Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву.— (22} Заявлено 05.04.74 (21} 2346554/18-24 с присоединением заявки №(23) Приоритет(43) Опубликовано 25.12.785юллетень № 47 (45} Дата опубликования описания 28.12.78.

Союз Советских

Социалистических

Республик

»» 639623 (51} М. Кл.

G 11 С 29/00

Государственный номнтет

Сонете Мнннстрав СССР пе делаи нзоеретеннй н отнрытнй (53) УДК 681.327..6 (088.8) В. В. Боднарчук, И. И, Гаенко, А. В. Городний, B. И. Корнейчук, А. С. Покаржевский, В. В, Ткаченко и Я. И. Торошанко (?2) Авторы изобретения

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (Тт } Заявитель (54) ЗАПОМИНАКЧЦЕЕ УСТРОЙСТВО

Изобретение относится к вычислитель ной технике и предназначено, в частности, для электронной цифровой вычислительной системы, выполненной на функциональных узлах с большой степенью интеграции.

Известно запоминаюшее устройство с 5 обнаружением ошибок, которое содержит накопитель, блок адресных и разрядных цепей, блок местного управления, регистр слова и блок контроля, который состоит из схемы автономного управления, схемы lo обнаружения ошибок, дополнительного регистра слова и схемы передачи Я.

Работа запоминаюшего устройства основана на методе двукратного обраше ния к каждой ячейке с операцией поразрядного инвентирования считываемых кодов в те моменты, когда оно не загружено реализацией основной программы.

Недостатком этого запоминаюшего устройства является наличие дополнитель- 2О ного регистра для хранения слова, а также ограниченная возможность по обнаружению случайных ошибок.

Наиболее близким техническим реше« нием к изобретению является устройство для хранения информации, содержашее накопитель, информационные выходы которого соединены с информационными выходами регистра слова, а контрольные выходы пос леднего подключены к блоку сравнения контрольных разрядов, и входные информационные шрны(2 . В известном запоминаюшем устройстве контрольные биты выбираются так, чтобы они не только индицировалн число двоичных "1" в передаваемой информационной ходовой комбинации, но и делали число двоичными 1 в полной кодовой комбинации нечетным (или четным) .

Недостатком известного устройства является недостаточная обнаруживаюшая способность (не всегда будет обнаружено четное число ошибок).

Бель изобретения -создание эапоминаюшего устройства с обнаружением ошибок, позволяюшего более эффективно обнаруживать большее число четных ошибок, 639023 вызванных отказами накопителя и разрядными цепями, Это достигается тем, что в устройство введены сумматоры по модулю два и элементы ИЛИ, первые входы которых соединены с входными информационными шинами, вторые входы — с выходами сумматоров по модулю два и входами блока сравне ния контрольных разрядов, а выходы подключены ко входам регистра слова, вы- 10 ходы которого соединены со входами сумматоров по модулю два.

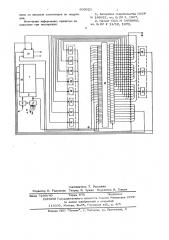

На чертеже дана структурная схема запоминающего устройства.

Оно содержит адресный накопитель (Н) 1, к которому подключен через адресные пепи (АЦ) 2 блок 3 адресных цепей (EAll) с информационным входом (Л) 4 и блок 5 местного управления (БМУ) со входами 6 "начало операции (HO) и вы- 20 ходом 7 "конец операции (КО), 8 "запись" (3), 9 чтение" (Ч) . Кроме этого, накопитель 1 через разрядные цепи (Pu)

10 соединен с регистром 11 слова (РС), который связан с сумматорами notnodgg4}

12 и с сумматорами notnod (X2) 13.

Выходы регистра 11 подключены к шине

14 "выход информационного слова", а входы - к элементам ИЛИ 15„на который через шину 16 вход информацион- 30 ного слова подается информация. В регистре слова 11 есть контрольные разряды групповой четности (КРГЧ) и контрольные разряды веточкой четности (КРВЧ). Выходы КРВЧ,КРГЧ 2 1 12 35 и Х,2 13 соединены с блоком 17 сравнения контрольных разрядов (БСКР).

Запоминающее устройство работает следующим образом. В режиме записи на вход 1 6 4о поступает информа ционное слово, которое проходит через элементы ИЛИ 15 и записывается в информационных разрядах ре Р гистра слова 11. Информационные разряды регистра условно разделены иа груп. 45 пы. Значения каждой из групп поступают на соответствующий сумматор по Mod

12, где формируются значения контрольных разрядов P групповой части четности (КРГЧ 1, КРГЧ2, КРГЧЗ) . Значения четнос- so ти для каждой из групп разрядов через элемен» ты ИЛИ 15 поступают в регистр 11.

Одновременно значения 4 — x разрядов каждой группы поступают на соответствующий 1-ый сумматор по юЫ 13. Значение бита четности для каждой g -ой ветви подается через элементы ИЛИ 15 в -й разряд {КРВЧj ) веточкой четности.

По сигналу с блока 5 местного управления осуществляется запись закодированного слова (кодового слова) через разрядные цепи 10 в ячейку 1 накопителя, номер которой задан кодом адреса на входе блока 3 адресных цепей.

При считывании информации образование всех контрольных разрядов групповой четности и контрольные разряды веточкой четности происходит аналогично, как и при записи, однако блок 5 управления блокирует запись этих разрядов с сумматоров 12 и 13 на регистр 11. Вновь образованные контрольные разряды групповой четности и веточной четности подаются в блок 17 сравнения, где осуществляется сравнение образованных контрольных разрядов групповой четности и веточной четности с первоначальными значениями, которые были записаны в соответствующих разрядах регистра 11 при чтении иэ накопителя 1. При несовпадении считанных и вновь образованных контрольных разрядов групповой и веточной четности блок 17 выдает сигнал "ошибка". Если не совпадают Р-контрольных разрядов веточной четности и один Д -й разряд групповой четности, то эта ситуация индицируется блоком 17 как пачка ошибок в d.-й группе разрядов, длина которых р.

Таким образом, предложенное устройство позволяет обнаружить все одиночные ошибки, двойные, тройные и т.д.

При семи информационных разрядах в группе и 3-х информационных группах одиночные двойные и тройные ошибки обнаруь живаются с вероятностью 1007, а четырехкратные — с вероятностью 99,07%.

Формула изобретения

Запоминающее устройство, содержащее накопитель, информационные выходы которого соединены с информа ционными выходами регистра слова,а контрольные выходы последнего подключены к блоку сравнения контрольных разрядов, и входные информационныешины,отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит сумматоры по модулю два и элементы ИЛИ, первые входы которых соединены с входными информационными шинами, вторые axoltbtc выходами сумматоров по модулю два и входами блока сравнения контрольных разрядов, а выходы подключены ко входам регистра слова, выходы которого соедииены со входами сумматоров по модулю два °

Источники информации, принятые во внимание при экспертизе:

639023

1. Авторское свидетельство СССР

% 189621, кл. Cj 06 F, 1967.

2. Патент США No 3458860, кл. Я 06 F 11/10, 1970.

Составитель Т, Мамджян

Редактор Н. Разумова Техред Э, Чужик Корректор И. Гоксич

Заказ 7290/40 Тираж 675 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открьггий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4