Адаптивное вычислительное устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Соииалистичесиих

Республик

ОГЗИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i! 64030! (б1) Дополнительное к авт. свид-ву (2?) Заявлено 04.08.76 (21) 2393444/18-24 с присоединением заявки ¹â€” (23) Приоритет (43) Опубликовано 30.12.78. Бюллетень № 48 (45) Дата опубликования описания 30.12.78 (51) М Кл з

G 06F 15/00

Государственный комитет (53) УДК 681.327 (088.8) по делам изобретений и открытий (72) Автор изобретения (71) Заявитель

В. А. Богатырев

Особое конструкторское бюро технической кибернетики

Ленинградского ордена Ленина политехнического института им.М. И. Калинина (54) АДАПТИВНОЕ ВЪ|ЧИСЛИТЕЛЬНОЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике и, в частности, к адаптивным вычислительным устройствам, состоящим из многофункциональных элементов, в которых при появлении отказов автоматически производится перестройка структуры с целью восстановления правильного функционирования устройства. Оно может быть применено в адаптивных цифровых вычислительных машинах, имеющих высокую жи- 10 вучесть, при ограниченной надежности элементов.

Известно адаптивное вычислительное устройство (1), содержащее функционально устойчивую сеть на многофункциональных по- 15 роговых элементах, узел регулировки, схемы сравнения, регистр, и логические схемы.

Недостатком известного является возможность выполнения только логических функций и значительной временной избыточности.

Известно адаптивное вычислительное устройство, содержащее многофункциональное логическое устройство, анализатор, селектор операций и вспомогательное оборудование (2).

Недостатком известного является функциональная ограниченность в выполнении только логических функций, выполняемых многофункциональным логическим .стройством.

Наиболее близким техническим решением к данному изобретению является адаптивное вычислительное устройство (3), содержащее многофункцнональныс мотнули, блок контроля, элементы И, И,1ТИ вЂ” НЕ, НЕ, коммутаторы, кольцевые регистры, генератор тактовых импульсов.

Известное устройство обладает недостатком, заключающимся в с. о функциональной ограниченности параллельным выполнением только независимых между собой функций, возложенных на модули. В нем невозможна организация как последовательного, так и параллельно последовательного процесса вычисления функций в случае их зависимости, т. е. когда результат вычисления некоторых нз них является входным воздействием для круглых функций. Кроме того, надежность известного адаптивного вычислительного устройства ограничена возможностью восстановления функционирования возложением функции отказавшего модуля на соседний модуль.

Целью изобретения является расширение функциональных возможностей за счет увеличения числа реализуемых функций н повышения надежности устройства.

640301

С.оставитель В. Богатырев

Техред А. Камышникова

Редактор Ю. Челюканов

Корректоры: Л. Корогод и Л. Брахнина

Заказ 2474/15 11зд. № 782 Тираж 799 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

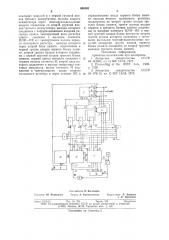

Типография, пр. Сапунова, 2 опальных модулей и с первой группой входов третьего коммутатора, выходы второго коммутатора через многофункциональные модули соединены со второй группой входов третьего коммутатора, выходы которого 5 соединены с информационными входами регистра сдвига, тактирующий вход регистра сдвига соединен с выходом элемента

ИЛИ вЂ” HE и с тактирующим входом первого кольцевого регистра, выходы которого 10 через второй блок памяти подключены к первой группе входов первого блока памяти, вторая группа входов которого соединена с первой группой входов третьего блока памяти, первый выход которого соединен с 15 первым входом элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, выход элемента И подключен к тактирующему входу второго кольцевого регистра и через элемент НЕ к 20 управляющему входу первого блока памяти, выходы второго кольцевого регистра подключены ко второй группе входов третьего блока памяти, третьи группы входов первого и третьего блоков памяти соединены со входами элемента ИЛИ вЂ” НЕ и первой группой входов блока контроля, вторая группа входов которого соединена с тестовыми выходами многофункциональных модулей, четвертая группа входов первого блока памяти соединена со второй группой выходов третьего блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Кв 443382, кл. G 06F 15/18, 1972.

2. Proceeding of the IEEE 1п!е, 1969, р. 1320.

3. Авторское свидетельство СССР

М 479115, кл. G 06F 15/18, 1973.