Логическое устройство для управления блоками печати

Иллюстрации

Показать всеРеферат

(»)640336

ОПИСАН И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЙЬСТВУ

Союз Советских

Социалистических

Республик

-1 (51) М, Кл.

G 06К 13/077 (61) Дополнительное к авт. свпд-ву (22) Заявлено 10.07.73 (21) 1941438/18-24 (23) Приоритет — (32) 11.07.72 (31) WPG Об116432б>

СССР ло делам изобретений и открытий (43) Опубликовано 30.12.78. Бюллетень ¹ 48 (45) Дата опубликования описания 30.12.78 (53) УДК 621-327 (088.8) (72) Автор изобретения

Иностранец

Франк Эрмер (ГДР) Иностранное предприятие

«ФЕБ Комбинат Цетроник» (ГДР) (71) Заявитель (54) ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

БЛОКАМИ ПЕЧАТИ

Изобретение относится к схемам для управления местоположением печатного агрегата, в частности механизма последовательной печати, причем каждому месту печати приписан адрес в двоичной, предпочтительно дуальной форме.

Известны схемы для управления местоположением, работающие по принципу непрерывного сравнения запрограммированного адреса и какого-то мгновенного местоположения подвижного узла, причем они выдают сигнал «Меньше», «Больше» или

«Равен», по которому и начинается соответствующая фаза движения. Сигнал приостановки такой схемой выдается только тогда, 15 когда адреса уже соответствуют.

Известны схемы управления печатающими устройствами, действие которых основано на определении различия фактического и заданного положений печатного устройства при помощи комбинаций элементарных логических схем (1).

Однако известные схемы не выполняют многих задач, необходимых при управлении печатью. К ним относятся определение направления и скорости перемещения печатающего устройства, момента остановки с определением необходимого тормозного пути ит.д.

Наиболее близкое к изобретению техническое решение — логическое устройство для управления блоками печати, содержащее разрядные сумматоры, один выход каждого из которых подключен к одному из входов последующего сумматора, другие входы которых подключены к входным каналам, один из выходов последнего разрядного сумматора соединен с одним из входов первого разрядного сумматора (2).

Недостатком этого устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в предлагаемом устройстве установлены элементы памяти, НЕ, ИЛИ и И, причем другие выходы первого и второго разрядных сумматоров соединены с первым элементом И, а выходы остальных разрядных сумматоров — с входами второго элемента

И и элемента ИЛИ. Выходы первого и второго элементов И подключены к входам третьего элемента И, а выходы второго элемента И через элемент HE и элемент ИЛИ непосредственно соединены с четвертым элементом И, связанного выходом с первым входом первого элемента памяти и входом второго элемента НЕ, выход кото640336

65 р1но н Tlc ðâüø ннвсрсный гыход элем!ига

l j,3I ll ПОД! ЛЮЧЕНЫ и В "O !TOÌ ПатОГО ЗЛЕ1,!сита И, соединенного с первым входом ьторого элемента памяти, второй вход которого соединен с выходом третьего элемента И и вторым входом первого элемента памяти, второй инверсный выход которого и выход второго элемента НЕ подключены к входам шсстого элемента И. Выходы третьего и шестого элементов И, второй инверсный выход первого элемента памяти, выход второго элемента памяти и выход последнего разрядного сумматора соединены с выходными к!!валами устройства.

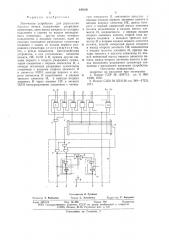

I I3 1сртс1ке показана функциональна!1 схема устройства.

Логическое устройство для управления блоками печати содержит разрядные сумматоры 11 — 1 „один из выходов каждого нз которых подкл1очен к одному из входов последнего, а выход последнего сумматора

1„, подключен к входу первого сумматора

1l. Разрядные сумматоры представляют собой г. совокупности счетно-решающую схему, и входам сумматоров которой подклюЧЕНЫ ВХОДНЫЕ КаНаЛЫ 21 — 2m И 31 — 3m ПО которым соответственно поступают сигналы мгновенного местоположения блоков печати и задаваемого адреса.

В устройство входят также логические элементы И 4 — 9, элемент ИЛИ 10, элементы HE 11 и 12 и элементы 13 и 14 памяти.

Одни из выходов сумматоров 11 и 1 подключены к элементу И 5, а выходы других сумматоров 1> — lm — к входам элемента И

4 и ИЛИ 10. Выходы элементов 4, 5 и 10 и сумматора 1, соединены с блоком 15 оценки сигналов, состоящим из элементов б — 9, 11, 12.

Первый элемент 13 памяти служит для управления табуляцией, второй элемент 14 памяти — для управления шаговым движением. К входу элемента 13 памяти через элементы И б и 7 и элемент НЕ 11 поступают сигналы от элементов И 4 и 5 и ИЛИ

10. К входам элемента 14 памяти подаются сигналы с элементов И б и 8, который обрабатывает сигналы с выходов элементов

13, 7 и 12. С выхода элемента И 9, подключенного к выходам элементов 13 и 12, снимается сигнал об окончании табуляции и начале процесса торможения. Сигнал равенства адресов с выхода элемента б используется для стирания памяти в элементе 13.

Выход сумматора 1 без изменения используется для формирования сигнала табуляции или шагового движения.

При наличии информации о мгновенном положении блоков печати (входы 21 — 2 ) и задаваемом адресе (входы 31 — 3 ) в сумматорах осуществляется суммирование. Так как один из адресов подается дополнительным кодом, то при равенстве адресов на

55 всех выходах резульгатон !н!т чшотся логические единицы. В эгом случае эл=менты 4, 5 и б вырабатывают единицы на выходах, из которых выход элемента б является сигналом равенства адресов «Адреса равны».

Благодаря тому, что этот сигнал равенства подастся так>кс на элсмснты 13 и 14, oil предотвращает появление на выходах элементов памяти сигналов, и блок печати нс движется. Если мгновенное положение и задаваемый адрес отличаются на одну, две или три единицы младших разрядов, то выходы сумматоров 11 — 1„, н зависимости от направления рассогласованы, либо всс нулевые, либо все сдшшчные, так что выходные сигналы элементов 4 и 10 одинаковы. При этом выходной сигнал элемента 7 также всегда нулевой. Через элементы 12, 13 и 8 элемент 14 становится в режим

«П одхв а та».

В процессе последующего шагового движения, направление которого определяется значением сигнала с сумматора 1,„, с каждым шагом изменяется значение мгновенного положения и так до совпадения с задаваемым адресом. К этому моменту выдается сигнал равенства адресов «Адреса равны» и снимает «подхват» элемента памяти 14, нужное положение блока печати достигнуто.

Если разница между мгновенным положением и задаваемым адресом превышает три единицы младшего разряда, то по меньшей мере один из выходов сумматора

1> — 1 имеет нулевой потенциал или по меньшей мере один — единичный потенциал, если несколько выходов сумматоров 1 — Im имеют единичный или нулевой потенциал.

На выходе элемента 4 при этом оказывается нуль, на выходе элемента 10 — единица, так что элементы 7 выдают единицу, которая взводит элемент 13 памяти.

Блок печати начинает быструю табуляцию, направление которой определяется значением сигнала с сумматора lmm. Табуляция продолжается до тех пор, пока мгновенное положение и задаваемый адрес не станут отличаться только на три единицы младшего разряда. При этом пропадает единица на выходе элемента 7 и оба входа элемента И 9 получают по единице, так что на его выходе появляется сигнал остановки табуляции, т. е. привод табуляции отключен, и вместо этого начинается процесс торможения, причем остальные три шага до согласования адресов будут пройдены в шаговом режиме. В конце процесса вновь появляется сигнал «Адреса равны», и происходит обнуление элементов памяти 13 и 14.

При этом устройство готово к следующему этапу управления местоположением.

Технико-экономический эффект изобретения заключается в создании быстродействующих блоков печати.

64() 336

Формула изобрегсни,<

Составитель О. Гудкова

Техред С. Антипенко

Корректор P. Беркович

Редактор Т. Рыбалова

Заказ 2357/12 Изд. № 808 Тираж 799 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Логическое устройство для управления блока м и печати, содержащее разрядныс сумматоры, один выход каждого из которых подкл1очен к одному из входов последующего сумматора, другис входы которых подключены к входным капалам, один из выходов последнего разрядного сумматора соединен с одним из входов первого разрядного сумматора, отличающееся тем, что, с целью повышения быстродействия устройства, в нем установлены элементы памяти, НЕ, ИЛИ и И, причем другие выходы первого и второго разрядных сумматоров соединены с первым элементом И, а выходы остальных разрядных сумматоров соединены с входами второго элемента И и элемента ИЛИ, выходы первого и второго элементов И подключены к входам третьего элемента И, а выходы второго элемента И через элемент НЕ и элемент

ИЛИ непосредственно соединены с четвертым элементом I l. связанного выходом с первым входом первого элемента памяти и входом второго элемента НЕ, выход которого и первый инверсный выход элемента

5 памяти подключены к входам пятого элемента И, соединенного с первым входом второго элемента памяти, второй вход которого соединен с выходом третьего элсмента И и вторым входом первого элемента

10 памяти, второй инверсный выход которого и выход второго элемента НЕ подключены к входам шестого элемента И, причем выходы третьего и шестого элементов И, второй инверсный выход первого элемента па15 мяти, выход второго элемента памяти и выход последнего разрядного сумматора соединены с выходными каналами устройства.

Источники информации, принятыс во внимание при экспертизе

2о 1. Патент ГДР № 1294713, кл. G 06К

13/00, 1970.

2. Патент CIIIA № 3512138, кл. 340 — 172.5, 1971.