Устройство для цикловой синхронизации

Иллюстрации

Показать всеРеферат

и

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 21.09.76 (21) 2405244, 18-09 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 30.12.78. Бюллстеш. ¹ 48 (45) Дата опубликования описания 30.12.78 (51) М. 1(л.оH 04L 7, 08

Государственный комитет

СССР аа делам изобретений и открытий (53) У 1К 621 394,662 (088.8) (72) Авторы изобретения

Ф. Г. Гордон и М. Я. Вертлиб (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к технике передачи данных и может использоваться для выделения псевдослучайного синхросигнала с обнаружением и исправлением ошибок при фазировании аппаратуры передачи данных с помощью фазового пуска.

Известно устройство для цикловой синхронизации, содержащее на информационном входе первый сумматор по модулю два, к другому входу которого подключен выход регистра сдвига с обратной связью и один из входов второго сумматора по модулю два, выход которого через управляемый счетчик временного интервала подключен к одному из входов дешифратора, к другим входам которого подключены выходы соответствующих разрядов регистра сдвига с обратной связью (1).

Однако это устройство характеризуется невозможностью исправления пакета ошибок и длительным временем вхождения в синхронизм.

Целью изобретения является сокращение времени вхождения в синхронизм.

Для этого в устройство для цикловой синхронизации, содержащее на информационном входе первый сумматор по модулю два, к другому входу которого подключен выход регистра сдвига с обратной связью и один из входов второго сумматора по модулю два, выход которого через управляемый счетчик временного интервала подключен к одному из входов дешифратора, к другим входам которого подключены выходы соот5 ветствующих разрядов регистра сдвига с обратной связью, введены дополнительный сумматор по модулю два, ключ, элемент И, триггер интервала, триггер фазирования и делитель частоты, при этом информацион10 ный вход первого сумматора по модулю два через дополнительный сумматор по модулю два подключен к входу регистра сдвига с обратной связью и к другому входу второго сумматора по модулю два, а выход

15 счетчика временного интервала подключен к единичному входу триггера фазирования, выход которого подключен к другому входу дополнительного сумматора по модулю два через ключ, другой вход которого соединен

2р .с выходом первого сумматора по модулю два и с первым входом элемента И, к другому входу которого подключен выход триггера интервала, а выход элемента И подключен к соответствующим входам триггера интервала и триггера фазированпя, к управляющим входам которых подкл.очены соответствующие выходы делителя частоты, к входу которого подключен выход триггера интервала, причем на выход «установка

30 нуля» триггера фазированпя и на вход «ус0439

64

3 тановка единицы» триггера интервала и на соответствующии вход делителя .астогы подан сигнал сброса.

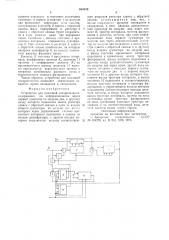

Йа чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для цикловой синхронизации содержит на информационном входе первый сумматор 1 по модулю два, к другому входу которого подключен выход регистра 2 сдвига с обратной связью и один из входов второго сум»aropa 3 по модулю два, вы од которого через управляемыи счетчик временного интервала подключен к одному из входов дешифратора 5, к другим входам которого подключены выходы соответствующих разрядов регистра 2 сдвига с обратной связью, дополнительный сумматор b no модулю два, ключ 7, элемент ll 8, триггер

9 интервала, триггер 10 фазирования и делитель il частоты, при этом информационный вход первого сумматора 1 по модулю два через дополнительный сумматор б по модулю два подключен к входу регистра 2 сдвига с обратной связью и к другому входу второго сумматора 3 по модулю два, а выход счетчика 4 временного интервала подключен к единичному входу триггера l0 фазирования, выход которого подключен к другoivl) входу дополнительного сумматора

Ь по модулю два через ключ (, другой вход которого соединен с выходом первого сумматора 1 по модулю два и с первым входом элемента li Ь, к другому входу которого подключен выход триггера 9 интервала, а выход элемента И 8 подключен к соответствующим входам триггера 9 интервала и триггера 10 фазирования, к управляющим входам которых подключены соответствующие выходы делителя ll частоты, к входу которого подключен выход триггера 9 интервала, причем на вход «установка нуля» триггера 10 фазирования, на вход

«установка единицы» триггера 9 интервала и на соответствующий вход делителя 11 частоты подан сигнал сброса.

Устройство работает следующим obpaзом.

При включении устройства сигналом сброса триггер 9 интервала устанавливается в состояние «установка единицы», а триггер

10 фазирования, счетчик 4 временного интервала и делитель 11 частоты — в состояние «установка нуля». При этом элемент

И 8 и ключ 7 закрыты и входная информация поступает через первый сумматор 1 по модулю два в регистр 2 сдвига с обратной связью без коррекции ошибок. Блокирующий вход делителя 11 частоты открыт высоким уровнем, поступающим с выхода триггера 9 интервала, и с входа 12 в делитель

11 частоты поступает тактовая частота.

Через интервал времени, определяемый коэффициентом деления делителя 11 частоты, на его выходе появляется сигнал, переводящий триггер 9 интервала в состояние «уста5

4!)

55 оо

4 новка нуля». При этом на блокирующем входе делителя 11 частоты появляется низкий уровень, закрывающий вход де. ителя

11 частоты.

Коэффициент деления К делителя )1 частоты выбирается, исходя из условий обеспечения коррекций гакетов ошибок и ви,1а псевдослучайной последовательности, т. е. если полином имеет вид Хо — — „—,Ë„, то

К )п, где и — число разрядов регистра 2 с обратной связью, образующего псевдослучайную последовательность.

При появлении на входе устройства ошибок первый же импульс ошибки появляется на выходе дополнительного сумматора 6 по модулю два, проходит через открытый элемент И 8 и переводит триггер 9 интервала и триггер 10 фазирования в состояние «установка единицы», При этом высокий уровень с выхода трш.гера 10 фазирования открывает ключ 7 и импульс с выхода дополнительного сумматора 6 по модулю два через открытый ключ

7 поступает на второй вход первого сумматора 1 по модулю два, на первый вход которого в это время поступил импульс ошибки. На выходе первого сумматора 1 по модулю два при этом происходит исправление ошибки и на втором сумматоре 3 по модулю два происходит сравнение записанной в регистре 2 сдвига с обратной связью исправленной входной информации. Если до этого времени в регистр 2 сдвига с обратной связью была записана информация без ошибок, то на выходе второго сумматора 3 по модулю два импульсы ошибок будут отсутствовать и счетчик 4 временного интервала будет считать импульсы тактовой частоты. Исправление ошибок в первом сумматоре 1 по модулю два будет происходить до момента времени, пока на промежуточном выходе делителя 11 частоты не появится импульс, который переводит триггер 9 интервала в состояние «установка нуля», при этом элемент И 8 закроется.

Длина пакета ошибок, который может исправить устройство, не может быть больше, чем К тактов, где К вЂ” разряд регистра, с которого снимается обратная связь, т. е. длина пакета ошибок определяется образующим полиномом Хо — — Х -+ Х„, по которому была образована псевдослучайная последовательность.

В случае, если длина пакета превышает

К тактов, то исправления ошибок не происходит, на выходе второго сумматора 3 по модулю два появляется импульс ошибки, сбрасывающий счетчик 4 временного интервала. При этом схема начинает работать сначала. Если в течение N тактов,,где N— емкость счетчика 4 временного интервала, на выходе второго сумматора 3 по модулю два не было ошибок, то на выходе счетчика

4 временного интервала появляется сигнал

его заполнения. При этом триггер 10 фази640439 рования переходит в состояние «установка единицы», в первом сумматоре 1 по модулю два происходит коррекция в сх ошибок, поступающих в регистр 2 сдвига с обратной связью. Фаза информации в регистре 2 сдвига с обратной связью будет сохраняться в этом режиме даже при перерывах связи. Сигналом с выхода счетчика 4 временного интервала открывается дешифратор 5. 11ри появлении в регистре 2 сдвига с обратной связью комбинации, на которую настроен дешифратор 5, на выходс появляется импульс фазового пуска.

Емкость IV счетчика 4 временного интервала, коэффициент деления К делителя 11 частоты и коэффициент деления К-, на промежуточном выходе делителя 11 частоты определяется вероятностями приема и неприема комбинации фазового пуска и вероятностями ложного фазирования. 20

Таким образом, устройство для цикловой синхронизации позволяет значительно сократить время вхождения в сипхропизм.

Формула изобретения

Устройство для цикловой синхронизации, содержащее на информационном входе первый сумматор по модулю два, к другому входу которого подключен выход регистра сдвига с обратной связью и один из входов 30 второго сумматора по модулю два, вь.ход которого через управляемый счетчик временного интервала подключен к одному из входов дешифратора, к другим входам которого подключены выходы соответствую- 35

6 щих разрядов регистра сдвига с обратной связью, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, в него введены дополнительный сумматор по модулю два, ключ, элемент И, триггер интервала, триггер фазирования и делитель частоты, при этом информационный вход первого сумматора по модулю два через дополнительный сумматор по модулю два подключен к входу pcI Iiстра сдвига с обратной связью и к другому входу второго сумматора по модулю два, а выход счетчика временного интервала подключсн к единичному входу триггера фазирования, выход которого подключен к другому входу дополнительного сумматора по модулю два через ключ, друго" вход которого соединен с выходом первого сумматора по модулю два и с первым входом элемента И, к другому входу которого подключен выход триггера интервала, а выход элемента И подключен к соответствующим входам триггера интервала и триггера фазирования, к управляющим входам которых подключены соответствующие выходы делителя частоты, к входу которого подключен выход триггера интервала, причем на вход

«установка нуля» триггера фазирования, на вход «установка единицы» триггера интервала и на соответствующий вход делителя частоты подан сигнал сброса.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 454705, кл. Н 041 7/08, 1973.