Импульсный стабилизатор постоянного напряжения с защитой от перегрузок по току

Иллюстрации

Показать всеРеферат

Союз Советских

Соцмалистмчвскми

Республик

< 641425

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЙТВЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено17.10.77 (21) 2534193/24-07 с присоединением заявки № (23) Приоритет ,Опубликовано 05.01.7ЬБюллетеиь № 1

Дата опубликования описания 10.01,79 (51) М. Кл.

G 05 F l/58

Гасударственный кемитет

СССР пе дезам изобретений и открьпий (53) УДК В21.316. .722.1 (088 8) (72) Авторы изобретения

Б. Г. Смирнов, B. M. Семииин и Е Е. Шарвиеоров;;, 1

1 (71) Заявитель (54) ИМПУЛЬСНЫИ СТАБИЛИЗАТОР ПОСТОЯННОГО

НАПРЯЖЕНИЯ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗОК ПО Т(ЖУ

Изобретение относится к области алек«. трорадиотехннки, к источникам питания и может быть использовано в системах питания устройств автоматики и вычислительной техники.

Известны импульсные стабилизаторы постоянного напряжения, содержащие регулирующий транзистор, интегрирующий фильтр, блок управления, блок сравнени (11 .

so

Наиболее близким к изобретению является импульсный стабилизатор постоянного напряжения с зашитой от перегрузок по току, содержащий включенные последовательно в выходную шину регулирующий транзистор и дроссель интегрируюmего фильтра, схему сравнения и ограничения напряжения, блок управления, выходом подсоединенный к базе регулируюmего транзистора (2)

Недостатком импульсного стабилизатора постоянного напряжения с зашитой от перегрузок по току является его относительная сложность.

Целью изобретениа авлаетса унроше» ние схемы стабилизатора.

Поставленная цель достигаетса тем, что в импульсном стабилизаторе постояв ного напряжения с заппетой от перегрузок по току, содержащем включенные после довательно в выходную янину регулирую ший транзистор и дроссель йитегриуувmего фильтра, схему cp@sseass и or чения напряжения, блок управленим, вы- ходом подсоединенный к базе регулирую щего транзистора, схема сравиеииа и оеъраничения напряжения выполнена в виде подключенных параллельно входным выво дам соединеию х последовательно атаби литрона с первым резистором и запоминающего конденсатора со вторым резистором, а также транзистора сравнеииа, фиксирующего диода и элемента индикапии, причем точка соединения стабилитрона с резистором подклкнеиа к эмиттеру транзистора сравнения, база которого подключена к точке соединения запоминающего конденсатора и второго резистора и через фиксирующий диод соединена с кол»

641425 лектором регулирующего транзистора, а коллектор транзистора сравнения через элемент индикации подсоединен к общей шине, причем точка соединения коллектора транзистора сравнения с элементом индикации подключена ко входу блока управления.

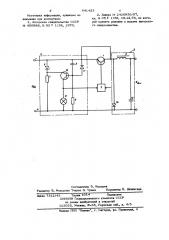

На чертеже представлена принципиаль ная электрическая схема импульсного стабилизатора постоянного напряжения с за- 10 шитой от перегрузок по току.

Стабилизатор содержит регулирующий{ транзистор 1,дроссель 2 интегрирующего фильтра 3, схему сравнения и огра« ничения напряжения 4, блок управления

5 стабилитрон 6, первый резистор 7, зало мкнающий конденсатор 8 в горой ре зистор 9, транзистор сравнения 10, фиксирующий д{{ог 1 1„элемент индикации

12, бгонде{-..сатор 13 и демпфируюший диод 14.

")5

Импульсный стабилизатор постоянного

{ напряженби с эащигой от перегоузок цо току, содержапц{{й включенные носледовательно и выходную шину регулирующий транзистор и дроссель иитегрирукниего фильтра, схему сравнения и ограничения напряжении, блок управлекия, выходом

5 подсоединенный к базе регулирующего транзистора, отличающийся тем, что, с целью упрощения схемы стабилизатора, схема сравнения ы ограничения напряжения выполнена в виде подключенных параллельно входным выводам соединенных последовательно стабилитро на с первым резистором и запоминающего конденсатора со вторым резистором, а также транзистора сравнения, фиксирую45 „. ио та инд <ац и чем точка соединения стабилитрона с резистором подключена к эмиттеру тран-. зистора сравнения, база которого подключена к точке соединения запоминаю5О щего конденсатора и второго резистора и через фиксирующий диод соединена с коллектором регулирующего транзистора, а коллектор транзистора сравнения через элемент индикации подсоединен к обшей

55 шине, причем точка соединения коллектора транзистора сравнения с элементом. индикации подключена ко входу блок& . управления.

Стабилизатор работает следующим образом.

B резуньмте включения источ11ика входного напряг выпь HQ выходе клбочевО го транзпс."гора 1 фсрмпрубогся импульсы, с амщни;удо."., близкой к ржодпому напря-, жению. Управление к. по гевым тоанзистооом 1 и a{" ."i:., {и{вся блоком ) правления

5 Ца;ъ)р,ч.-.--т:.;.-.,:- ъ тбф1(и ющего диода 14 дросселя 2 и конденсатора 13 -" обычное дл{{ и;{б 7 ;;.l пых стабнлизаторове

Цо „;; ббус ги;.,бьбх збгачеппях тока на| рузки стабплизетооа ключевой транзистор { нРхоб{и i б.::{ В ббасыбпеб{бги при подаче упраилябо{ббе.: о -.чгнала на его базу с блока управления 5., В этом слу чае падение напряжения на ыпочевом транзисторе 1 (напряжеиие эмиттер-коллЯ тор) не превышает заданного значения.

В случае превышения тока нагрузки падение напряжения на открьггом ключе вом транзисторе 1 возрастает.

Вьбделение укаэанного падения напряжения осуществляется с помощью фиксирующего диода 11 и зарядного резистора 9 на запоминающем конденсаторе

8 следукицим:образом.

Заряд запоминающего конденсатора 8 происходит через зарядный:.резистор 8 до напряжения, равного минимальному падению напряжения — на ключевом трап« зисторе 1, а при дальнейшем его увеличении фиксирующий диод 11 отпираеч ся и, гаким образом напряжение На запоминающем конденсаторе 8 становится равным падению напряжения на открытом ключевом транзисторе 1. Выделенное на» пряжение с запоминающего конденсатора

8 поступает ча вход транзистора сравнения 10, на другой вход которого подается опорное напряжение стабилитрона

6, равное допустимому падению напряжения иа открытом ключевом транзисторе 1.

Таким образом, на выходе транзистора сравнения 10 при допустимых значениях тока нагрузки стабилизатора сигнал отсутствует, а при превышении его появляегся и, воздействуя на блок управления 5, вызывает эапирание ключевого транзистора 1 и обеспечивает защиту стабилизатора err перегрузок по току.

Процесс запирания ключевого транзистора 1 эа счет положительной обратной связи протекает лавинообразно. Йля возобновления работы после срабатывания зашиты необходимо отключить и снова включить источник входного напряжения.

Ф ор мула изобретения

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

14 400888, G 05 F 1/58, 1970.

2. Заявка % 2426856/07, кл. G 05 С 1/58, 16.12.76, по которой принято решение о выдаче авторского свидет ельства.

Составитель B. Косырев

Редактор В. Фельдман Техред Э. Чужик Корректор E. Йнчинская.

Заказ 7512/43 Тираж 101 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий .

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4