Устройство для управления операциями ввода-вывода данных

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублмк цц 641435 (61) Дополнительное к авт. свид-ву (22) Заявлено 1 2.08.76 (21) 2396944/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.01.79.Бюллетень №. 1

Дата опубликования описания 07.01.79 (51) м. Кл.

С06 F 3/04

ГасудерственныИ нсинтет

СССР по делам нэебретеннй н QTlfpblEHII (53) УДК 681.327..2(088,8) +

М. А. Боярченков, А. И. Березенко, В. Я. Хонтарер Л. H. Корягин, Г. А. Крылов, lI. M. Ленгник, С. А. Шац Ь. -И .-,Фельлман у

А

Ф

Институт электронных управляющи -цашжС,:. -,, (72) Авторы изобретения (71) Заявитель

I (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАЦИЯМИ

ВВОДА-ВЫВОДА ДАННЫХ

Изобретение относится к вычислительной технике.

Известно устройство для управления вводом-выводом данных, предназначенное для различных внешних устройств (1(Оно содержит адресный регистр, регистр операций, регистр пуска, счетчик импульсов, выходной буферный регистр, схему сравнения, дешифратор состояния счетчика, схему блокировки и набор элементов И.

С помощью адаптера осуществляется на. стройка устройства на работу с внешним устройством определенного типа.

К недостаткам такого устройства относятся: громоздкость схемных решений, низкий уровень унификации узлов, высокая стоимость аппаратной реализации, сложность массоаого производства и отладки, а также невозможность использования логических решений на больших интегральных схемах (БИС) из-зв нецелесообразности разработки узкоспециализированных БИС для тиражирования в ограниченных масштабах, кроме того, непосредственный перевод схем аппаратно реализованного устройства на БИС в ряде сл чаев может оказаться технологически неосуществимым либо черезмерно дорогим и сложным в связи с тем, что использование БИС накладывает определенные ограничения на схемотехнические решения.

Следует отметить, что имеется воэмож5 ность осуществления логического алгоритма и алгоритма обмена цо интерфейсным связям с помощью аппаратуры, реализованной на программируемых БИС. Специфика логического алгоритма. и алгоритмов обмена по интерфейсным связям в этом слу1о чае определяется программой, хранящейся в памяти программ устройства.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство, которое содержит процессор, блок памяти и блок сопряжения, 15 соединенные двусторонними информационными связями, управляющий выход процессора соединен с управляющими входами блока памяти и блока сопряжения, входы и выходы которого подключены соответственно ко входам и выхода н устройства (2(.

К недостаткам этого устройства относится неэффективное использование быстродействия процессора.

Ч14ЗЬ

3 .Наименьшир пауза или сигнал не успеют окончиться или возникнуть между двумя сОседними МОментами ОпрОс3, Частота опроса ограничена тактовой частотой устройства, которая определяется исходя из бь(стродействия элементной базы устройства. Под тактовой частотой здесь подразумевается максимальная частота выполнения команд того уровня, ня котором производится программирование устройства.

Поскольку сигналы от периферийных устройств имею, кяк правило, переменный периОд, то частота опроса должна превышать фиксировянн /to частоту следОВяния Опрашиваемь|х импульсов больше,. чем в 2 раза.

Далее, при большом указанном Отноше- И нии усложни(отся программы устройства, так как необходимо обрабатывать большие последовательности результатов опросов сигналов с интерфейсных связей, что в свою очередь, приводит к увеличению необходимого объема памяти и уменьшает эффективное бь(стродействие. В рассматриваемом изВ8сТНоМ устройстве с программно-упр3вляемым обменом по интерфейсным связям внешних сиГналОВ, к которым подключены периферийные устройства с различными частотами Q6McH3 данными, oTcvTcTB (oT средства

25 синхронизации моментов исполнения команд с моментами появления внешних сигналов.

Следствием этого являются описанные выше недостатки., т. е, неэффективное использование быстродействия процессора и блока па- M мяти.

Целью изобретения является повышение быстродействия и Обеспечение универсальности применения для широкого класса внешних устройств и ЗИМ.

Поставленная цель достигается тем, что в устройство введен блок формирования тактовых сигналов, первый управляющий вход . кОтороГО соединен с управляющим ВыхОдОм процессора, второй управляющий вход блока формирования тактовых сигналов н уп- равляющий вход процессора соединены с управляющим входом устройства, Выход блока фОрмирований тактОвых сиГНЯЛОВ сОРдинен с так овым входом процессора.

Кроме того, блок формирования тактоBhIx сиГналов содержит регистр, схему ср38нения,. пересчетиый узел и импульсный генератор, выход которого соединен со счетным входом пересчетнОГО узла, Выходы которого и выходы регистра подключены соответственно ко входам схемы сравнения, вход регистра и первый вход пересчетного узла соединены с первым управляющим входом блока, второй вход иересчетного узла соединен со вторым управляющим входом блока, третий вход объединен с выходом . блока и подключен к выходу схемы срав55 ненни.

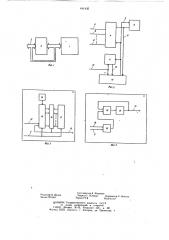

На фиг. 1 представлена обобщенная блоксхема устройства; на фиг. 2 показаны блоксхема устройства в соответствии с изобретением; Н3 фиг. 3 изображена схема блока формирования тактовых сип(ялов, выполненного в виде цифрового фязируемого генератора переменной частоты; на фнг. 4 изображена схема блока формирования тактовых сигналов, выполненного и виде фязируемого автогенератора реляксяционного типа.

Н3 фиГ. 1 — 4 приняты следуюгцие Обозначения: логический блок 1; блок 2 связи с ЗВМ и периферийными устройствами; связь 3 для обмена данными и управляющими сигналами с ЗВМ и периферийными устройствами; блок 4 сопряжения, связь 5 управляющих сигналов; связь 6 для обмена данными, управляющий вход 7 (для сигналов прерывания) процессора, связи 8 подключения блока 4; блок 9 памяти; процессор 10; блок 11 формирования тактовых сигналов; управляющая связь 12, связь 13 тактовых сигналов; пересчетный узел 14; импульсный генератор 15; схема сравнения 16; регистр 17; накопитель I8; пороговый элемент 19; узел 20 управления сбросом.

Устройство работает следующим образом.

При отсутствии команды от ЗВМ выполняется цикл ожидания. Команда ОТЗВМ вызывает прерывание этого цикла; соответствующий сигнал прерывания поступает иа входы прерывания процессора 10 по связи

12 и инициирует вьи(олиение процессором 10 соответствуощей программы, хранящейся в блоке 9. Синхронизация исполнения команд процессора с моментами ожидаемого появления внешнего сигналя производится в режиме.«фязировка». По сигналам от процессора, поступающим иа блок 11 формирования тактовых сигналов, производится задержка исполнения следующей команды. Зта задержка происходит за счет прекращения работы блока 11 формирования актовых сигналов до прихода вне(инего сигнала е определенной линии связи 12. При появлении этого сигнала блок 11 формирования тактовых сигналов начинает выдавать синхросигналы (синхросерии) для процессора 10 в фазе и с частотой внешнего сигнала до следующей команды управления блоком формирования тактовых сигналов 11 от процессора 10. По окончании отработки этого режима управление снова передается на цикл ожидания.

Блок I I формирования тактовых сигналов может быть выполнен в виде цифрового фазируемого генератора переменной часготы (см. фиг. 3) .

Блок 11 формирования тактовых сигналов, выполненный в виде цифрового фазируемого генератора, представляет собой делитель частоты импульсного генератора 15 с переменным коэффициентом деления, з ля64) 435 ваемым содержимым регистра 17. Он работает следующим образом: пересчетный узел 14 при отсутствии сигналов управления на первом управляющем входе блока по IM!fyJlbcB!)i с непрерыв»0 работак)щ)",.ГО 5 импульсного генератора 15 последовательно пе}теходит В сОстОяния От нячяльнОГО дО Конечного, последнее определяется кодом В регистре 17, устанавливаемым заранее. При совпадении кодов узла 14 и регистра 7 на выходе схемы сравнения 16 вырабатывается сигнал совпадения устанавливающий начальное состояние пересчетного узла 14, после чеГО ОписяниыЙ цикл счетя пОВторяется. Один цикл счета соответствует набору тактовых сигналов иа связи 1, 3 тактовых д сигналов„необходимому для Выполне)н)я одной команды процессора 10. В ре)киме (фазировкя», зада вяемом сООтветстВующими сигналами по связи 5, пересчетный узел 14 устанавливается в начальное состояние и счет прекращается до прихода соответствующего дополнительного сигнала по связи 12, после прихода которого начинается описаиныи Выше цикл счета.

Блок 1 1 формирования тактовых сигналов может бь.ть также выполнен в виде фазируемого автогеиератора релаксацио)иного

-ть)па, блок-схема которого приведена на фиг 4. Такой блок формирования тактовых сигналов содержит накопитель 18, выход которого связан со входом порогового элемента 19, выход которого связан со входом сброса накопителя 18 и с выходом блока.

Другой вход сброса накопителя 8 связан с выходом узла 20 упр;âë.åí.è.ÿ сбросом, Входы которогО сВязяны с rfepBbIM и BTopbi lf упоавля)()щи ми вх()»ам и блока

Блок формирования TQKTGBbix сигналов с этой структурой работает следующим 06Р330М.

При GTc)JTcòBèH сиГналОВ упрзВлсния ня перВОМ ВхОде накопительный элемент (напримеп, конденсатор или HHJ)yKTHBhocTb} 33- и) ряжяется дО тех пор) пока сиГиял ня ВыхОде накопителя 18 не достигнет уровня переключения порогового элемента 19, сигнал с выхода котсрого поступает иа вход сброса накопителя 18 и Вызывает разряд его накопительного элемента, после чего цикл заряд45 разряд, повто})я)ется H T. Il,. В pe)KHMP c!I)3зировка», задаваемом соответствующими c«гизлзми по сВЯзи 5. накопительный элемент разряжается и поддерживается в этом состоянин дО Tcx f)op, ПОИЗ не ИОяБи тся соотВетствуюгцпй сигнал иа Втором уп})анля оffIBVi ВХОДЕ |)JIOKB, IIUCJIÐ ЧЕГО CHOBB HBH (!f3ется описанный выше цикл заряда-разряда.

Один цикл заряда-разряда соответствует набору тактовых сигналов на выходе блока, необходимом). для вьгполнения одной команды процессора 10.

ФО ))и !)Л0 0зоорвтвHIJ.R

Устройство для управления операциями вводя-вывода дBHíûõ, содержащее процессор, ОлОк пЯмЯти н. блОк сопрчжениЯ, соединенные двухстооонйим и информационнымии сВязями, упрявляющнЙ Выход f)polMcс0р3 соединен с )правля)огцими Входами блока памяти и блока соп))яжения, ВхОды и Bbiхбды кОторОГО подключены сООТВетственио

KG Входам и ВыходЗМ УстРОЙства, ОтлнчпгоfqeecJI TeM, )fTo, c цель)0 повып1ения быстроgi=HcTBHH;l Ооеснечсн)<я yf иперс.) )у ио(Ги при менения для f!IHpoKofio класса Внешии х уcTPoHcTB H =. ВМ, В него Введен GJ!ÎK фоРмироваиич тактовых сигналов, первый управляющий вход которого соединен с управля)ощим выходом I)pOUecco})3, второЙ управляющий вход блока формирования такТОВЫХ СИГliBJIOB И УПРЯВЛЯ10щий ВХОД ПРОЦЕССОРЯ СОЕДИНЕНЫ С ) ПРЯВЛЯЮЩИМ ВХОДОМ устройства, выход блока формирования такToBb! x сигналов сОединен с тактовым входом процессора.

2, УСТРОЙСТВО BO H. 1, OtilU)l010fgePCA тем, чтО блОк $)opf!HpoBBHIIH тактовых сиГlfQ IoB соде})жит региcTp, схем1 сравнения, пересчетный узел и имп) льсныЙ Генератор, Выход KGTÎI)ОГО сОС jflHcí ГО счетным входОм пере(гчетнОГО узла, Bb!ходь! Которого и Выходы регист)а ПОдключены cGOTI)ETcTBBffffo Ko

Входам схемы сраВнения, пход реГистр3 и

fIQpBbIA ВхОд пе})есчетпОГО узла соединены с первым управляющим входом блока, Второй Вход пересчетного узла соединен со втоРЫМ ) IIPBBЛЯЮЩНМ ВХОДОМ ОЛОКЯ, TPBTHH

ЬХОД ООЬЕДННСН С ВЫХОДОМ ОЛОКЯ И ПОДКЛЮчен к Выходу сХемы сряВнеиия.

Источники ипформа.гии, принятые во Внимание при экспертизе

}. 1 }зтент :ЩД,})))» 3714635 кл. 34Π†1.5, кл. G 06 }r 3/00, }973.

2. 1}атент США № 3828325, 34Г) — 172.5, кл. Q ()6 F 1 (}(} } Ч74

64!435

Фиг./

Фиг. г

4риг.3

Составитель А. 5Керенов

Техред О. Луговая Корректор Л. Hefiuna

Тираж 779 Подписное

Редактор В. Лукин

Заказ 75! 4/44

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4