Устройство для управления вводомвыводом

Иллюстрации

Показать всеРеферат

Союз Соаетсммх

Соцмалмстмческмх

Респубпмк (и 641439 (61) Дополнительное к авт, свил-ву (22) Заявлено 03.02.77 (21) 2449980/18-24 (51) М. Кл.

С 06 F 3/04 с присоединением заявки №

Гоаудврственный номнтет

СССР ео делам нзобретеннй н открытнй (23) Приоритет

Опубликовано05.01.79.Бюллетень № 1

Дата опубликования описания 07.01.79 (S3) УЛК 681.325 (088.8) Л. Е. Баркова, А. А. Константинов, В. В;, Корнеев, А. С. Крылов и Д. Б. Подшивалов (72) Авторы изобретения (71, . Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВВОДОМ-ВЫВОДОМ

Изобретение относится к области вычис- лительной техники и может быть использовано при конструировании вычислительных систем.

Устройство предназначено для управления вводом-выводом данных электронных вычислительных машин, синхронизации рабоS ты процессора и оперативного запоминающего устройства с работой периферийных устройств.

Изве тно устройство 1), содержащее блок связи с процессором и памятью и не- 1О сколько каналов.

Недостатком известного устройства являегся то, что устройство прерывает программу процессора по специальным сигналам от периферийных устройств, снижая скорость вычислений.

Дублирование в каждом канале оборудования передачи данных, модификации управляющих слов, операционных регистров, хранящих управляющие слова, снижает степень использования оборудования. Кроме того, в устройстве отсутствует возможность управления каналами из работающего канала.

Наиболее близким по сущности техничес- ким решением задачи является устройство для управления вводом-выводом, содержащее три блока синхронизации обмена, первые входы которых соединены с соответствующими входами устройства, вторые входы блоков синхронизации обмена соединены с первым выходом блока управления, второй выход которого соединен с первыми входами блока сопряжения с памятью, регистра ввода, узла приоритетного обслуживания, первый вход блока управления соединен с первыми выходами блоков синхронизации обмена, вторые выходы которых соединены со вторыми входами регистра ввода и узла приоритетного обслуживания, выход которого соединен с управляющими входами регистра ввода н регистра вывог,a, выход которого через первую и вторую буферные памяти соединен со вторыми входами соответственно блока управления и блока сопряжения с памятью, выходы которого соединены с выходами устройства, четвертый вход устройства через третью буферную память соединен с третьими входами регистра ввода, узла приоритетного обслуживания и блока управления, четвертый, пятый и третий

64 439-1 выход которого соединены с соответствующими»в.. -.,: .,-н н выходом ус гроисгва тре тьн выходы блоков синхронизации обмена соединены с соответствующими выходам и

ycTpoAства (2j

8 известном ) стройстве оборудование модификации дескрипторов обмена дублируетсч в каждой секции аппаратуры обслуживания данных, что снижает степень использования оборудования.

Кроме того, система разработана для управления периферийными приборами но интерфейсу, отличающемуся от интерфейса.широко распространенных устройств фирмы 38М и E(: ЗВМ, и не- может работать с

HHi . È, Целью изобретения является повышение коэффициента использования оборудования.

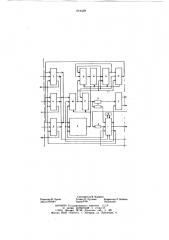

Поставленная цель достигается тем, что в устройство введены дополнительная память, исполнительный регистр, узел модификации, буферный регистр, причем выход узла приоритетного обслуживания соединен с первыми входами дополнительной памяти, исполнительного регистра, узла модификации, буферного регистра, выход которого соединен с третьими входами блоков синхронизации обмена, выход дополнительной памяти через исполнительный регистр соединен со вторыми входами буферного регистра, дополнительной памяти и узла модификации и первым входом регистра вывода, второй вход которого соединен с выходом регистра ввода и третьими входами дополнительной памяти, буферного регистра и узла модификации, выход которого соединен с четвертыми входами буферного регистра и дополнительной памяти.

Блок-схема устройства приведена на чертеже, где приведены блок управления блок сопряжения с памятью 2, блоки синхронизации обмена 3 — 5, узел приоритетного обслуживания 6, буферные блоки памяти 7 — 9, регистр ввода 10, регистр вывода 11, дополнительная память 12, исполнительный регистр 13, узел модификации 14, буферный регистр 15, узел запуска каналов 16.

Работа устройства по обмену с внешнимн устройствами ведется автономно от процессора, первоначальный же запуск осуществляется процессором. Последующие запуски каналов производятся как процессором, так и уже работающими каналами. Работа канала заканчивается по окончании цепочки команд в программе канала или по команде «Останов» из программы другого канала, Запуск канала от процессора производится через нулевой канал, в который принимается адрес программы. Нулевой каиал переводится блоком l в состояние «Работа» и в ием, как и в любом работающем канале, ведется обработка команды, считанной по адресу программы. Отработка команды, например «Начать обмен», включает:

-- дешифрацию кода команды блоком 1; — анализ узлом 16 состояния канала, указанного в команде, на возможность запуска (перевод его в состояние «Работа», обрагцение эа первой командой в программе канала через блок 2) — отработку программно-управляемого прерывания блоками 1, 2; — анализ признака «Цепочка команд» в обрабатываемой команде и переход, если предписано, к следующей команде работающего канала.

Считанные из ОЗУ команды управления периферийными устройствами пересылаются через регистры 10, l! в блоки синхронизации обмена, например 3. Блок 3 связывается с периферийным устройством, считывает начальный байт состояния, пересылает через регистры 10, 1! и буферную память 7 в блок 1 для анализа. Если байт состояния равен нулю, то блок разрешает блоку 3 продолжить команду. Блок 3 по запросам устройства набирает иэ байтов слово (при считывании с внешнего устройства — ВУ! и обращается с запросом в узел 6. Узел 6 обеспечивает обработку запросов блоков 3—

5 в соответствии с заданным приоритетом и позволяет увеличить пропускную способность высокоприоритетных каналов за счет снижения ее в менее приоритетных каналах, так чтобы не превышалась суммарная пропускная способность устройства. Принимая

ЭО слова (при считывании с BY) от блока 3 на регистр 10, узел 6 обеспечивает: считывание на исполнительный регистр 13 из дополнительной памяти 12 информации, относящейся к данному каналу, модификацию количества байтов и адреса слова „u ОЗУ в узле 14; обращение через регистр 11, буферную намять 8 и блок 2 в ОЗУ; запись модифицированной информации в дополни, тельную яамять 12; определение «Конца обмена». Все эти действия на регистрах и уз40 лах 6, 10 — 15 производятся последовательно над информацией, относящейся к различным каналам. Отработав очередной запрос канала, узел 6 обеспечивает запоминание его информаци" в дополнительной памяти 12 и освобождение регистров 10, 13, 15 и узла 14 для работы с запросами других каналов. Такая организация работы по обслуживанию запросов каналов позволяет повысить степень использования оборудования. Блок 3 по команде «Конец об в мена» выдает конечный байт состояния, который через регистры 10, 11 и память 7 пересылается для анализа в блок 1. Если в байте имеются указатели окончания, то узел 16 запускается на анал из признака

«Цепочка команд» в исполняемой команде н переход к следующей команде, если предписано. В «Цепочку команд» могут входить как команды управления периферийными устройствами, так н команды управления каналами. Это позволяет узлу 16, анализируя состояние каналов при исполнении команды в работающем канале, осуществлять управление ими из работающего канала.

Устройство имеет высокую степень использования оборудования, достигаемую тем, что проводится модификация управляющей информации, относящейся к операциям в каналах. Устройство позволяет уменьшить затраты времени процессора на управление вводом-выводом, благодаря способности со стороны работающих каналов управлять работой других каналов без участия процессора. Возможность перераспределения пропускной способности каналов и управлении со стороны работающих каналов другими каналами повысило гибкость управления каналами.

Использование устройства, наряду с экономией оборудования каналов, даваемой повышением степени его использования, позволяет упростить программирование взаимосвязанных операций ввода-вывода и несколько сократить потери производительности процессора на управление вводом-выводом.

Формула изобрете>(>(я

Устройство для управления вводом-выводом, содержащее три блока синхронизации обмена, первые входы которых соединены с соответствующими входами устройства, вторые входы блоков синхронизации обмена соединены с первым выходом блока управления, второй выход которого соединен с первыми входами блока сопряже>гия с памятью, регистра ввода, узла приоритетного обслуживания, первый вход блока управления соединен с первыми выходами блоков синхронизации обмена, вторье выходы которых соединены со вторыми входами регистра ввода и узла приоритетного Обслуживания, 1>ыход которого соед««нсн с « прявляюц(ими входами j>ÐÃ>>ñTj>B Вьодя и регистра вывода, яы:(од которого через nep«f вую и вторую буферные памяти соединен со

BTopb!«fff Bxo, >B «If> (ooTB(.TcTBcfffi0 блока управления и бл(1ка (Опряжения с памятью. выходы которого соединены с выходами устройства, ":åòâ(j«T>«,й ьход устройства через третью оу<1>срную >я. .пгь сосдинеи с тре>о тьими входами регистра ввода, узла приоритетного обслуживания и блока управления, четвертый, пятый входы и третий выход которого соединены с соответствующими входами и выходом устройства, третьи выходы блоков синхронизации обмена соединены с соответствующими выходами устроиства, огли«(аюи(евся тем, >70, с целью повышения коэффициента использования оборудования, в устройство введены дополнительная память, исполнительный регистр, узел модификации, буферный регистр, причем выход узла приоритетного об"л живания соединен с первыми входямн дополнительной памяти, исполнительного регистра, узла модификации, буферного регистра, выход которого соединен с третьими входами блоков синхронизации обмена, выход дополнительной памяти через исполнительный регистр со- единен со вторымн входами буферного регистра, дополнительной памяти и узла модификации и первым входом регистра вывода, второй вход которого соединен с выхОдОм регистра в130да и третьими вхОдями дополнительной памяти, буферного регистра ч узла модификации, выход которого соединен с четвертыми входамц оуц>ериого регистра и дополнительной памяти.

Источники информации, п>зннятые BO BffHмание прн зкспсртнзе

> («ате«(т ф!.«j ««(««j Я(>(1 j .(«« кл. 42 п> 3/К, 1971

2. Патент С11И № 36?5209, З Щ вЂ” ?2. 5, j g?2.

64l439

Составитель В. Корнеев

Текред О. Луговая Корректор Л- Небола

Тираж7 19 Подписное

Редактор B. Лукин

Заказ 75l4 44

ЦНИИПИ Государственного комитета СССР по делам изобретений и откр ьггий

l 13035, Москва, Ж-35, Раушская нзб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4