Устройство цифрового задания частоты следования импульсов

Иллюстрации

Показать всеРеферат

641455

П1

26

60 без флуктуаций мгновенного значения вьходной частоты.

Однако, расширение диапазона изменения заданного кода требует пропорционального увеличения объема счетчика и обоих управляемых делителей, каждый из которых включает счетчик, регистр памяти и блок переноса кода, что существенно увеличивает объем оборудования устройства и недоиспользование его,в разных участках диапазона.

Цель. предлагаемого изобретения расширение диапазона изменения заданного кода.

Для этого в устройство .цифрового задания частоты следования импульсов содержащее генератор эталонной частоты, управляемые делители часто ты, суммирующий счетчик, блоки переноса кода, блоки управления и блок установки задания, введены блоки вычитания импульсов, элемент ИЛИ, вентиль и дополнительный управляемый делитель частоты, состоящий из ïîñледовательно соединенных счетных декад, образующих счетчик-делитель, реверсивного регистра сдвига, дополнительного элемента ИЛИ и группы вентилей, импульсные входы которых подключены ко входам соответствующих счетных декад счетчика-делителя, управляющие входы — к разрядным выходам реверсивного регистра сдвига, а выходы через дополнительный элемент ИЛИ вЂ” к сигнальным входам первого управляемого делителя частоты, при этом вход счетчика-делителя подключен к выходу генератора эталонной частоты, выход - ко второму входу второго блока управления, а выходы " двух предпоследних счетных декад— к первым входам блоков вычитания импульсов, вторые входы которых соединены с выходом первого управляемого делителя частоты, а выходы — со знаковыми входами реверсивного регистра сдвига непосредственно и через элемент ИЛИ вЂ” с третьим входом второго блока управления и с управляющим входом вентиля, импульсный вход которого подключен к выходу предпоследней счетной декады счетчика-делителя, а выход — ко входу реверсивного регистра сдвига.

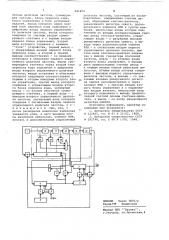

На чертеже представлена структурная электрическая схема предлагаемого устройства цифрового задания часто ты следования импульсов.

Оно содержит генератор 1 эталонной частоты, управляемые делители

2 и 3 частоты и дополнительный управ ляемый делитель 4 частоты, суммирующий счетчик 5, блок 6 устройства задания, блоки 7 и 8 переноса кода, блоки 9 и 10 управления, блоки 11 и 12 вычитания импульсов, элемент

ИЛИ 13, вентиль 14. Дополнительный управляемый делитель 4 частоты состоит из счетчика-делителя 15, включающего последовательно соединенные счетные декады 16-20, реверсивного регистра 21 сдвига, вентилей 22-24, дополнительного элемента ИЛИ 25.

Устройство работает следующим образом.

Выходная последовательность импульсов генератора 1 с высокой частотой следования поступает на сигнальный вход дополнительного управляемого делителя 4 частоты, где она делится на коэффициент деления, кратный 10 и задаваемый положением реверсивного регистра 21 сдвига. Если имеется сигнал на разрядном выходе реверсивного регистра 21 сдвига, то через открытый этим сигналом вентиль 22 частота с выхода генератора 1 через дополнительный элемент ИЛИ 25 поступает на выход дополнительного управляемого делителя 4 частоты.

При этом коэффициент деления делителя 4 частоты равен И=10 1. При поступлении сдвигающих импульсов с выхода вентиля 14 измеряется положение регистра 21 в зависимости от знака вправо или влево. При изменении состояния регистра 21 вправо коэффициент деления делителя увеличивается в 10 раз на каждый шаг. Так при появлении сйгнала на следующем раз-, рядном выходе регистра 21 открывается вентиль 23 и на выходе делителя 2 ! частоты появляется частота с выхода счетной декады 16, равная „О, При поступлении tl импульсов на вход регистра 21 коэффициент деления станет равным M=10, а на выходе делителя и

4 частоты сформируется частота Fo= „ и с,п -ой счетной декады счетчика-делйтеля 15. При изменении знака сдвига регистра 21 положение его будет сдвигаться влево, уменьшая коэффициент деления.

Импульсы с выхода делителя 2 частоты поступают на сигнальные входы делителей 2 и 3 частоты, каждый из которых содержит вычитающий счетчик, регистр памяти и блок переноса кода.

Коэффициент деления этих делителей определяется кодами, хранимыми в регистрах памяти и обнуляемых по сигналам управления, поступающим от блоков 9 и 10. Коэффициент деления делителя 2 частоты формируется в блоке 6.

По сигналу пуск в блоке 9 формируются сигналы управления, переписывающие через блок / код задания К а в предварительно обнуленный регистр памяти делителя 2 частоты.

Запись этого кода из регистра памяти в счетчик делителя 2 частоты осуществляется через открытый сигналом блок переноса .(на чертеже не показаны) каждым импульсом на выходе счетчика, возникающим после списания числа из счетчика, осуществляется новая

641455

ЦНИИПИ Заказ 7875/Z

Тираж 713 Подписное ляемые делители частоты, суммирующий счетчик, блоки переноса кода, блоки управления и блок установки задания, выход которого через первый блок переноса кода подключен к цифровому входу первого управляемого делителя частоты, выход которого соединен со счетным входом суммирующего счетчика и с первым входом первого блока управления, второй вход которого соединен с зажимом пуск устройства, первый выход— с управляющим входом первого блока переноса кода, а второй и третий выходы соответственно — co входами установки и обнуления первого управляемого делителя частоты, выход суммйрующего счетчика через второй блок переноса кода подключен к цифровому входу второго управляемого делителя частоты, входы установки и обнуления которого соединены соответственно с первым и вторым выходами второго блока управления, третий выход которого соединен с управляющим входом второго блока переноса кода, четвертый выход — со входом обнуления суммирующего счетчика, а первый вход — с выходом второго управляемого делителя частоты, сигнальный вход которого соединен с сигнальным входом первого управляемого делителя частоты, о т л и ч а ю щ е е с я тем, что, с целью расширения диапазона изменения заданного кода, в него введены блоки вычитания импульсов, элемент ИЛИ, вентиль и дополнительный управляемый делитель частоты, состоящий из последовательно соединенных счетных декад, образующих счетчик-делитель, реверсивного регистра сдвига, дополнительного элемента ИЛИ и группы вентилей, импульсные входы которых подключены ко входам соответствующих счетных декад счетчика-делителя, управляющие входы — к разрядным выходам реверсивного регистра сдвига, а выходы через дополнительный элемент

ИЛИ вЂ” к сигнальным входам первого

1О управляемого делителя частоты, при этом вход счетчика-делителя подключен к выходу генератора эталонной частоты, выход — ко второму входу второго блока управления, а выходы двух предпоследних счетных декад к первым входам блоков вычитания импульсов, вторые входы которых соединены с выходом первого управляемого делителя частоты, а выходы — co знаковыми входами реверсивного регистра сдвига непосредственно и через элемент ИЛИ вЂ” с третьим входом второго блока управления и с управляющим входом вентиля, импульсный вход которого подключен к выходу предпоследней счетной декады счетчика-делителя, а выход — ко входу реверсивного регистра .сдвига.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Ф 222465, кл. Н 03 К 23/02, 1968.

2. Авторское свидетельство СССР

М 282748, кл. С 08 F 1/00, 1968.

Филиал ППП Патент, г.ужгород, ул. Проектная, 4