Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Соаетекмх

Социалист мчесимх

Республик

ОП ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТВЛЬСТВМ (61) Дополнительное к авт. свил-ву (22) Заввлеио 16.01. 76(21) 2316524/18-24 ((() 641499 (5I) М. Кл.

6 11 С 17/00

С ЧтисоЕдииеиием заявки № 2317142/18-24

231 7725/18-24 (И} Приоритет

Гесударстваххих каетет

СССР в двлам хыбрвтвхх1 к еткритв»

Опубликовано05.01.79.Бюллетень М 1

Дата опубликования описания 08.01.7ц (5З) УДК681. 327.

66(088 8) (72) Авторы изобретения

В. И. Корнейчук, А. В. Городняй, E. Н. Сосноичнк и„ К;",Г;-Цъпков !

1-,. !:::; : —.: ::.:" ( (Киевский ордена Ленина политехнический институт (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники, а именно к заноминающим устройствам (ЗУ).

Известны постоянные ЗУ, сод(ержащие числовые блоки с большим чнслом элементов связи либо с большим числом прошитых сердечников, характеризующиеся большой потребляемой мощностью, неравномерностью нагрузки на адресные шины и низкой надежностью ) I.

Наиболее близким техническим решением является постоянное запоминающее устройство, содержащее дешифратор адреса, соединенный с адресными шиками накопителя, н первый блок инвертирования чисел, выходы которого соединены с выходами устройства f2).

Недостаток известных устройств — большое число элементов связи, используемых при реализации накопителя и дешифратора, большая разрядность числового блока и низкая надежность устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что оно содержит второй блок инвертирования чисел, входы которого соединены с разрядными шинами накопителя, а выходы — со входами первого блока инвертирования чисел, а также тем, что оно содержит дополнительный блок памяти, входы которого нодключены к дешифратору адреса, а выходы— к управляющим входам второго блока инвертирования чисел, а также тем, что второй блок инвертирования чисел содержит сумматоры по модулю два и узел управления, выходы которого соединены со входами сумматоров по модулю два, другие входы которых соединены со входами блока, выходы нх — с выходами блока, а входы узла управления соединены с управляющими входами блока, а также тем, что второй блок инвертирования чисел содержит коммутатор, инверторы, элементы ИЛИ н узе(т управления, выход которого соединен с управляющим входом коммутатора, входы которого соединены со входами блока, а выходы— непосредственно н через янверторы подключены ко входам соответствующих элементов ИЛИ, выходы которых соединены c выходамн блока, а входы узла управления соединены с управляющими входами блока.

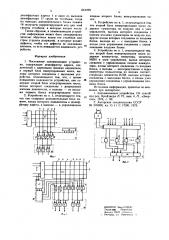

На фиг. представлена блок-схема постоянного запоминающего устройства; на

641499 фиг. 2 н 3 — - варианты выполнения второго блока инвертирования чисел и блок-схемы устрой тва.

Постоянное запоминающее устройство содержит дешифратор адреса 1, выходы кото- 5 рого подключены к адресным шинам 2 накопителя 3, который соединен с запоминающими элементами 4 и управляющим элементом 5 накопителя 3 с помощью элементов связи 6. Разрядные шины накопителя 3 подключены ко входам второго блока 7 инвертирования чисел (по столбцам), содержащего сумматоры 8 по модулю два и узел управления 9, состоящий, например, нэ яче.ек памяти, и соединенный с одним из входов сумматоров 8 по модулю два, другие входы которых соединены со входами блока

7, а выходы — с его выходами. Выходы блока 7 подключены ко входам первого блока 10 инвертирования чисел (по строкам), выходы которого подключены к выходам ЗУ.

Второй блок 7 инвертирования чисел (фиг. 2) содержит коммутатор !1 ° к управляющим входам которого подключены выходы узла управления 12, а остальные входы— ко входам блока, соединенным с выходами накопителя, входы узла управления подключены к управляющим входам блока. Выходы коммутатора непосредственно и через инверторы 13 подключены ко входам группы элементов ИЛИ 14, выходы которых соединены с выходами блока 10.

Второй блок 7 инвертирования чисел Эo (фиг. 3) может быть выполнен в виде сумматоров 15 по модулю два, к первым входам которых подключены выходы накопителя 3, а ко вторым — выход дополнительного блока иамяти 16, ко входам которого через дешифратор 17 групп по столбцам

3» подключена часть входов дешифратора адреса 1. Выходы второго блока 7 инвертирования чисел подключены ко входам первого блока 10 инвертирования чисел.

Запись информации в накопитель 3 осуществляется с помощью элементов связи 6, соединяющих адресные шины дешифратора

1 с разрядными шинами (запоминающими элементами 4 и управляющим элементом

5) в тех местах, где необходимо записать логическую «1».

Устройство но фиг. 1 работает следующим образом.

При возбуждении одной из адресных шин дешифратора 1 иа выходе накопителя

3 получается трансформированный код чис- «О ла, соответствующего данному адресу, который поступает на входы блоха инвертирования чисел 7. В блоке 7 иивертируютсяте разряды, которые принадлежат столбцам, хранящимся в обратном коде в накопителе 3. Полученный код с выходов блока 7 инвертируется в блоке 10, если значение на выходе управляющего элемента 5 после прохождения через блок 7 равно логической «1», или не иивертируется, если эначение на выходе управляк>щего элемента 5 равно логическому «О».

Значения дополнительных разрядов по столбцам хранятся в узле управления 9 (коды инвертирования по столбцам) и они управляют сумматорами 8 блока 7. Если значение i-ro дополнительного разряда по столбцам равно логической «1», то на выходе i-ro сумматора 8 получаем при чтении инвертированное значение i-го столбца.

Более гибко можно трансформировать информацию при записи, если инвертировать не полностью строки и столбцы накопителя, а группы разрядов (фиг. 2}. При этом значения информационных разрядов записываются в запоминающие элементы 4, а значения дополнительных разрядов по строкам — в управляющие элементы 5, число которых зависит от числа групп. В зависимости от значений дополнительных разрядов по столбцам устанавливаются инверторы 13, число которых равно числу групп по столбцам. Инверторы 13 устанавливаются в те позиции, для которых дополнительные разряды по столбцам равны единице.

Например, в одну группу можно отнести все числа, старший разряд кодов адресов которых равен «О», а во вторую — числа, старший разряд кодов адресов которых равен «1». Для конкретной информации, которую предстоит записать в матрицу постоянного ЗУ, следует выбирать метод, который позволяет сократить число элементов связи 6. В зависимости от способа разбиения по столбцам подключают управляющие входы узла управления 9. Блок ? работает следующим образом. Узел управления 9, в зависимости от. адреса считываемого слова, определяет группу по столбцам, в которую входит это слово и возбуждает соответствующий управляющий вход коммутатора 11, который осуществляет подключение накопителя 3 к инверторам 13, соответствующим данной группе столбцов, причем инвертнруются значения тех разрядов, которые входят в столбцы, коды которых хранятся в обратном коде. С выходов элементов 14 получаем необходимый код.

При выполнении блоков постоянного запоминающего .устройства в соответствии с фиг: 3 в сумматорах 15 по модулю два блока 7 инвертируются значения тех разрядов кода, считанного из накопителя 3, для которых значения соответствующих им разрядов корректирующего кода групп по столбцам равны «1», а в сумматорах по модулю в блоке 10 инвертируются те группы разрядов, для которых значения соответствующих им уйравляющих элементов после прохождения через сумматоры по модулю два 15 равны

«1».

Дополнительный блок памяти 16 подключается в зависимости от используемого разбиения столбцов на группы и в зависимости от адреса возбуждается один иэ выходов

Формула изобретения

l

1

1

7) Юг. ю дешнфратора адреса и один из выходов дешифратора 17 групп по столбцам, тогда на выходах дополнительного блока памяти

l6 получаем корректирующий код для этой группы столбцов, в которую входит число.

Таким образом, в запоминающем устройстве информация может быть закодирована записью обратных кодов тех столбцов или строк (группы разрядов), в которые входят дефекты, чтобы эги дефекты не оказывали влияния, то есть повышается надежность устройства.

Постоянное запоминающее устройство, содержащее дешифратор адреса, соединенный с адресными шинами накопителя, и первый блок инвертирования чисел, выходы которого соединены с выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит второй блок инвертирования чисел, входы которого соединены с разрядными шинами накопителя, а выходы — со входами первого блока инвертирования чисел.

2, Устройство по п. 1, отличающееся тем, что оно содержит дополнительный блок ïàмяти, входы которого подключены к дешифратору адреса, а выходы — к управляющим е 83 входам второго блока инвертирования чисел.

3. Устройство по и. 1, отличающееся тем, что второй блок инвертирования чисел содержит сумматоры по модулю два и узел управления, выходы которого соединены с одними входами сумматоров по модулю два, другие входы которых соединены со входамн блока, выходы их — с выходами блока, а входы узла управления соединены с управляющими входами блока.

4. Устройство по и. 1, отличающееся тем, что второй блок инвертирования чисел содержит коммутатор, инверторы, элементы

ИЛИ и узел управления, выход которого соединен с управляющим входом коммутатора, входы которого соединены со входами блока, а выходы — непосредственно и череъ ииверторы подключены ко входам соответствующих элементов ИЛИ, выходы которых соединены с выходами блока, а входы узла управления соединены с управляющими входами блока.

Источники информации, принятые во внимание прн экспертизе: !. Запоминающие устройства. Сб. статей под ред. Крайзмера Л. П., вып. 4, Л., «Энергия», 1974, с. 89.

2. Авторское свидетельство СССР № 376808, кл. G 11 С 17/00, 1973.

ЦНИИПИ Заказ 7522(47

Тираж С30 Полоиеоое

Филиал !lllH Пагеч i, г Ужгород, ул l lðîåêòíë÷