Устройство формирования ступенчатотрапецеидального напряжения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалмсткческих

Республик » 641637 (6l) Дополнительное к авт. свнд-ву (22) Заявлено 01,08.76 (21) 2393908/18 21 с присоадинеинем заявки № (23) Г1риоритет

Опубликовано05.01.79.Бюллетень М 1

Дата опубликования описания 10.01.7Э (51) М. Кл. а

Н 03 К 4/02

Государственный комитет

СССР по делам изооретений и открытий (53) УДК 621.314 (088,8) (72) Авторы изобретения

А, И, Овчаренко и В. М. Тр

Украинский заочный политехнический (71) Заявитель (54) УСТРОЙСТВО ФОРМИРОВАНИЯ СТУПЕНЧАТО-ТРАПЕЦЕИ11АЛЬНОГО. НАПРЯЖЕНИЯ

Изобретение относится к импульсной технике н может быть использовано в программных системах автоматического управлення.

Известен генератор импульсов, содер кащий интегрнруюшне усилители, амплитудные дискриминаторы, 1$-триггеры н переключателя j l J.

Недостатком данного генератора является нестабильность крутизны фрон — îâ выходного напряжения.

Более совершенным является устройство формнрозання ступенчато-трапецеидального напряжения, содержащее дешифратор, устройство временных -àäåðæåê,,триггер реверса, счетчик импульсов, преобразователь код-напряжение, элемент совпадення, генераторы пикообразных напряжений (2) .

Недостаток устройства — невысокая стабнльность фронтов выходного ступенчатотрапецендального напряжения.

Цель предлагаемого изобретения — повышенне стабильности крутизны фронтов нмпульсов выходного напряжения.

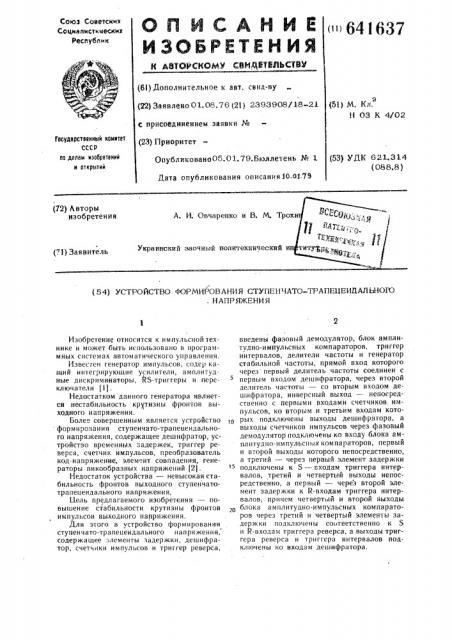

Для этого в устройство формирования ступенчато-трапецендального напряжения, содержащее элементы задержки, дешифратор, счетчики импульсов н триггер реверса, введены фазовый демодулятор, блок амплитудно-импульсных компараторов, триггер интервалов, делители частоты н генератор стабильной частоты, прямой вход которого через первый делитель частоты соединен с первым входом дешнфратора, через второй делитель частоты — со вторым входом дешифратора, инверсный выход — непосредственно с первыми входами счетчиков импульсов, ко вторым н третьим входам которых подключены выходы дешнфратора, а выходы счетчиков импульсов через фазовый демодулятор подключены ко входу блока амплитудно-импульсных компараторов, первый н второй выходы которого непосредственно, а третий — через первый элемент задержки подключены к S — входам триггера интервалов, третий н четвертый выходы непосредственно, а первый — через второй элемент задержки к К-входам триггера интервалов, причем четвертый н второй выходы блока амплитудно-импульсных компараторов через третий н четвертый элементы задержки подключены соответственно к S н R-входам триггера реверса, а выходы триггера реверса н триггера интервалов подключены ко входам дешифратора.

641637

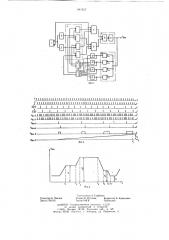

На фиг. 1 изображена структурная элекрическая схема предлагаемого устройства; на фиг. 2 представлены временные диаграммы, поясняющие принцип его работы; на фиг. 3 дан график выходного напряжения ступенчато-трапецеидальной формы.

Предлагаемое устройство содержит генератор 1 стабильной частоты, прямой выход <оторого подключен через делители 2 и 3 частоты, ко входам дешифратора 4. Дешифратор может быть выполнен, и пример, на четырех потенциальных логических элементах И (И1 — И4). В этом случае выход делителя 2 частоты подключается ко входам двух первых элементов И, а выход делителя 3 частоты — ко входам двух последних.

Выходы дешифратора 4 попарно подключены ко входам счетчиков 5 и 6 импульсов.

Счетчики 5 и 6 импульсов — двоичные с одинаковым количеством разрядов и с логикой ИЛИ на входах. Выходы счетчиков 5 и 6 импульсов подключены ко входам фазового демодулятора 7 (преобразователя раз- ности фаз импульсов в напряжение), который может быть выполнен, например, в виде последовательно соединенных RS-триггера 8 и фильтра 9 нижни: частот. Выход фазового демодулятора 7 подключен ко входу блока 10 амплитудно-импульсных компараторов. Количество амплитудных компараторов в блоке 10 зависит от требуемой формы выходного напряжения.

Блок 10 (фиг. 1) содержит четыре амплитудно-импульсных ком паратора. Причем компараторы построены таким образом, что импульсы на выходах двух первых появляются в случае 13выв>Ц и 1.)выл >U> соответственно, а на выходах двух других— в случае Ьых < 14 и Ъх < U, соответственно, где Ц Ц, Uq, L4, — требуемые уроцни выходного напряжения (фиг. 3) . Пер вый и второй выходы блока 10 подключ.ны непосредственно, а третий через элемент 11 задержки к S — входам триггера 12 интервала, третий и четвертый выходы блока 10 подключены непосредственно, а первый через элемент 13 задержки к R-входам триггера 12 интервала, четвертый выход блока 10 подключен через элемент 14 задержки к S-входу триггера 15 реверса, а второй выход блока 10 через элемент 16 выдержки к R-входу триггера 15 реверса. Прямые выходы триггеров 15 реверса и триггера 12 интервала подключены соответственно ко входам первых двух элементов И дешифратора 4, а их инверсные входы — соответственно ко входам двух других элементов И дешифратора 4.

Предлагаемое устройство работает следующим образом.

Генератор стабнлыюй частоты вырабатывает две импульсные последовательности с частотамн Г и F с разностью фаз 180 (фиг. 2). На выходах делителей 2 и 3 частоты получаются импульсные последовательности с частотами -- — и - — (фиг. 3), F F к„К„ где К ф, — коэффициенты делеЗь ния делиТелей 2 и 3 частоты соответственно.

Предположим, что разрешающие уровни находятся на прямом выходе триггера 15 и инверсном выходе триггера 12 интервала. Это означает, чтб открыты первый и четвертый элементы И дешифратора 4,т.е. импульсы частоты проходят на счетчик 5

15 импульсов, а импульсы частоты — — — на км счетчик 6 импульсов. На выходах счетчиков 5 и 6 суммируют во времени импульсы F, — и F, — соответственно. Импульсы

14г ) и переполнения счетчиков 5 и 6 следуют с частотами — — -я - и — — ;- з- соот}1. +gф 1г +)Р/К

t а ветственно, где п — число двоичных разрядов счетчиков 5 и 6 (фиг. 2). При этом фаза между импульсами переполнения счетчиков 5 и 6 ступенчато-линейно нарастает, что соответствует ступенчато-линейному увеличению коэффициента заполнения импульсной последовательности на выходе триггера 8 фазового демодулятора 7 и линейному

ЗО увеличению напряжения на выходе фильтра 3 фазового демодулятора 7, Процесс продолжается до тех пор, пока 1 1вц„ие достигнет значения Ц (в момент времени tI) (фиг.,2, 3). В этот момент времени срабатывает первый компаратор блока 10 и его ф выходной импульс устанавливает по одному из S-входов триггер 12 интервала в противоположное предыдущему состояние т. е. блокируется прохождение импульсов — че

92 рез четвертый элемент И дешифратора 4, 4о а счетчики 5 и 6 заполняются через его первый и второй элементы И импульсами частоты — . Фаза между импульсами

1 я переполнения счетчиков 5 и 6 остается пос- тоянной, постоянен коэффициент заполне45 ния импульсной последовательности на выходе триггера 8, соответственно постоянно и напряжение бвых ) {интервал t < t < t ) (фиг. 3) . Через время t> — t< (фиг. 3), определяемое элементом 13 задержки, триггер 12 интервалов по одному из К-входов устанавливается в прежнее состояние, при котором запирается второй элемент И дешифратора 4 и отпирается его четвертый элемент И. Напряжение с частотой

K ü снова поступает на счетчик 6 импульсов я фаза между импульсами переполнения счетчиков 5 и 6 начинает нарастать, Формируется фронт на участке (t> < t< Q ) (фиг. 3)

В момент (з срабатывает второй компаратор, переключая триггер 12 интервалов, Снова ечетчики 5 и 6 импульсов заполняются

64!637 формцла изобретения одинаковыми частотами Г+ -- -- и формиf1

1 Ь руется постоянное напряжение на интервале (Q < t<. Q ) (фиг. 3). Через время (g — t3) (фиг. 3), определяемое элемен ом 16 за.— держки, переключается триггер 15 реверса и теперь напряжение с частотой — постук пает уже на счетчик 6 импульсов, фаза между импульсами переполнения ступенчато-линейно уменьшается, формируется линейно-падающий участок Q < t< t; ) 1ц,, . (фиг. 3) В момент срабатывает третий компаратор блока 10, переключается триггер 12 интервалов, через третий и четвертый элементы И дешифратора 4 на счетчики 5 и 6 импульсов проходят импульсы частоты -ф — и формируется интервал (< t< Q (фиг. Я .Через время Q — (;, определяемое элементом 1! задержки, переключается триггер 12 интервалов, открывается второй элемент И дешифратора 4. Закрывается его четвертый элемент И. Формируется интервал (4< t< tð ) (фиг. 3). В момент t< срабатывает четвертый компаратор блока 10, переключается триггер 12 интервалов. Формируется и нтервал ((т < t< (р ) (фиг, 3).

Через время te — tj (фиг. 3), определяемое элементом 14 задержки, переключается триггер 15 реверса, первый элемент И дешифратора 4 и закрывает его третий элемент И. Далее процесс повторяется.

Изменение крутизны фронтов может быть осуществлено изменением Кд или Кф, изменение уровней срабатывания элементов И дешифратора 4 — регулировкой установок компараторов блока 10, изменение интервалов (ь.. 4; ta...Q; 4...ts, (т."4 регулировкой времени задержки элементов заде жки 11, 13, 14, 16.

1 спользование предлагаемого устройства формирования ступенчато-трапецеидального напряжения позволяет повысить стабильность крутизны фронтов выходного напряжения, т. е. производится цифровое интегрирование (суммирование) цифровой величины (постоянной разности частот).

В этом случае нестабиЛьность фронта выходного сигнала будет определяться неста10

ЗО

35 бильностью частогы и коэффициентов деления К4 и К4. Эти нестабильности могут быть получены весьма малыми (10 и менее) при использовании кварцевого генератора и цифровых (счетчиковых) делителей частогы.

Устройство формирования ступенчатотрапецендального напряжения, содержащее элементы задержки, дешифратор. счетчики импульсов и триггер реверса, отличающееся тем, что, с целью повышения стаоильности крутизны фронтов выходных импульсов, в него введены фазовый демодулятор, блок амплитудно-импульсных компараторов, триггер интервалов, делители частоты и генератор стабильной частоты, прямо" выход, которого через первый делитель частоты соединен с первым входом дешифратора, через второй делитель частоты — со вторым входом дешифратора, инверсный выход — непосредственно с первыми входами счетчиков импульсов, ко вторым и третьим входам которых подключены выходы дешифратора, а выходы счетчиков импульсов через фазовый демодулятор подключены ко входу блока амплитудно-импульсных компараторов, первый и второй выходы которого непосредственно, а третий — через первый элемент задержки подключены к S-входам триггера интервалов, третий и четвертый выходы непосредственно, а первый — через второй элемент задержки к R-входам триггера интервалов причем четвертый и второй выходы блока амплитудно-импульсных компараторов через третий и четвертый элементы задержки подключены соответственно к S и R-входами триггера реверса, а выходы триггера реверса и триггера интервалов подключены ко входам дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 327717, кл. Н 03 К l/12, 1972.

2. Авторское свидетельство СССР № 464961, кл. Н 03 К 4/02, 1975.

Риг 1

ШШ.Ш Ш «ШШ ШШШШШШШ Ш!! дьш ш LUJJJJ

1 в. 5 -!iiiiil-l-i!i-LlllLLII ll -l-ill-! JJLLliLU LllllJJLLllLUIL

IJILIIILII IIII JIllIJlllJJ ШШШШВШ вЂ” с 7Ы.а

4 Х б У

3

А 2. 3

Составитель А. Горбачев

Текред О. Луговая Корректор А. Кравченко

Тираж 105 3 Подписное

Редактор Б. Павлов

Заказ 7541I55

ЦНИИПИ Государственного комитета СССР по делам изобретений и открьпий!! 3035, Москва, . Ж-35, Раугиская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4