Управляемый инвертор на мдп-транзисторах

Иллюстрации

Показать всеРеферат

641655 чен первый ускоряющий конденсатор, сток нагрузочного транзистора подключен к шине питания, а исток — к стоку переключающего транзистора, исток которого подключен к общей шине, последовательно включенные зарядный и разрядный транзисторы между шиной питания и общей шиной, входную шину, подклю- 5 ченную к затворам переключающего и разрядного транзисторов, и выходную шину, подключенную к истоку зарядного и стоку Разрядного транзисторов, введены два транзистора смещения, затворы ко- 10 торых и сток первого из них подключены к шине питания, и второй ускоряющий конденсатор, одна обкладка которого подключена к истокам нагрузочного транзистора и второго транзистора 15 смещения, а вторая — к истоку первого транзистора смещения, к стоку второго транзистора смещения и к затвору зарядного транзистора.

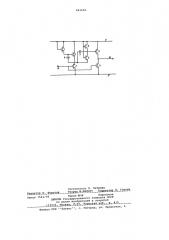

На чертеже представлена принципиальная электрическая схема устройства.

Затвор и сток транзистора предварительного заряда 1 подключены к шине питания 2, а чсток — к затвору нагрузочного транзистора 3, между затвором и истоком которого включен ускоряющий конденсатор 4. Сток транзистора 3 подключен к шине питания 2, а исток — к стоку переключающего транзистора 5, к истоку транзистора смещения 6, к одной обкладке ускоря- 30 ющего конденсатора 7, вторая обкладка которого подключена к стоку трачзистора смещечия б, к истоку транзистора смещения 8 и к затвору зарядного транзистора 9. Затворы транзисторов 6, 8 :35 и стоки транзисторов 8, 9 подключены к шине питания 2, исток транзистора

9 — к выходной шине 10 и к стоку разрядного транзистора 1.1, истоки транзисторов 5 и 11 подключены к об-. щей шине 12, а затворы этих транзисторов — ко входной шине 13, Инвертор работает следующим образом.

При поступлении на входную шину 13 напряжения, соответствующего уровню логической единицы, открываются тран- 45 эисторы 5 и 11, и ускоряющий конденсатор 4 заряжается через транзистор предварительногО заряда 1 до уровня где Š— напряжение питао ния, а Π— пороговое напряжение ry транзистора 1. При этом открывается транзистор 3, конденсатор 7 заряжается до уровня 00 задаваемого цепью смещения, образованной транзисторами 8 и б. Зарядный транзистор 9 закрыт, и на выходной шине 10 формируется напряжение логического нуля.

При поступлении на входную шину

13 напряжения логического нуля напряжение на стоке транзистора 5 поднимается до уровня Е д (напряжение на затворе транзистора 5 повышается до величины 2Е > - J за счет передачи напряжения на стоке этого транзистора через ускоряющий конденсатор), а напряжение на затворе зарядного транзистора 9 повышается до величины Е и + U,и на выходной шине 10 формируется напряжение логической единицы, равное

Дополнительно введенные цепь смещения, образованная транзисторами 8, б, и ускоряющий конденсатор 7 позволяют повысить уровень напряжения логической единицы на выходе устройства до величины напряжения питания.

Формула изобретения

Управляемый инвертор на ."1ДП-транзисторах, содержащий транзистор предварительного заряда, затвор и сток которого подключены к шине питания, а исток — к затвору нагрузочного транзистора,между затвором и истоком icoторого включен первый ускоряющий конденсатор,сток нагрузочного транзистора подключен к шине питания,а исток к стоку переключающего транзистора, исток которого подключен к общей шине, последовательно включенные зарядный и разрядный транзисторы между шиной питания и общей шиной, входную шину, подключенную к затворам переключающего и разрядного транзисторов, и выходную шину, подключенную к истоку зарядного и стоку разрядного транзисторов, о т л и ч а ю шийся тем, что, с целью повышечия уровня выходного напряжения логической единицы, в него введены два транзистора смещения, затворы которых и сток первого из них подключены к шине питания, и второй у скоряющий конденсатор, одна обкладка которого подключена к истокам нагрузочнаго транзистора и второго транзистора смещения, а вторая к истоку первого транзистора смещения, к стоку второго транзистора смещения и к затвору зарядного транэис" тора.

Источники информации, принятые во внимание при экспертизе

1. Электроника Р 4, 1971 с. 31 °

2. Патент США М 3912948, кл. 307279, 1975.

641655

Составитель Л. Петрова

Техред Ю.Ниймет Корректор И. Гоксич

Редактор Б. Федотов

Заказ 7542/56 Тираж (Оif Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Иосква Х-35, Раушская наб. д. 4j5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4