Цифро-аналоговый корреляционный приемник

Иллюстрации

Показать всеРеферат

Союз Советск

Соцмалметмческих

Респубпнн

<»> 64 1659 (61) Дополнительное к авт. свил-ну (22) Занвлено 03.05.76 (21}2357489/18-09

С присоединением заявки № (23) Приоритет (51) М. Кл.

Н 04 В 3./08

Говудврвтвениый лвмлтет сссю в делам ювбретелий

И 0TKPbITNN

Опубликовано 05.01.79.1зюллетень № 1

Дата опубликования опнсапия 08.01.78 (53) УДЕ 821.372. 54(088.8) (72) Авторы изобретения

О. Г. Каратаев В. И. Танагаев, B. С. Атфттов и Г. И. Смыспов (71) Заавитель (54} ЦИФРОАНАЛОГОВЫЙ КОРРЕЛЯЦИОННЫЙ

ПРИЕМНИК

Изобретение относится к радиотехнике и может использоваться в системах радиосвязи.

Известен цифроаналоговый корреляционный приемник, содержащий в основном канале последовательно соединенные перемножитель и интегратор, а также первый ключ, второй ключ, выходом соединенный с входом порогового блока, генератор тактовых импульсов, опорный генератор, основной элемент задержки, основной вентиль, счетчик, оконечный .блок (1) . 10

Однако в известном устройстве велико время обработки информации.

Цель изобретения — сокращение време ни обработки информации.

Для этого в цифроаналоговый корреляционный приемник, содержащий в основном канале последовательно соединенные неремножитель и интегратор, а также первый ключ, второй ключ, выходом соединенный с входом порогового блока, генератор тактовых импульсов, опорный генератор, основной 20 элемент задержки, основной вентиль, счетчик, оконечный блок, введены и дополнительных каналов, а в каждом из каналов введены накопитель, триггер; дополнительный элемент задержки, дополнительный вентиль, первый элемент ИЛИ, а также общие для всех каналов второй элемент ИЛИ, дешифратор, блок поиска максимума.

Первые входы перемножителей объединены и являются входом устройства. Вторые входы неремножителей также объединены и соединены с вь ходом опорного генератора, вход которого через основной элемент задержки соелинсH с одним вь|ходом основного вентиля. Первый вход основного вентиля соединен с выходом генератора тактовых импульсов.

Выход основного элемента задержки соединен также с другими ьходами интеграторов, выходы которых соединены с входами параллельно соединенных первых ключей.

Другие входы первых ключей соединены с соответствующими выходами дешифратора, а выходы первых ключей через накопители соединены с первымн входами вторых. ключей, вторые входы которых соединены с выходами блока поиска максимума. Входы этого блока соединены с другими выходами вторых ключей, а третьи входы — объединены и через дополнительный элемент задержки соединены с выходом дешифратора, который

641659 также соединен с первыми входами дополнительных вентилей.

Выходы дополнительных вентилей через первый элемент ИЛИ соединены с первыми входами триггера, вторые входы которых соединены с выходами порогового блока.

При этом одни выходы триггеров всех каналов через второй элемент ИЛИ соедине«ы с одним входом счетчика, другой вход .которого соединен с выходом дешифратора.

Вход дешифратора соединен с другим выходом основного вентиля, а выход счетчика соединен с другими входами первого элемента ИЛИ, триггеров, основного и дополнительных вентилей. Другие выходы всех триггеров соединены с соответствующими входами оконечного блока. выход которого является выходом устройства.

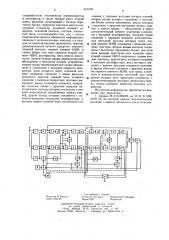

1-1а чертеже изображена структурная электрическая схема поедлагаемого устройства.

Цифроаналоговый корреляционный прием«ик содержит в основном канале последовательно соединенные перемножитель 1 и интегратор 2, а также первый ключ 3, второй ключ 4, выходом соединенный с входом порогоього блока 5, генератор 6 тактовых импульсов, опорный генератор 7, основной элемент задержки 8, основной вентиль 9, счетчик 10, оконечный блок 11, накопитель

12, триггер 13, дополнительный элемент задержки 14, дополнительный вентиль 15, нервый элемент ИЛИ 16, а также общие для всех каналов второй элемент ИЛИ 17, дешифратор 18, блок поиска максимума 19.

Первые входы перемножителей I объединены и являются входом устройства. Вторые входы перемножителей 1 также объединены и соединены с входом опорного генератора 7, вход которого через основной элемент задержки 8 соединен с одним выходом основного вентиля 9. Г1ервый вход вентиля 9 соединен с выходом генератора 6 тактовых импульсов, Выход основного элемента задержки 8 соединен также с другими входами интеграторов 2, выходы которых соединены с входами параллельно соединенных ггервых ключей 3. Другие входы ключей 3 соединены с соответствующими выходами дешифратора 18, а их выходы через накспители 12 соединены с первыми входами вторых ключей 4. Вторые входы ключей 4 соединены с выходами блока 19 поиска максимума, входы которых соединены с другими выходами вторых ключей 4, а третьи входы — объединены и через дополнительный элемент задержки 14 соединены с выходом дешифратора 18, который также соединен с первыми входами дополнительных вентилей 15.

Выходы вентилей 15 через первый элсме«г ИЛИ 16 соединены с первыми входами триггера 13; вторые входы когорых соединены с выходами порогового блока 5. При этом одни выходы триггеров 13 всех каналов чеРез второй элемент ИЛИ !7 соединены с одним входом счетчика 10, другой вход которого соединен с выходом дешифратрра

18. Вход дсшифраторз !8 соединен с другим выходом основного вентиля 9, а выход счетчика 10 соедичен с другими входами первого элемента ИЛИ 16, триггеров 13, основного и дополнительных вентилей 9, 15. Другие выходы всех триггеров 13 соединены с соответствуюц!ими входами оконечного блока 11, выход которого является выходом устройства.

Устройство работает следующим образом, Генератор 6 тактовых импульсов через открытый основной вентиль 9 и основной l5 элемент задержки 8 запускает огорный генератор 7 и интеграторы 2. В момент окончания первого цикла интегрирования, импульсами по временной оси через открытый основной вентиль 9 и дешифратор 18 очередной импульс генератора 6 замыкает первые ключи 3, передавая напряжение, накопленное на интеграторах 2, в накопители 12.

Этог же сигнал через дополнительный элемент задержки 14 замыкает вторые ключи 4,. подавая напряжения с выходов накопителей д 12 на блок 19,)оиска максимума. При этом напряжение на накопителях rre разрушается.

С выхода блока !9 импульсный сигнал открывает один из вторых ключей 4, включенных на выходе накопителя !2, с макси30 мальным значением напряжения, подавая напряжение соответствующего накопителя на пороговый блок 5. Если напряжение превышает установленный порог, то в соответствующий триггер !3 записывается «I».

Следующий импульс цикла с генератора з 6 через дешифратор 18 повторяет ту же операцию по отношению к первым ключам 3, накопителям 12, вторым ключам 4, блоку поиска максимума 19, пороговым блокам

5 и триггерам 13 . Количество импульсов генератора 6 в цикле равняется числу букв г блоке.

Таким образом, по окончании цикла в каждой группе триггеров 13 может быть записано несколько единиц (от 0 до m, где m — число букв в блоке) . Очевидно, каждый триггер 13 соответствует определенной букве заданного алфавита. Все единицы, записанные в триггерах 13, через второй элеме«1 ИЛИ !7 записываются в счетчик 10.

Если число единиц равно m, счетчик 10 переполняется и выдает запирающий им50 пульс на вентили 15. Этим же импульсом информация в виде единиц, записанных в триггерах 13, считывается с них на оконечный блок 1 через первый элемент ИЛИ 16, и работа устройства по приему информации заканчивается.

Предлагаемое устройство позволяет сократить время обработки информации.

Формула изобретения

Цифроаналоговый корреляционный приемник, содержащий в основном канале по641659

Составитель Г. Серова

Текред О. Луговая Корректор С. Шскмар

Тираж 77.т Подписное

Редактор И. Кароас

Заказ 7543 5G

ЦНИ И ПИ Государственного комитета СССР по делам изобретений и открыл vé

I I 3035, Москва, Ж-35, Раугнская наб, д. 4/5

Филиал ППГ1 «Патент>, г. Ужгород, ул. Проектная, 4 следовательно соединенные перемножитель и интегратор, а также первый ключ, второй ключ, выходом соединенный с входом порогового блока, генератор тактовых импульсов, опорный генератор, основной элемент задержки, основной вентиль, счетчик, оконечный блок, отличающийся тем, что, с целью сокращения времени обработки информации, введены п дополнительных каналов, а в каждом из каналов введены накопитель, триггер, дополнительный элемент задержки. дополнительный вентиль, первый элемент ИЛИ, а также общие для всех каналов второй элемент ИЛИ, дешифратор, блок поиска максимума, причем первые входы перемножнтелей объединены и являются входом устройства, вторые входы перемножителей также объединены и соединены с выходом опорного генератора,, вход которого через основной элемент задержки соединен с одним выходом основного вентиля, первый вход которого соединен с выходом генератора тактовых импульсов, выход основного элемента задержки соединен -также с другими входами интеграторов, выходы которых соединены с входами параллельно соединенных первых ключей, другие входы которых соединены с соответствующими выходами дешнфратора, а выходы первых ключей через накопители соединены с первыми входами вторых ключей, вторые входы которых соединены с выходами блока поиска максимума, входы которых соединены с другими выходами вторых ключей, а третьи входы — объединены и через дополнительный элемент задержки соединены с выходом дешифратора, который также соединен с первыми входами дополнительных вентилей, выходы которых через пер1п вый элемент ИЛИ соединены с первыми входами триггера, вторые входы которых соединены с выходами порогового блока, при этом одни выходы триггеров всех каналов через второй элемент ИЛИ соединены с одним входом счетчика, другой вход которого соединен с выходом дешифратора, вход которого соединен с другим выходом основного вентиля, а выход счетчика соединен с другими входами первого элемента ИЛИ, триггеров, основного и дополнительных вентилей, при этом

2О другие выходы всех триггеров соединены с соответствующими входами оконечного блока, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспептизе:

l. Заявка № 2151082/09, кл. В 04 В 1/06, 29.01.76, по которой выдано положительное

- решение о выдаче авторского свидетельства.