Регенератор приемника стартстопных телеграфных сигналов

Иллюстрации

Показать всеРеферат

ю64 Ь 67Ь

Ссиоз Советских

Социалистических

Республик (6l) Дополнительное к авт. саид-ву (5Ь) М. Кл.

Н 04 Х. 25/64 (22) Заявлаио 14. 10.76 (2Ь) 2412137/18-09 с присое .диненнем заявки №(23) Приоритет

Государственный коинтет

СССР но делам необретеннй н отнрытнй (53) УЙК 621.396, .62 1.5 (088. 8) Опубликовано 05.01.79Бюллетень № 1

Дата опубликования описания 08.01,79 (12) Авторы изобретения

В. Г. Артемьев и Б. М. Чернобыльский л

) Ра) Заявитель (54) РЕГЕНЕРАТОР ПРИЕМНИКА СТАРТСТОПНЫХ

ТЕЛЕГРАФНЫХ СИГНАЛОВ

Изобретение отчосится к радиотехнике и может быть использовано в системах передачи дискретных сигналов.

Одним из известных стартстопиых регенераторов, используемых для регенерации по форме и длительности посылок стартстопной телеграфной комбинации, является регенератор, содержащий входной, исправляющий и выходной узлы, а также управляемый делитель частоты и счетную схему со спусковым реле для управления упомянутым дели- тв телем (Ь).

Однако известный регенератор нельзя использовать в приемниках стартстопно-синхронных систем для коррекции длительности стоповых посылок.

Наиболее близким техническим решением к предлагаемому устройству является регенератор приемника стартстопных телеграфных сигналов, содержащий формирователь входных сигналов, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты, на управляющий вход которого поданы тактовые импульсы, счетчик и спусковое реле, к другому входу которого подключен выход блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а выход делителя частоты подключен к тактовому входу блока коррекции (2j.

Однако и этот регенератор невозможно применять в приемниках стартстопно-синхронных систем для коррекции длительности стоповых посылок из-за низкой помехоустончивости.

Цель изобретения — повышение помехоустойчивости путем регенерации стоповой посылки телеграфных сигналов.

Для этого в регенератор приемника стартстопных телеграфных сигналов, содержащий формирователь входных сигналов, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты, на управляющий вход которого поданы тактовые импульсы, счетчик и спусковое реле, к другому входу которого подключен выход блока коррекции, причем выход спускового реле подключен к другому входу счетчика, а выход делителя частоты подключен к тактовому входу блока коррекции, введены фазовый дискриминатор, блок

641671 нычмтания, ренерсивный счетчик, блок совпадения и блок эластичной памяти.

Между выходом формирователя входных сигналов и информационным входом блока коррекции включен блок эластичной памяти, выход которого через блок вычитания подключен ко входу фазового дискриминатора и к вычитающему входу реверсивного счетчика. К суммируюшему входу счетчика подключен выход фазового дискриминатора, выход реверсивного счетчика подключен к другому входу блока вычитания и к соответствующему входу блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственно ко входам блока совпадения, выход которого подключен к соат- 18 нетствующему входу блока вычитания и к дополнительному входу делителя частоты.

Выход делителя частоты подключен к соатветству ощему нхаду фазового дискриминатора, причем на управляющие входы фазового дискриминатора и блока эластичной памяти поданы управляющие импульсы, а на тактовый вход блока вычитания соответственно тактовые импульсы.

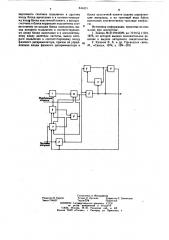

На чертеже приведена структурная электрическаг схема предложенного регене- 25 ратора.

Регенератар приемника стартстопных телеграфных сигналов содержит формирователь входных сигналов 1, на управляющий вход которого поданы управляющие импульсы, и последовательно соединенные делитель частоты 2, на управляющий вход которого поданы тактаные импульсы, счетчик 3 и спусковое реле 4, к другому входу которого подключен выход блока коррекции 5. Выход спускового реле 4 подключен к другому входу счетчика 3, а выход делителя частоты 2 подключен к тактовому входу блока коррекции 5.

Регенератор также содержит фазовый дискриминатор 6, блок вычитания 7, реверсивный счетчик 8, блок совпадения 9 и блок

4С эластичной памяти 10. Между выходом формирователя входных сигналов 1 и информаUHoHHblM olla 0M I5 0ll EoppPKH,èH 5 включен блок эластичной памяти 10, выход которого через. блок вычитания 7 подключен ко входу фазового дискриминатора 6 и к вычитающему входу реверсивного счетчика 8.

К суммирующему входу счетчика 8 подключен выход фазового дискримйнатора 6, выход реверсивного счетчика 8 подключен к другому входу блока вычитания 7 и к соответствующему входу блока эластичной памяти 10. Выходы счетчика 3 и блока коррекции 5 подключены соответственно ко входам блока совпадения 9, выход которого подключен к соответствующему входу блока вычитания 7 и к дополнительному входу делителя частоты 2. Выход последнего подключен к соответствующему входу фазового дискриминатора б, причем на управляющие входы фазоваго дискриминатора 6 и блока эластичной памяти 10 поданы управляющие импульсы, а на тактовый вход блока вычитания 7 соответстнен но та ктовые и м пул ьсы.

Регенератор работает следующим образом.

В стоповом положении регенератора счетчик 3 заблокирован н нулевом состоянии управляющим сигналом с выхода спускового реле 4, которое находится в стоповом положении. Кроме того, реверсивный счетчик 8 находится в нулевом состоянии, а управляемый делитель частоты 2 делит частоту входных тактовых импульсов в К раз так, чтобы период следования выходных тактовых импульсов был равен длительности элементарной посылки хр

В формирователе входных сигналов 1 с помощью управляющих импульсов из группового многоканального сигнала импульсной стартстопно-синхронной системы выделяется сигнал данного канала и с помощью этих же упранляюгцих импульсов, период следования которых (xg, записывается в блок эластичной памяти 10. С выхода блока 10 сигнал с помощью блока коррекции 5 считывается в моменты прихода тактовых импульсов на вход этого блока благодаря чему осуществляется коррекция длительности посылок принимаемого сигнала.

Коррекция длительности стоповой посылки осуществляется при помощи счетчика 3, спускового реле 4, блока совпадения 9 и управляемого делителя частоты 2. В момент считывания в блоке коррекции 5 стартовой посылки срабатывает спусковое реле 4 и разрешает рабату счетчика 3, подсчитывающего количество считывающих (выходных тактовых) импульсов, начиная с первой (стартовой) посылки в стартстопной комбинации.

После подсчета числа импульсов, равного минимальному числу посылок в стартстапнай комбинации, на выходе счетчика 3 ноянляется сигнал, подаваемый на вход блока совпадения 9. Если на другой вход блока совпадения 9 н этот момент с выхода блока коррекции 5 поступает столовая полярность, то с выхода блока совпадении 9 подается сигнал на управляющий вход управляемого делителя частоты 2 и увеличивает ега коэффициент деления частоты до величины L>K так, чтобы следующий считывающий (выход ой тактовый). импульс был выработан через интервал т, >ср. Затем коэффици-. ент деления частоты управляемого делителя частоты 2 возвращается к прежнему значению К, что обеспечивает удлинение стоповой посылки íà Ьт = ц — xe, Величина L выбирается таким образам, чтобы длительность стартстопного цикла на выходе регенератора не превышала минимально допустимую длительность стартстопного цикла на входе стартстопна-синхронной системы.

Выходной сигнал счетчика 3 одновременно с поступлением на вход блока совпа64!6?!

Составитель А. Меньшикова

Редактор И. Карпас Техред О. Луговая Корректор Е. Личинская

Заказ 7544/57 Тираж 7Я Подписное

0НИИПИ Государственного комитета СССР по делам изобретений и открытий

1 ЗОЗЬ, Москва, Ж-35. Рву шская нвб., д. 4/5

Филиал ППП «Патент>. г. Ужгород, ул. Проектная, 4 версивиого счетчика подключен к другому входу блока, вычитания н к соответствующему входф блока эластичной памяти, а выходы счетчика и блока коррекции подключены соответственйо ко входам блока совпадения, выход которого подключен к соответствующему входу блока вычитания и к дополнительному входу делители частоты, выход кото.рого подключен к соответствующему входу фазового дискриминатора, причем на управляющие входы фазового дискриминатора н блока эластичной памяти поданы управляющие импульсы, а на тактовый вход блока

1 вычитания соответственно тактовые импульсы.

Источники информации, принятые во внимание при экспертизе:, 1. Заявка l6 2149443@9, кл. Н 04 Q !1 04, 1975, по которой выдано положительное решение о выдаче авторского свидетельства.

2. Ушаков В. А, и др. Проводная связь.

М., «Связь», 1974, с, 199 — 200.