Устройство оптимального регенератора

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

1841 (E1) К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное к авт. свид-ву № 534160 (22) Заявлено 12.07.74 (21) 2047289/18-09 с присоединением заявки №вЂ” (23) Приоритет—

Орубликовано 15.04.80. Бюллетень № 14

Дата опубликования описания 25.04.80 (51) М. Кл2.

Н 04 1. 5/12

Н 04 L 27/22

Государствеииый комитет (53) УДК621.394..62 (088.8) по делам изобретений и открытий (72) Автор изобретения

О. Н. Порохов (71) Заявитель

Центральный научно-исследовательский институт (54) УСТРОЙСТВО ОПТИМАЛЬНОГО РЕГЕНЕРАТОРА

Изобретение отноится к технике связи и может использоваться для передачи цифровой информации.

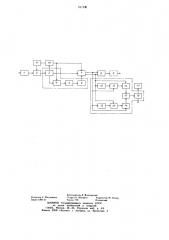

По основному авт. св. ¹ 534160 известно устройство оптимального регенератора, содержащее последовательно соединенные узел согласования с линией связи, усилитель, оптимальный фильтр обнаружения двухуровневого сигнала на интервале двух соседних рабочих посылок, двухполупериодный выпрямитель, узел выделения частоты рабочих посылок, формирователь коротких 1о импульсов, решающий узел, формирователь регенерированного сигнала, узел ввода сигнала в линию связи, также формирователь напряжения оптимального порога, соединенный с оптимальным фильтром обнаружения двухуровневого сигнала на интервале двух соседних рабочих посылок, решающим узлом и через узел автоматической регулировки усиления с усилителем; один из выходов оптимального фильтра обнаружения двухуровневого сигнала на интервале двух соседних рабочих посылок подключен к входу решающего узла, двухполупериодный выпрямитель соединен с выходом формирователя напряжения оптимального порога, з формирователь регенерированного сигнала выполнен, например, в виде триггера раздельным запуском.

Однако в известном устройстве не обеспечи вается контроль работы регенератора.

Цель изобретения — обеспечение контроля работы регенератора путем обнаружения ошибок при регенерации цифрового сигнала.

Предлагаемое устройство отличается от известного тем, что в него дополнительно введены два канала обнаружения ошибок, каждый из которых состоит из последовательно соединенных линий задержки, триггера и элемента И, последовательно соединенные элемент ИЛИ, выходной триггер и индикатор ошибок, при этом каждый выход решающего узла подключен к входу линий задержки и к другому входу элемента И одного канала обнаружения ошибок и к соответствующему входу триггера другого канала обнаружения ошибок, причем выходы элементов И обоих каналов обнаружения ошибок подключены соответственно к входам элемента ИЛИ.

Н а чертеже изображе на структурная электрическая схема предлагаемого устройства.