Арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления

Иллюстрации

Показать всеРеферат

»»642677

Союз Соввтскми

Социалмсткчвскии

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЙТВЛЬСТВУ (61) ДОполнительное к авт. свид-ву (22) ЗаЯвлено 28.06.76 (21} 2378355/18 24 с присоединением заявки № (23) Приоритет

Опубликовано 15.01„79.Бюллетень № 2

Дата опубликования описания 19,01.79 (51) М, Кл.

5 05 В 15/00

G 06 1е 15/20

Государственный комитет

СССРоо делам изооретений и открытий (53) УДК 681.325..5(088.8) Б. Н. Петров, Н. П. Колпакова, Ю. М. Гусев, В. А. Семеран, Б. Г. Ильясов, А. И. Иванов, Ю. М. Ахметов, Ю. С. Кабальнов н Р. М. Гареев (72) Авторы изобретения

Московский ордена Ленина авиационный институт имени Серго Орджоникидзе и Уфимский авиационный институт имени Орджоникидзе (71) Заявители (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ИИФРОВОГО ВЫЧИСЛИТЕЛЯ

ДЛЯ САМОНАСТРАИВАЮЩИХСЯ СИСТЕМ АВТОМАТИЧЕСКОГО

УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике.

Известно арифметическое устройство для обработки больших массивов информации в реальном времени, в состав которого входят несколько связанных между собой уровней камеры н блоков обработки, соединенных с отдельными блоками управления (l).

Однако это устройство не может быть использовано для работы в специализированныхх системах, в которых определяется текущая импульсная переходная функция (ИПФ} системы и сравнивается с требуемой, ИПФ, затем в функции этого разностного сигнала формируется сигнал самонастройки, воздействующий на параметры регулятора системы с целью приближения текущей ИПФ к требуемой ИПФ системы управления.

Из известных устройств наиболее близким по технической сущности к предложенному изобретению является устройство, которое содержит узлы умножения и применяется в составе системы, включающей преобразователь аналог-код, запоминающий блок, преобразователь код-аналог, управляющие входы которых соединены с выходом блока управления, причем вход системы соединен с выходом датчика управляемой координаты системы, а выход подключен к блоку постройки параметров регулятора (2).

Недостатком известного. арифметического устройства является малая скорость выл деления сигнала самонастройки, обусловленная функциональной схемой. Алгоритм его работы основан на решении интегрального уравнения Винера-Хопфа. Устройства, реализующие алгоритм решения этого уравне- ния, дают низкую точность, что связано с некорректностью задач данного типа.

Целью изобретения является увеличение быстродействия и точности выделения сигнала самонастройки при наличии помех.

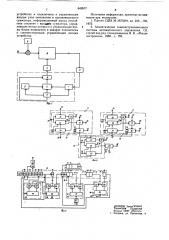

Поставленная цель достигается тем, что устройство содержит блок возведения в квадрат, выход которого соединен со входом сум- матора, и блоки выделения составляющих ошибки, каждый из которых вклю ает накап. ливающий сумматор, формирователь дополнительных кодов, первый вход которого соединен с выходом узла умножения, выход подключен к первому входу накапливающе го сумматора, выход которого соединен с выходом блока выделения составляющих ошибки и с соответствующим входом блока воз642677

Формула изобретения

45 узлов.12. По сигналу с ячейки 4 -6 осуществляется передача кодов из регистров множителя в сумматоры, если младший разряд регистра множителя равен «l», производится поразрядное суммирование и запись «1» в счетчик логического узла 45. По сигналу с ячейки 41-7 осуществляется сдвиг регистров множителя и сумматоров на один разряд вправо, запись «1» в ячейку 41-6 блока управления, если показания счетчика логического узла 45 меньше числа К,, соответствующего числу разрядов кодов чисел. Сигнал с ячейки 41-7 осуществляет запись «1» в ячейку 41-8 и в счетчик логического узла 46, если. показание счетчика логического узла 45 равно К>. Таким образом, за К, тактов сигналами с ячейки 41-7 осуществляется перемножение чисел, записанных в регистрах .узлов 12. По сигналу с ячейки 41-8 осуществляется вывод кода произведений из сумматора узлов умножения 12 в накапливающие сумматоры 18. При этом, если знаки умножаемых чисел противоположны, то с помощью.формирователей дополнительных кодов

17 в накапливающие сумматоры 18 код произведения подается в обратном коде, а в случае совпадения знаков этих чисел — в прямом коде. Сигнал с ячейки 41-8 записывает «1» в ячейку 42-2, если показание счетчика логического узла 46 меньше числа М, и осуществляет запись «1» в ячейку 41-9, .если показание счетчика логического узла 46 равно N.

Сигнал с ячейки 41-9 считывает сигнал с первой ячейки распределителя импульсов

42, осуществляя передачу кода накапливающего сумматора 18 (первого из блоков 11) в регистры блока 19 возведения в квадрат, и подготавливает цепь установки «О» этого накапливающего сумматора 18. По сигналу с ячейки 41-10 осуществляется установка «О» вышеупомянутого накапливающего сумматора 18. 11епи установки «О» остальных накапливающих сумматоров заперты до прихода соответствующих сигналов с распределителя импульсов 42. По сигналу с ячейки

41-11 осуществляется передача кодов из регистра множимого блока 19 возведения в квадрат в сумматор, если младший разряд регистра множителя равен « l », и осуществляется поразрядное суммирование. По сигналу с ячейки 41-12 осуществляется сдвиг .регистра множителя и сумматора. блока 19 возведения в квадрат иа один разряд вправо, осуществление записи « i» в ячейку 41-! блока управления, если показание счетчика логического узла 47 меньше числа К-,, соответствующего числу разрядов кодов чисел, либо осуществление записи «1» в ячейку

41-13, если показания счетчика логического узла 47 равно К . Таким образом, за К> тактов с ячейки 41-12 осуществляется возведение в квадрат чисел, записанных в регистрах. По сигналу с ячейки 41-13 осуществляется вывод кода произведений из сумматора блока 19 возведения в квадрат в сумматор 20 и запись «1» в счетчик логического узла 48.

По сигналу с ячейки 41-14 осуществляется сброс на «О» регисгров и сумматоров блока 19 возведения в квадрат, запись «1» в ячейку 41-9, сброс на «О» счетчика логического узла 47, через элемент ИЛИ 61, если показания счетчика логического узла 48 меньше N. Этот же сигнал с ячейки 41-14, осуществляет запись «1.» в ячейку 41- !5, если показания счетчика логического узла 48 равно N. Таким образом, если показания счетчика логического узла 48 меньше N, то в следующем такте сигнал с ячейки 41-9 считает сигнал с первой ячейки распределителя импульсов 42, который осуществляет передачу кода накапливающего сумматора (второго из блоков l I ) в регистры блока 19 возведения в квадрат. Таким образом, за N+1 тактов распределителя импульсов 42 в сумматоре 20 оказывается записанным число, 20 соответствующее величине сигнала самонастройки. Сигнал с ячейки 41-15 осуществляет вывод кода сумматора 20 на вход преобразователя 4 код-аналог. Аналоговая величина, соответствующая вычисленному значению сигнала самонастройки, с выхода преобразователя 4 «код-аналог» поступает на вход блока 7 подстройки параметров регулятора.

Блок 7 подстройки параметров регулятора изменяет параметры системы управления с целью приближения их к требуемым.

Арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления, содержащее узлы умножения, отличающееся тем, что, с целью увеличения быстродействия и точности выделения сигнала самонастройки при наличии помех, оно содержит блок возведения в квадрат, выход которого соединен со входом сумматора, и блоки выделения составляющих ошибки, каждый из которых включает накапливающий сумматор, формирователь дополнительных кодов, первый вход которого соединен с выходом узла умножения, выход подключен к первому входу накапливающего сумматора, выход которого соединен с выходом блока выделения составляющих ошибки и с соответствующим входом блока возведения в квадрат, первый информационный вход каждого блока выделения составляющих ошибки соединен с первым информационным входом устройства, с первым входом узла умножения и со вторыми входами формирователя дополнительных кодов и накапливающего сумматора, второй информационный вход —,. соединен со вторым информационным входом устройства, вторым входом узла умножения и третьим входом формирователя дополнительных кодов, управляющие входы — соединены с соответствующими управляющими входами

642677 устройства и подключены-.к управляющим входам узла умножения и наканлнвающего сумматора, информационный выход устройства соединен с выходам сумматора, управляющие входы которого и управляющие вхо- 5 ды блока возведения в квадрат подключены к соответствующим управляющим входам устройства.

Источники информации, принятые во внимание при экспертизе:, 1. Патент США № 3875391, кл. 235 в 156, 1975.

2. Аналитические самонастраивающиеся системы автоматического управления. Сб. статей под ред. Солодовникова В. В., «Машиностроение», 1965., с. 165. р 1ОИ . Подпнс нее

Филиал ППП «Патент» . г Ужгород ул Проектная 4