Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Союз Советсим

Социалистических

Реслублми

ОЛ ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

642842 (6() Дополнительное к авт. свил-ву (22) Заявлено 16.10.74 (21) 2069318/18-09 с присоелинением заявки ¹ (23) ПриоритетОпубликовано 15.01.79.Бюллетень ¹ 2

Дата опубликования описания 18.01.79

2 (51} М. Кл

Н 03 В 3/04

Госяйрстооаныо ком%тот

СССР оо делам озооретоей и открмтик (5З) УДК 621.373.. 42 (088.8) (72) Авторы изобретения B. B. Синьков, В. С. Куменко и М. H. Макаров (7}) Заявитель (54) БИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

Изобретение относится к радиотехнике и может быть использовано в сисгемах автоматики, в приемно-передающих устройствах и в измерительной технике.

Известен цифровой синтезатор частот, содержащий пересграиваемый генератор, к управляющему входу которого подключен выход фильтра нижних частот, а выход перестраиваемого генератора через управляемый делитель частоты соединен с первыми входами первого и второго импульсно-фазовых детекторов, к вторым входам которых подключены выходы первого и второго делителей частоты соответственно, входы которых соединены с выходом генератора опорной частоты, при этом поразрядные входы всех делителей частоты соединены с выходами управляющего блока (lj

Однако в известном устройстве с целью получения малого шага перестройки частоты при высоком значении опорных частот используется несколько контуров фазовой автоподстройки.

Белью изобретения является получение шага перестройки частоты, меньшего чем разность опорных частот на втаб. рых входах импульсно-фазовых детекторовв.

Пля этого в цифровой синтезатор чаотот, содержащий пересграиваемый генератор, к управляющему входу которого подключен выход фильтра нижних частот, а выход перестраиваемого генератора через управляемый делитель частоты соединен с первыми входами первого и второго импульсно-фазовых детекторов, к вторым входам которых подключены выходы первого и второго делителей частоты соответственно, входы которых соединены с выходом генератора опорной частоты, при этом поразрядные входы всех делителей частоты соединены с вЫходами управляющего блока, введены последовательно соединенные цифроанапоговый преобразова тель, сгробирующее устройство .и сумматор, а также пороговый разпичитель, первый и второй григгеры, первое и второе устройства для поразрядного совпадения, выходы которых соединены с установочными входами первого и второго делителей частоты соответственно, при этом выход первого 5 триггера подсоединен к,управляющим входам первого делителя частоты и первого устройства для поразрядного совпадения, Выход второго>-риггера соединен с управляющими Входами второго делителя 1О частоты н второго устройства для поразрчдного совпадения, к выходу управляющего 6J1GKB подключены TBKIKe разрядчые

Входы .. цифроаналогового, преобразователя и первые разрядные входы первого и

ВторОГО устройств t для пОразряднОГО сОВп>адения, Вторые разрядные входы котоВых coeQ>Hнень> с разрядными Выходам>и первого и второго делителей частоты со- ответственно, выход первого делителя частоты соединен -акже с первыми Вхо дами порогового раздичителя, стробирующего устройства и первого триггера, ВихОд BТОрОГО делителя частОты coeQHнен с вторыми Входами порогового различителя и стробирующего ycrpohcraa и с перВь>м ВХОдом Второго триггера Выход порО

I GttotG рази>ичитедя соединен с Вторыми

Входами >Iep ac To и ВторОГО триГГерОВ B

Выходы импуд ьсно-Д!азовых детекторов подсоединень1 к сооrветствующим Входам суь4маropat: ВыхОд которого соединен с

ВХОдом фБяьrpa нижних частОT

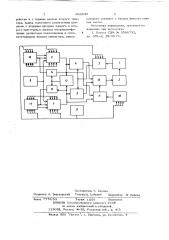

HB чеотеже приВедена структурная электрическая схема cHHTeea rope

4$

Цифровой синтезатор частОт содержит перестраиваемый генератор 1> к управля

ЮЩЕМУ ВХОДУ XorGPOI O ПОДКЛЮЧЕН ВЫХОД фильтра 2, нижних 1 частот,, B ВыхОд пере>

cTpBHBBexGIo reHepBzGpa 1 через управ- о ляемый делитель 3 частоты соединен с первыми Входами IIepBGIO 4 H BropGFG 5 импульснО-фа<ювьзх детекторов, к BropbIM ,входам которь>х подключены выходы перВого 6 и второго 7 делителей частоты соответственно, Входы которых соедине1

:ны с выходом генератора 8 опорной час ,. тОтnI>> tlpH этом поразрядные ВхОды Всех делителей 3, 8 и 7 частоты соединены с

>Выходами управляющего блока 9, последОвательнО соединенные цифроаналоговый преобразователь 1О, стробирующее устpoffcTBG 1 1 H сумматор 1 2, B также по° роговый различитель 13, первый 14 и

Второй 15 триггеры, первое 16 и второе 17 устройства ддц поразрядного соВ. падения, Выходы которых соединены с установочными ВхОдами перВОГО 6 и ВтО рого 7 делителей частотьц при этом выход первого триггера 14 подсоединен к управляющим входам первого делителя частоты 6 и первого устройства для по.разрядного совпадения 16, выход второго триггера 15 соединен с управляющими входами второго делителя частоты 7 и

Второго устройства для поразрядного сов.падения 17, к выходу управляющего бло ка 9 подключены также разрядные входы цифроаналогового преобразователя 10, и первые разрядные входы первого 16 и второго 17 устройств для поразрядного совпадения, вторые разрядные входы которых соединены с разрядными выходами первого 6 и второго 7 делителей частоты, выход первого делителя частоты 6 соединен также C первыми входами порогового раздичителя 13, стробирующего устройства 11 и первого триггера 14, выход второго делителя 7 частоты соединен с вторыми входами порогового различителя 13 и стробирующего устройства

11 и с первым входом второго триггера

15, выход порогового разпичитепя 13 соединен с Вторьпми, Входами первого 14и второго 15 триггеров, а выходы импульсно-ч >азовах детекторов 4 и 5 подсоединены к соответствующим входам сумматора 12, выход которого соединен с входом фильтра 2 нижних частот.

Синтезатор работает следующим образомм.

В первый момент производится задание начальных:Временных ссютношений между сигналами, которое осуществляется установкой управляемого делителя 3 и первого 6 и второго 7 делителей час тоты в начальные состояния управляю:щим блоком B. Это производится с той целью, чтобы в момент начала работы на входах импульсно-фазовых детекторов

4 и 5 импудьс нерестраиваемого генератора 1, прошедший через управляемый делитель 3 с коэффициентом деления l4,, во Времени находидся между опорными импульсами,, сформированными, из сигнала генератора 8 путем деления на первом и втором делителях частоты 6 и 7 с коэффициентами деления, равными со-, ответственно М и И .

На выходе первого импульсно-фазового детектора 4 формируется сигнал с длительностью импульсов, равной Временному рассогласованию опорных импульсов с Первого делителя частоты 6 и поделен ных импульсов перестраиваемого генера тора 1, а на выходе второго импульснофазового детектора 5 формируется сигнал о длительностью импульсов, равной временному рассогласованию между поделенными импульсами перестраиваемого генератора 1 и опорными импульсами с второго делители частоты 7. При суммировании этих сигналов на выходе сумматора 12 образуется сигнал с периодически изменяющейся длительностью положительных и отрицательных импульсов. Ю йа вход сумматора 12, кроме того, подается сигнал цифроаналогового преобразователя 10, прошедший через стробирующее устройство 11. Стробирующее устройство 11 осуществляет стробирование проходящего сигнала на время, равное рассогласованию опорных сигналов, которые подаются на его управляющие входы с выходов первого и второго делителей частоты 6 и 7. При этом в сигнале на выходе сумматора 12 амплитуда положительных импульсов в общем случае не равна амплитуде отрицателы ых импульсов, так как сигнал цифроаналогового преобразователя 1О приводит к увеличению амплитуды одних импульсов и к равнозначному уменьшению амплитуды других.

После фильтрации суммарного сигнала на фильтре 2 управляющее. напряжение, пропорциональное интегралу От настоян ной составляющей суммарного сигнала, поступает на управление перестраиваемым генератаром 3.

B пороговом разпнчителе 13 производится сравнение временных интервалов между анарными сигналами с пороговым, и, когда эти интервалы становятся меньше порогового, осуществляется временной сдвиг опорных. сигналов. Сдвиг осущест- "0 вляется нри наступлении сигналов с первого триггера 14 на управляющие входы первого и второго делителей частоты 6 (7) и первого и второго устройств для поразрядного совпадения 16 (17), выходы и первые разрядные входы которых соединены соответственно со вспомогательными входами и разрядными выходами соответствующих первого и второго делителей частоты 6 (7)..При этом производится разовое уменьшение коэффициента деления первого делителя частоты 6, Фу на К(и увеличение коэффициента

:деления второго делителя частоты 7 N> на К . При этом выходной импульс пер$$ ваго делителя частоты 6 сдвигается влево на К„Та, а второго делителя 7 час-, тоты вправо на К Та, где То- период

2 Ов

42. 6 колебаний эталонного генератора. Сдвинутые выходные импульсы первого 6 и второго 7 делителей частоты возвращают соответствующие первый 14 и второй 15 триггеры в исходные состояния., Предложенный синтезатор частот по сравнению с известным позволяет получить малый шаг перестройки частоты.

Формула изоб ре тения, Цифровой синтезатор частот, содержащий перестраиваемый генератор, к управляющему входу которого подключен и@ход фильтра нижних частот, а выход переетраиваемого генератора через управляемый делитель частоты соединен с первыми входами первого и второго импульснофазовых детекторов, к вторым входам которых подключены выходы первого и второго делителей частоты соответственно, входы которых соединены с выходом генератора опорной частоты, при этом поразрядные входы всех делителей частоты соединены с выходами управляющего блока, а т л и ч а ю шийся тем, что, с целью получения шага перестройки частоты, меньшего чем разность опорных часто на вторых входах импульсно-фазовых детекторов, в него дополнительно введены последовательно соединенные цифроаналоговый преобразователь, ctpoбирующее устройство и сумматор, à также пороговый различитель, первый и второй триггеры, первое и второе устройства для поразрядного совпадения, выходы которых соединены с установочными входами первого и второго делителей частоты соответственно, при этом выход первого триггера подсоединен к управляющим входам первого делителя частоты и первого устройства для поразрядного совпадения, выход второго триггера соединен с управляющими входами второго делителя частоты и второго устройства для поразрядного совпадения, к выходу управляющего блока подключены также разрядные входы цифроаналогового преобразователя и первые разрядные. входы первого и второго устройств для поразрядного совпадения, вторые разрядные входы которых соединены с разрядными выходами первого и второго делителей частоты соответственно, выход первого делителя частоты соединен1;также с первыми входами порогового различителя, стробирующега устройства и первого триггера, Bhtxerr atopoFo делителя часто-.

1 ты соединен с вторыми входами порога« ваго различи теля и стробирующего уст642842

Состави гель Г. Серова

Техред Н. Ьабурка Корректор Л. Небола

Редактор А. Зиньковский

Заказ 7779/53 Тираж 1059 Подписное

llHHHllH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, РауUJcKBsl наб,, Q 4/5

Филиал ППП Патент ", r. Ужгород, ул. Г!роектная, 4 ройства и с первым входом второго триггера, выход порогового различителя соединен с вторыми входами первого и второго триггеров, а выходы импульсно-фазовых детекторов подсоединены к соот- 5 ветствуюшим входам сумматора, выход которого соединен с входом фильтра нижних частот.

Источники инфюрмании, принятые во внимание при экспертизе

1. Патент США № 3588732, кл. 331-2, 28. 06.7 1.