Устройство для передачи данных

Иллюстрации

Показать всеРеферат

QA ИКАНИЕ

ИЗОБРЕТЕН ИЯ

И АВТОРСКОМУ СЗИДВ ИЛЬСаВЖ (61) дополнительное к авт. свиа-ву (22) Заявлено 03.05,76 (2I) 2357478/18 .09 с присоединением заявки № (23) Приоритет

Опубликовано 15 pl 79Бюллетень № 2

Дата опубликования описания 18,01.79

Союз Советсюа

Соцмлистииескик

Республик

««642868

2 (51) М. Кл

Н 04 1 17/02

Я 06 F 3/04

Гаеударственны9 натлнтет

СССР не делан нзебретеннй н атнрь тнй (53) УДК 621.394..6 (088.8) В. М. Антимиров, B Г. Бельцов, Ю. П. Запек

В. ll. Трит,онов и П. С. Шабашив (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах для передачи данных между центральной памятыа и периферийными системами.

Известно устройсгво для передачи данных, содержащее запоминающий блок, связанный через буферный накопитель с периферийным блоком, блок управления, первый выход которого подключен к управляющему входу буферного накопителя, а второй выход — через блок формирования текущего адреса подключен к управляющему входу запоминающего блока, причем управляющий выход периферийного блока подключен к первому входу блока управления, к второму входу которого подключен другой выход блока формирования.текущего адреса, к информационному входу которого и к третьему входу блока .управления подключен выход ттроцесс ора (1$ .

Однако известное устройство не обеспечивает передачу данных без выдачи управляющих команд процессором.

Целью изобретения является устранение перерывов в передаче данных при возникновении отказов процессора.

Для этого в устройство для передачи данных, содержащее запоминающий блок, связанный через буферный накопитель с периферийным блоком, блок управления, пер1В вый выход которого подключен к управляющему входу буферного накопителя, а второй выход - через блок формирования текущего адреса подключен к управляющему входу запоминающего блока, причем управляющий выход периферийного блока подключен к первому входу блока управления, к второму входу которого по подключен другой выход бпока формирс ванин текущего адреса, к информационному входу которого и к третьему входу:. блока управления подключен выход процессора, введены блок контроля временного интервала и формирователь an42868

6 реса автоматического считывания, к информационным входам которых подключен выход процессора, к управляющему входу которого подключен третий выход блока управления, четвертый выход которого подключен к управляющему входу формирователя адреса автоматического очитывания, выход которого подключен к дополнительному информационному входУ блока формирования текущего адреса, а пятый выход блока управления подключен к управляющему входу блока контроля временного интервала, выход которого подключен к четвертому входу блока управления.

В таком устройстве перерывов в передаче данных при отказах процессора не набл!одается.

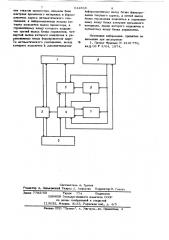

На чертеже приведена структурная электрическая схема устройства.

Устройство для передачи данных содержит запоминающий блок 1, связанный через буферный накопитель 2 с периферийным блоком 3, блок управления 4, первый выход которого подключен к управляющему входу буферного накопителя 2, а второй выход - через блок формирования 5 текущего адреса подключен к управляющему входу запоминающего блока 1, причем управляющий выход периферийного блока 3 подключен к первому входу блока управления 4, к второму входу которого подключен другой выход блока формирования 5 текуmer о адреса, к информационному входу которого и к третьему входу блока управления 4 подключен выход процессора 6, введенные блок контроля 7 временного интервала и формирователь 8 адреса автоматического считывания, к информационным входам которых подклю чеи выход процессора 6, к управляющему входу которого подключен третий выход блока управления 4, четвертый выход которого подключен к управляющему входу формирователя 8 адреса автоматического счичъ вания, выход которого подключен к дополнительному информационному входу блока формирования 5 текущего адреса, а пятый выход блока управления 4 подключен к управляющему входу блока контроля 7 временного интервала, выход которого подключен к четвертому входу блока управления 4.

Устройство для передачи данных работает следующим образом.

Устройсаьо для передачи данных работает в двух режимах: в режиме передачи данных по командам процессора и в режиме автоматического списывания.

В режиме передачи данных работа начинается с посылки процессором 6 последовательности к оманд поочередно:

- в блок управления 4 посылается информация о виде обмена и номера периферийного блока 3;

- в блок формирования 5 записывает ся адрес зоны запоминающего блока 1, выделенной для передачи или приема данных;

Ф вЂ” в блок контроля 7 записывается контрольный интервал времени;

- в формирователь 8 адреса вводятся данные о начальном адресе и размере массива, подлежащего выводу в периферийное устройство 3 в автоматическом режиме.

После получения информации о виде обмена блок управления 4 посылает признак обращения к запомчнающему блоку 1 в процессор 6 и в блок формирования 5. Блок формирования 5 вырабатывает и посылает в запоминающий блок 1 сигналы обращения и код адреса. Между буферным накопителем 2 и запоминающим блоком 1 происходит передача данных, после чего блок управления 4 снимает признак обращения к запоминающему блоку 1. К этому моменту буферный накопитель 2 содержит данные для передачи в периферийный блок 3, В зависимости от вида обмена, заданного блоку управления 4, передача в периферийный блок 3 и списывание данных из него происхсдит по сигналу запроса, поступающему иэ периферийного блока 3 нли по сигналу, формируемому блоком управления 4. Блок управления 4 посылает в буферный накопитель 2 команду, по которой происходит обмен между буферным накопителем 2 и периферийным блоком 3. Затем блок управления 4 посылает в процессор 6 и в блок формирования 5 признак обращения к запоминающему блоку 1, по которому текущий адрес изменяется на единицу и вырабатываются сигналы обращения и код адреса, т.е. производится очередной цикл обмена аналогично описанному вьппе.

После окончания последнего цикла передачи заданной зоны блок формирования 5 посьшает в блок управления 4 признак последнего слова массива, по которому блок управления 4 прекращает ,формировать признаки обращения к запоминаюшему блоку 1 и пось«лать команды в буферный накопитель 2.

Устройство для передачи данных переходит в состояние ожидания следующей посылки последовательности команд из процессора 6, после получения которой режим обмена повторяется.

Для разрешения конфликт««ой ситуации одновременного обращения к запоминающему блоку 1 и к процессору 6, процес- «О сор 6, после получения из блока управления 4 признака обра«пения к запоминающему блоку 1 блокирует собственное абращение к запоминающему блоку 1. Йля этого в процессоре 6 может, например, приостанавливаться на время обращения формирование последовательности синхроимпульсов или же задерживаться выполнение микрооперации обращения к запоминающему блоку 1, если признак обращения устройства для передачи данных совпадает с данной микрооперацией.

Одновременно с передачей данных между запоминающим блоком 1 и периферийным блоком 3, блок контроля 7 по меткам времени, поступающим нз блока управления 4, считает контрольный временной интервал, счет продолжается н в состоянии ожидания, При правильной работе процессора 6 заданная длительность кбнтрольного временного интервала заведомо больше интервала времени между обращениями процессора 6 к устройству для передад чи данных, В режим автоматического списывания устройство переходит по сигналу конца временного интервала, посланного блоком контроля 7 в блок управления„4. Этот сигнал вырабать«вается, 46 если интервал времени между соседними обращениями процессора 6 к устройству для передачи данных превышает длительность заданного временного нн»

45 тервала. Первый контрольный интервал формируется блоком контроля 7 схемно, при включении системы. В дальнейшем его значение может заменяться кодом, посылаемым процессором 6 в блок контроля 7 при обращении к устройству для передачи данных. При получении сигнала на переход в режим автоматического списывания блок управления 4 посылает в формирователь

8 адреса признак передачи адреса. Формирователь 8 адреса вырабатывает код и передает его в блок формирования 5, Первоначальный адрес формируется схемно при включении устройства и может затем заменяться кодом, посылаемым процессором 6 в формирователь 8 адреса. После йередачи адреса автоматического списывания блок управления 4 посылает в блок формирования 5 и в процессор 6 признак обращения к запоминающему блоку 1 и весь цикл обмена проводится аналогично режиму передачи данных по командам процессора. После окончания передачи в meриферийный блок 3 содержимого зоны автоматического списывания, блок формирования 5 посылает в блок управления 4 признак последнего слова массива. При совпадении этого признака с

««риэ««аком конца контрольного интервала времени режим повторяется. После получения от процессора 6 соответствующей последователы ости команд устройство переходит в режим передачи данных по командам процессора.

Использование предложен. ого устройства для передачи данных позволяет передавать информацию из запоминаюп его блока вь"числительной машины в периферийный блок в автоматическом режиме без управления со сторонь«процессора.

Это позволяет выполнить ряд дополнительных задач, например контроля и диагностики отказов процессора. Рещение подобных задач является особенно важным при отработке управляющих си стем с ограниченным доступом или без доступа к оборудованию.

Форм.ула изобретения

Устройство для передачи данных, содержащее запоминающий блок, связанный через буферный накопитель с периферийным блоком, блок управления, первый выход которого подключен к управляющему входу буферного накопителя, а второй выход — через блок формирования текущего адреса подключен к управляю«цему входу запоминающего блока, причем управляюц«нй выход периферийного блока подкчючен к первому входу блока управления, к второму входу которого подключен другой выход блока формнрования текущего адреса, к информационному входу которого и к третьему вхэду блока управления подключен выход процессора, о т л н ч а ю щ е е с я тем, что, с целью устранения перерывов в передаче данных при возннкнове642868 8 информационному влоду блока формир ввния текущего адреса, а пятый выход блока управления подключен к управляющему входу блока контроля временного

Ю интервала, выход которого подключен к четвертому входу блока управлении.

7 нии отказов процессора, введены блок контроля временного интервала и форми рователь адреса автоматического счичмвания, к информвлионным входам которых подключен выход процессора, к управляхкпему входу к оторого подключен третий выход блока управления, четвертый выход которого подключен к уиравлякищему входу формирователя адреса автоматического считывания, выход 19 которого подключен к дополнительному

Источники информации, принятые во внимание при экслертиэе

1. Патент Франции N 23.91770, an.Q 06 Г 3/04, 1974.

Составитель А. Грачев

Редактор А. Зинькаеский Техред Л. Алферова Корректор И. Гоксич

Заказ 7782/55 Тираж 774 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва. Ж-35, Раушскаи наб., д. 4/5

Филиал НПП Патент", г. Ужгород,,ул. Проектная, 4