Устройство для связи запоминающего и арифметического устройств

Иллюстрации

Показать всеРеферат

Союз Соеетскмн

Соцналнстмческия

Реслублмн

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВЛЛЬСТВУ (и) 643878 (61) Дополнительное к авт. свил-ву(51) М. Кл.

G 06 Р 13/06 (22) Заявлено 05.08.76(21),2392718/18-24 с присоединением заявки № " (23) ПриоритетГесударетевннвй квинтет

СССР аа данам нзобретвнкй в юткрнтнй

Опубликовано 25.01.79.Бюллетень Ж 3

Дата опубликования описания28.01.79 (53) УДК681.325 (088.8) В. Г. Псарев, Ю. В. Пшеничный, В. П. Тише (72) Авторы изобретения (73) Заявитель (54) УСТРОЙСТВО ДЛЯ СВЯЗИ ЗАПОМИНАЮЩЕГО

И АРИФМЕТИЧЕСКОГО УСТРОЙСТВ

Изобретение относится к области вы числжельной техники, в частности, к устройствам для связи запоминающего и арифметического устройств и может быть использованб при построении систем обработки данных на базе мини-ЭВМ.

Известно устройство P), позволяющее осуществлять связь запоминающего и арифметического устройств, содержащее регистр команд,. первътй-четвертый блоки связи, коммутатор, регистр базового адреса, два сумматора и индексный регистр.

Недостаток устройства состоит в том, что оно не позволяет управлять форматом выходной информации запоминающего устройства.

Наиболее близким к кюбретенню по технической сущности и достигаемому результату является устройство nas связи запоминающего и арифметического устройств (2), содержащее дешифратор, выходы которого соединены со входами .шифратора и коммутатор, выполненный в виде групп элементов H и группы эле ментов HJIH, причем выходы одноимен» ных элементов И групп соединены со входами соответствующего элемента

ИЛИ.

Недостатком устройства являются повышенные затраты оборудования и

or p8íè÷åíHûå функциональные воэможности, поскольку оно не обеспечивает согласования работы сопрягаемых устpDRcTB в случае различия форматов адpecos и данных.

Цель изобретения - сокращение обору» дования и расширение фунхциональных воэможностей путем организаций режима работы при форматах адреса и данных зацоминаюшего устройства, превышаю тних форматы адреса и данных арифме, тического устройства.

Поставленная цель достигается тем, что устройство содержит регистр номе ра массива и регистр зоны, причем казк дая группа информационных входов ус аройства соединена с первыми входами

643878 элементов И соответствующей группы элемеМгов И, вторые входы элементов

И каждой группы соединены с соответствующими разрядными выходами регистра зойы, выходы элементов ИЛИ соединены с групной информационных выходов устройства, группа адресных входов устройства соединена со входами p,åøèôðàтбре и является первой группой адгеснйХ выходов устройства, а второй груп. пой адресных вь..ходоВ устройства являются выходы регистре номера массива. первая и вторая группы выходов шифраторе соединены с разрядными входами соответственно регистра номера массива и регистра эоны.

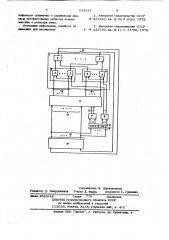

Структурная cxvма устройства приведена на чертеже.

Устройство для связи запоминающего и арифметического устройств. содержит коммутатор 1, выполненный в виде группы элементов ИЛИ 2, групп 3 и 4 элементов И 5, регистр 6 зоны, регистр 7 номера массива, дешифратор 8, шифратор 9; Кроме того, на чертеже позициями 10 и 11 обозначены соответственно арифметическое устройство и запоминаямцее устройство, позицией 12первая группа адресных выходов устройстве, позицией 13 - вторая группе адресных выходов устройства, позицией

14 - группа едресных входов устройства, позицией 15 - группа информационных выходов, позициями 16, 17 груп цы информационных входов устройства.

Устройство работает следукицим образом.

Вся память запоминающего устройся ва (ЗУ) 11 делится на массивы (по адресам) и зоны (по разрядам информации}. Выбор массива определяется состоянием регистра 7, управляюшим старшими разрядами адреса запоминающего устройства 11, и состоянием регистра

6, который управляет зоной информации.

Весь массив адресов, формируемых арифметическим устройством (АУ) 10 разделяется на два. массива. Первый цодмассив адресов предназначен для рабочих программ вычислительной машины (текущие" адреса). Второй под месив адреса, являющиеся кодами управлений, предназначенные для перек лкиения, магистралей:устройстве адресации к памяти (фиксированные адреса}.

Во времй работы вычислительиой машины «текущие» и "фиксированные" ад10 признаком для контроля правильного под 5 ключения участка ЗУ 11.

55 реса поступают в запоминающее устройство 11 и на вход дешифретора 8. При составлении программ учитывается, что формирование и выдача в ЗУ 11 "текущих адресов вызывает появление в

АУ 10 рабочей информации. фиксиро ванный адрес выполняет две функции.

Во-первых, этот адрес воспринимается дешифратором 8, для подключения требуе мого участке памяти ЗУ 11 к арифметическому устройству 10. l3o-вторых, информация, которая считается по фиксированному" адресу в АУ 10 является

Алгоритм построения программ вычиолительной мешины следующий:

-АУ 10 формирует фиксированный» адрес, который поступает в устройство, вызывая переключение магистралей, и в ЗУ 11, где осуществляет контроль правильности подключения участка проиъ. рамм ЗУ 11;

Ф

- далее исполняются программы, расположенные в подключенном участке памяти ЗУ 11.

При переходе программ на другой участок памяти ЗУ 11 указанный алгоритм повторяется.

ЗУ 11 реагирует на адреса, посту пающие из АУ 10 и регистра 7.. Адрес на выходе регистра 7 является безо вым адресом АУ 10, Информация на этот регистр в виде кода фиксированного адреса устанавливается перед ис» полнением рабочих программ (текущих

4 адресов). Регистр 6 "гакже устанавливается в определенное состояние кодоМ

«фиксйровенного«адреса. При этом сигнал с этого регистра разрешает прохож дение через коммутатор 1 в АУ 10 ии» формации с выбранной зоны ЗУ 11. Îcтавшиеся разряды информации ЗУ 11 блокируются коммутатором 1.

Блокировка изменейия состояния ре» гистра 6, 7 устройства выполняется программным способом.

Приведем описание работы устройст ва адресации к памяти иа следующем числовом примере.

Пусть разрядность адресных и иифор мационных магистралей АУ 10 и ЗУ 11 такова, что

- адреса АУ содержат 13 разрядов, - информаций AY содержит 16 разряд оь«

- адреса ЗУ имеют 18 разрядов, - информация ЗУ имеет 64 разряда;

643878

Из всего диапазона адресов АУ (00000й-17777й ) последние адреса, 17770 -17777е, определим как фиксированные, остальные адреса "теку шие".

Вся память ЗУ разделяется на массивы по адресам:

000000 - 017777й первый массив

020000я - 037777в второй массив, ° ° ° ° ° ° ° . ° ° ° ° ° ° ° ° °

600000в - 777777< т -й массив, н зоны по разрядам информации:

0- 15 разряды - первая эона, .16-31 разряды - вторая зона, 32«47 разряды - третья зона, 48-63 разряды - четвертая эона.

Выбор массива определяется состоянием регистра 7, который содержит стар. шие адреса ЗУ 11, а выбор зоны информации определяется состоянием регистра:

6, который выбирает требуемую зону информации.

В исходном состоянии на выходах

АУ 10, ЗУ 11 коммутатора 1 сигна лы отсутствуют. При поступлении с

АУ 10 фиксированного адреса (на, пример, 17771> «) последний воспринимается дешифратором 8 и на регистр ры 6, 7 записываются коды, позволяюшие иэ ЗУ 11 выбрать, например, первый ьмссив адресов {QQQQQQ -01777 ) и подключить в АУ 10, нвщимер, четЭ вертую зону информации Зу 11.

Кроме этого из ЗУ 11 в арифметическое устройство 10 поступит информв ция, записанная в ячейке .с адресом, равным "фиксированному „которая воспримется АУ 10 как контрольная информация для оценки правильного nogключения выбранного массива и зоны памяти ЗУ ll. Далее производится совместная работа АУ 10 н ЗУ 11 по рабочим программам, расположенным в выбранном участке памяти.

Таким обрезом, изобретение позволяет сократить затраты оборудования за счет исключения регистров младших рюрядов и дешифратора коммутатора, в также расширить функциональные воэ» можности известного устройства. Тем самым изобретение позволяет. данному

АУ работать запоминашцим устройством большой емкости. Обшее увеличение обьема памяти может быть рассчитано следующим обрезом.

Емкость за оминаккцего устройства цифровой вычислительной машины с edраэрядной адресной магистралью и Пц, - разрядной информационной магнст. рвлью составляет

Ч = 2 4 разрядных слов.

Применение запоминаюшего устройства большой емкости, имеюйего,например, ФО - разрядную адресную магистраль и NU - разрядную информационную магистраль, где nO> > rnO< и щц у пц„позволяет увеличить объем памяти в вычислительной машине до

Ч2 > Ч1 К (К2 разрядных слов, 2 à -та 1 где К = р 1 - количест

2tl а„ во массивов эапоминаюшего устройства по адресной магистрали (емкость памяти каждого иэ массивов равно емкости штатной памяти цифровой вычислительной машины, то есть И ); я

К 2. „ 1- количество abH запоминающего устройства по информапионной магистрали.

Обшее увеличение объема памяти составит:

К= к к, Ч1 формула изобретения

Устройство для связи запоминающего и арифметического устройств, содержашее дешифратор, выходы которого соединены со входами шифратора и коммутатор, выполненный в виде групп элементов И и группы элементов ИЛИ, при чем выходы одноименных элементов И групп соединены со входами соответствуюшего элемента ИЛИ, о т л и ч вю ш е е с я тем, что, с целью сокрашения оборудования и расширения функциональных воэможностей нутом органи звции режима работы при фоомвтах адреса и данных запоминающего устройства, превышающих форматы адреса н данных арифметического устройства,оно содержит регистр номера массива и регистр зоны, причем каждая грунна информационных входов устройства соединена с первыми входами элементов И соответствующей группы элементов И, вторые входы элементов И каждой группы соединены с соот» ветствующими разрядными выходами ре

SO гистра зоны, выходы элементов ИЛИсое-, динены с группой информационных выходов устройства, группа адресных входов устройства соединена со входами дешифратора и является первой грушюй адресных выходов устройства, в второй группой адресных выходов устройства являются выходи регистра номера массива, первая и вторая группы выходов

643878

Составитель Ф. Шагнахметов

Редактор Д. Мепуришвнли Техред 3, фанта Корректор Л. Гриценко

Заказ 8023/45 - Тираж 779 Подписное

ЦНИИПИ Государственного кЬмнтета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектна», 4 шифратора соединены с ри ряднымн входами соответственно регистра номера массива и регистра зоны.

Источники информации, принятые во внимание при экспертизе;

1. Авторское свидетельство СССР

> 431516, кл. 0 06 F 9/20, 1972.

2. Авторское свидетельство СССР

S. М 453739, кл. О 11 С 17/00, 1972.