Устройство для сложения и вычитания частот двух импульсных последовательностей

Иллюстрации

Показать всеРеферат

< 643901

Сема Совет(вии

Сациалистнчасвии

Рвснублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 21.06.76 (21) 2375682/18-24 (51) М. Кл.

G06 G 7/14 с присоединением заявки №

Государственный комитет

СССР

-по делам изобретении и открытий (23) Приоритет

Опубликовано 2501»79.Бюллетень № 3 (5З) УДК 681.325.4 (088.8)

Дата опубликования описания 250179 (72) Авторы изобретения 3.H. Домбровский и A.A. столяров

I .,/ е»

СР Я;),11 a q

Р .1

-тр. -„щ -. -, : (71) Заявитель ц i гг <)

»««:«, «-» «««„, *ЗФ». (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ

ЧАСТОТ ДВУХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к области автоматики и вычислительной техникь и может быть использовано в измерительной технике.

Известно устройство для вычитания и сложения двух последовательностей, импульсов (1) . Недостатком этого устройства является представлейие выходного сигнала (суммарного нли разностного) в виде неравномерной после- 1" довательности коротких импульсов, . Наиболее близким по технической сущности к данному йзобретенню являет: ся устройство (21, содержащее блок синхронизации, элемент И, блок управления, сумм тор rio ìîÄóëé два," дели»-"" тель частоты, выход которого являетея выходом устройства, первая и вторая информационные шины устройства соединены соответственно с первым и вторым входами блока синхронизации, управляющая шина соединена с первым входоМ блока управления.

Недостатком известного УстРойства является низкая частота выходного сигнала.

Целью изобретения является расширение частотного диапазона устройства.

С этой целью в него введен умножитель частоты, вход котороГо соединен

cî второй информационной шиной, а первый и второй выходы — соответст.— венно со вторым входом блока управления, а также с третьим входом блока управления и первым входом сумматора по модулю два, второй вход которого соединен с выходом элемента

И, первый вход которого соединен с выходом блока синхронизации, а второй вход — с выходом блока управления, выход сумматора по модулю два соединен со входом делителя частоты.

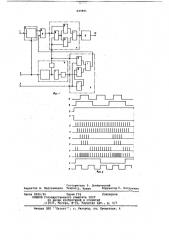

На фиг, 1 представлена схема устройства, на фиг. 2 — временная диаграмма работы устройства.

Устройство содержит (фиг.1) информационные шины 1, 2, управляющую

IdHHy 3, умножитель 4 частоты, блок 5 синхронизации, блок 6 управления, сумматор 7 по модулю два, делитель 8 частоты, элемент, И 9, выход 10.

Устройство работает следующйм образом.

На вход 1 подают более высокую (фиг. 2 а), а на вход 2 более низкую (фиг. 2 б) входные частоты, представленные в виде последовательностей прямоугольных импульсов со скважностью g 2.

643901

Ale. 1 Составитель 3..Домбровский

Редактор Д. Цепурцшвилр Техред Э, цу к к. Корректор С. Патрушева

Закав Pg)6/ 6 Type 779 Родлисрое

ДЩЩЦД осударствеииоро ксмитета СССР йо делам изобретеии q оу срыФиЦ

j))f35< Э дсква $-3 Раущскаи наб., д; $/5

Ф дцщ ЯДА Цще т, г, У рород у ; ПРорщщя,