Цифровой дифференциальный анализатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) дополнительное к авт. свид-ву(И) Заявлено 081074 (21) 2065293/18-24

Саюз Советских

4:фциалистических республик

<и) 643915 (51) М. Кл.

606 У 1/02 с присоединением заявки М

Государственный «омитет

СССР по деяам изобретений и открытий (23) ОриоритетОпубликовано 2501.79.Бюллетень Jk 3 ..

Дата опубликования описания 250179 () ИЖ 681 14 (088 8) (72) Автор изобретения

И,М.Соколов (7!) Заявитель (54) ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИ3АТОР

Изобретение относится к области вычислительной техники. Оно может быть использовано в качестве функционального преобразователя и формирова- . теля различных функциональных эави- 8 симостей, например, для управления фазированной антенной решеткой РЛС, для управления разверткой индикатора

РЛС и для других целей.

Известны цифровые дифференциаль- 10 ные анализаторы (ЦДА) j1), содержащие . переменные линии задержки, блок памяти, элементы И.

Недостатком известных устройств является значительная конструктивная l5 сложность.

Из известных устройств наиболее . близким по технической сущности является цифровой дифференциальный анализатор (2j, содержащий датчик исходных данных, вход которого является входом устройства, формирователь адреса, состоящий иэ адресных. счетчиков старших и младших разрядов, соединенных соответственно с дешифра-. + торами старших и младших раэрядбв, коммутатор, блок памяти, группа вйходов которого соединена с группой входов коммутатора, блок управления, сумматор, первая группа входов кото2 рого соединена с первой группой выходов коммутатора, вход которого сое» динен с первым выходом блока управления, регистр результата, первый вход которого соединен со вторым выходом блока управления.

К недостаткам известного устройства следует отнести то-,что в нем невозможно обеспечить ойеративный ввод любого значения функции в произвольный момент времени, что удлиняет время решения задачи.

Цель изобретения - повышение быстродействия цифрового,дифференциального анализатора.

Поставленная цель достигается тем что в устройство введены и регистров адреса приращений, дешифратор приращений, блок элементов И, буферный регистр и схема сравнения, причем ri0yвая группа выходов датчика исходных данных соединена с группой входов адресного счетчика старших разрядов, а вторая группа"выходов - с первой группой входоя схемы сравнения, выход которой подключен к .первому входу блока управления, третий выход блока управления соединен со. входом адресного счетчика старших разрядов и сО вторым входом адресного счетчика

643915 младших разрядов, четвертый выходсо вторым входом адресного счетчика

"Младших разрядов, пятый выход - ко входу дешифратора старших разрядов, шестой выход - ко входу блока буферного регистра, второй вход блока управления является информационным вхо- 8 дом устройства, седьмой и восьмой вход блока управления являются управляющими входами устройства, первый и второй выходы дешифратора адреса старшйх разрядов соответственно с )0 ,первым и вторым входами блока памяти, группа входов которого соединена с группой выходов дешифратора приращений, первый и второй выходы дешифратора адреса младших разрядов соедине- 15 ны с соответствующими входами и регистров адреса приращений, выходы которых пс;ключены ко входам дешифратора приращений, вторая группа выходов коммутатора .соединена с группой вхо-. дов первого и второго регистров адреса приращений и с группой входов буферного регистра, группа выходов которого соединена со второй группой вхо" дов сумматора, группа выходов суммато ра подключена к группе входов регистра результата, группа выходов которого подключЕна к группе входов буферного регистра и через блок элементов И к инфорМационному выходу устройства.

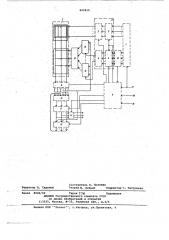

На чертеже представлена блок-схема® устройства.

Цифровой дифференцйальный анализатор содержит датчик 1 исходных данных, формирователь 2 адреса, который содержит адресный счетчик 3 старших раэря- 35 дов, адресный счетчик 4 младших разрядов, дешифратор 5 старших разрядов, дешифратор с младших разрядов, блок 7 памяти, коммутатор 8, блок 9 управления, сумматор 10, регистр 11 резуль- 40 тата, регистры 12« 12> адреса приращений, дешифратор 13 приращений, блок

14 элементов И, буферный регистр 15, схема 16 сравнения, информационный вход 17, управляющие входы 18,19. 45 .Устройство работает следующим образом., При подаче внешнего импульса останов по входу 19 регистры ll, 15, адресные счетчики 3,4 устанавливаются

s нулевое положение, а генератор блоКа 9 управления блокируется.

При подаче внешнего импульса --запуск по входу 18 подключается генератор блока 9 управления, обеспечивающий формирование на выходе его ймпульсов для управления последовательностью работы ПДА. Сначала под ключается выход дешифратора 5 и иэ зоны старших разрядов блока 7 информация (нулевая) поступает через ком- @ мутатор 8 на старшие разряды буферного регистра 15 а иэ зоны адреса при-. ращений информация обо всех адресах .цлй. данного положения адресного счетчика 3 через коммутатор 8 поступает 65 на входы N регистров 12 д и записыва- ется в них. Так как адресный счетчик

4 находится в нулевом состоянии, то на дешифратор 13 поступает адресная информация, соответствующая 0, Затем блок 9 управления обеспечивает подключение выходоЬ дешифратора 13.

При этом иэ блока 7 через коммутатор

8 поступает нулевое приращение на первые входы сумматора 10 а на вто- рые входы его поступает информация иэ буферного регистра 15 (нуле= вая ), Затем информация иэ суммато« ра 10 переписывается в регистр 11 результата (блок 14 может отключаться только.при вводе исходных данных).

Далее приходит импульс на счетный вход адресного счетчика 4, переводя его в первое положение. При этом блок 9 управления обеспечивает отключение выходов дешифратора 5 и подключение выходов коммутатора 8 к первым входам сумматора 10 до возникновения импульса на счетном входе адресного счетчика 3. В адресный счетчик 4 записана 1, что обеспечивает подключение выходов первого регистра адреса приращений 12 ко входам дешифратора 13. Затем блок 9 управления обеспеЧивает подключение вЫходсв дешифратора 13 и перезапись из регистра 11 в буферный регистр 15. При этом из блока 7 через коммутатор 8 поступает приращение функции на первые входы сумматора 10, а.на вторые входы его поступает предыдущая информация с выхода буферного регистра 15..Затем новое значение функции переписывается в регистр 11 и формируется новый импульс на счетном входе адр .сного счетчика 4, переводя его во второе состояние, что обеспечивает посредством дешифратора 6 подключение выходов второго. регистра адреса приращений 12 ко входу дешифратора 13. Затем блок 9 управления обеспечивает подключение выходов дешифратора 13 и перезапись иэ регистра 11 в буферный регистр 15.

При этом иэ блока 7 через коммутатор

8 поступает приращение функции на первые входы сумматора 10, а на вторые входы его поступает предыдущая информация с выхода буферного регистра 15. Затем новое значение функции переписывается в регистр ll и формируется новый импульс на счетном входе адресного счетчика 4, переводя егоs третье состояние и т.д. до тех пор, пока, не возникнет импульс на счетном входе адресного счетчика 3. При этом регистры 12 и адресный счетчик 4 обнуляются. Затем подключается выход дешифратора 5 и из эоны старших разрядов блока 7 информация поступает через коммутатор 8 на старшие разряды буферного регистра 15, а из зоны адреса приращений 7 информация обо всех адресах для данного положения адресного счетчика 3 через коммутатор 8

5 643 поступает на входы всех регистров 12 и записывается в них.Так как адресный счетчик 4 находится в состоянии О, то на дешифратор 13 поступает адресная информация, соответствующая О .

Затем блок 9 управления обеспечнвает подключение выходов дешифратора 13 и переключение коммутатора 8 в другое состояние. При этом из блока 7 через коммутатор 8 поступает нулевое приращение на первы входы сумматора 10, а на вторые входы его поступает предыдущая информация из буферного регист- 10 ра 15.Затем информация иэ сумматора

10 переписывается в регистр 11.Далее на счетный вход адресного счетчика 4 поступает импульс, переводя его в сос"тояние, соответствующее 1 и т.д. до заполнения счетчиков, после чего цикл работы повторяется.

Использование в цифровом дифференциальном анализаторе новых блоков и связей между ними по сравнению с про- 20 тотипом позволило повысить быстродействие процесса ввода. исходных данных в 1350 раэ при одновременном уменьшении объема памяти в 4. раза.

Кроме того, в регистры адреса приращений могут. быть записаны любые адреса в произвольном порядке, что поз- воляет использовать ЦДА для формирования любых функций.

Формула изобретения

Цифровой дифференциальный анализатор, содержащий датчик исходных дан- 35 ных, вход которого является входом устройства, формирователь адреса, состоящий иэ адресных счетчиков старших и младщих разрядов, соединенных соответственно с дешифраторами стар- 40 ших и младших разрядов, коммутатор, . блок памяти, группа выходов которого соединена с группой входов коммутатора, блок управления, сумматор, первая группа входов которого соединена с первой группой выходов коммутатора, вход которого соединен с первым выхо- 45 дом блока управления, регистр результата, первый вход которого соединен со вторым выходом блока управления, 915 6 б т л и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены и регистров адреса приРащений, дешифратор приращений, блок элементов И, буферный регистр и схема сравнения, причем первая группа выходов датчйка исходных данных соединена с группой входов адресного счетчика старших разрядов, а вторая группа выходов - c первой группой входов схемы сравнения, выход которой подключен к первому входу блока управления, третий выход блока управления соединен со входом адресного счетчика старших разрядов и со вторым входом адресного счетчика младших разрядов, четвертый выход - со вторым входом адресного счетчика младших разрядов, пятый выход — ко входу дешифратора старших разрядов, шестой выход — ко входу буферного регистра, второй вход блока управления является информационным входом устройства, седьмой и восьмой вход блока упраьления являются управляющими входами устройства, первый и второй выходы дешифратора адреса старших разрядов соединены соответственно с первым и вторым входами блока памяти, группа входов которого соединена с группой выходов дешифратора приращений, первый и второй выходы дешифратора ад- реса младших разрядов соединены с соответствующими входами Й регистров адреса приращений, выходы которых подключены ко входам дешифратора приращений, вторая группа выходов коммутатора соединена с группой входов первого и второго регистров адреса приращений и с группой входов буферного регистра, группа выходов которого соединена со второй группой входов сумматора, группа выходов сумматора подключена к группе входов регистра результата, группа выходов которого подключена к группе входов буферного регистра и через блок элементов И к информационному выходу устройства °

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 213416, кл. 6 06 У 1/02, 1966.

2. Авторское свидетельство СССР

9 294157, кл. G 06 7 1/02, 1969.

643915

Составитель H. Полеева

Техред Ю. Ниймет Корректор С. Патрушева

Редактор A. Садомов

Филиал ППП Патент, г.ужгород, ул.Проектная, 4

Закав 8026/4б Тираж 779 Подписное цНИИПИ Государственного комитета СССР по делам изобретений и открытой

1l3035, Москва, Ж-35, Раушская наб., д.4/5