Регистр сдвига

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И ЗО6РЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ и643976

Союз Советских

Социалистимеских

Республик

2 (51) М. Кл. (61) Дополнительное к авт. свид-ву (22) Заявлено 18. 10.76 (21) 2412290/18-24

11 С 19/00 с присоединением заявки № (23) Приоритет

Государственный комитет

СССР оо делам изобретений н открытий

Опубликовано 25.01.79.Âþëëåòåíü № 3 (53) УДК 628.327. .6 (088.8) Дата опубликования описания 28.01.79

С. П. Попков и Л. Н. Гришан (72) Авторы изобретения (71) Заявитель (54) РЕГИСТР СДВИГА

Изобретение относится к вычислительной технике и может быть использовано в радио-технических устройствах приемо-передачи дискретных данных.

Известен регистр сдвига, содержащий потенциальные логические элементы и RSтриггер, единичный и нулевой входы триггера соединены соответственно с единиЧным и нулевым выходом последнего разряда первой группы разрядов регистра, единичный и нулевой выходы RS-триггера соединены соответственно с единичным и нулевым входом первого разряда второй группы разрядов регистра, тактовый вход RS-триггера соединен с выходом второго каскада генератора тактовых импульсов (1). 15

Наиболее близким техническим решением к данному изобретению является регистр сдвига, содержащий два RS-триггера и два инвертора, шины записи, управления, считывания и сброса (2).

Скорость, с которой сдвиговые импульсы продвигают данные с входа регистра на выход, выбирается такой, чтобы значительно превосходить скорости «вспышки» самой высокой скорости, которые могут возникнуть во время ввода данных.

В этом регистре скорость поступления данных значительно ограничена, быстродействие при переносе их с входа на выход невысоко. При асинхронном поступлении данных на вход регистра возможность одновременно пройзводить их запись и считывание с регистра отсутствует, а наличие источников сдвиговых импульсов требует дополнительного оборудования.

Целью изобретения является повышение быстродействия регистра и обеспечение возможности одновременной записи и считывания данных.

Поставленная цель достигается тем, что вход первого инвертора каждого разряда регистра соединен с прямым выходом первого RS-триггера данного разряда, инверсный выход которого соединен с R-входом второго RS-триггера предыдущего разряда, с входом второго инвертора и S-входом второго RS-триггера данного разряда, прямой выход которого соединен с S-входом первого RS-триггера, а выход первого инвертора данного разряда соединен с R-входом RS-триг643976

35 ключена на вьдход инвертора 12, шина 18,подключена на выход инвертора 14, шина 19 подключена на выход инвертора 15, шина 20 подключена на R-вход RS-триггера 1, шина 21 подключена на инверсный выход RSтриггера 2, шина 22 подключена на инверсный выход RS-триггера 8, шина 23 подключена на R-вход RS-триггера 8, шина 24на счетный вход RS-триггера 8, D-вход триггера 8 подключен к шине нулевого потенциала.

В исходном состоянии RS-триггеры 2, 4, 6, сброшены. На шине 20 присутствует нулевой уровень, Нулевые уровни присутствуют на входах S и Rтриггеров 1,,3, 5, 7 и на обоих выходах этих триггеров присутствуют единичные уровни. На шинах 16 — 19 присутствуют нулевые уровни, т. к. на входы инверторов 10, 12, 14, 15 поступают единичные уровни. На шинах 21, 22, 23 присутствуют единичные уровни и на шине 24 нулевой уровень.

Сигнал записи единичного уровня поступает на шину 20 и RS-триггера 1 устанавливается в единичное состояние. Нулевым уров нем инверсного плеча RS-триггера 1 установится в единичное состояние RS-триггер 2

45 гера последующего разряда, шина записи подключена к R-входу первого RS-триггера первого разряда, шины управления — к выходам вторых инверторов, шина заполнения регистра — к инверсному выходу второго RSтриггера первого разряда, шина наличия данных в регистре — к инверсному выходу второго RS-триггера последнего разряда, к одному из входов которого подключена шина считывания, а к другому — шина сброса.

При таком построении регистра сдвиговые импульсы формируются элементами регистра, а перенос осуществляется асинхронно со скоростью, определяемой быстродействием элементной базы регистра, скорость поступления данных может приближаться к ско- 15 рости переноса в регистре. Запись данных и считывание их в регистре независимы, что позволяет производить одновременно операции записи и считывания.

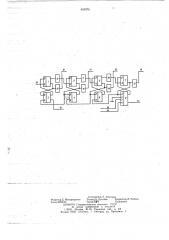

Работа предлагаемого регистра рассматривается на примере 4-разрядного регистра сдвига, схема которого приведена на чертеже.

Схема содержит RS-триггеры 1 — 8, инверторы 9 — 15, шины 16 — 19 управления, шину 20 записи в регистр, шину 21 заполнения регистра, шину 22 наличия данных в регистре, шину 23 обнуления регистра, шину 24 считывания данных.

RS-триггеры 1, 2 и инверторы 9, 10 образуют 1-й разряд (входной) регистра;

RS-триггеры 3, 4 и инверторы 11, 12 образуют 2-й разряд регистра; RS-триггеры 5, 6 и инверторы 13, 14 — 3-й разряд; RS-триггеры 7, 8 и инвертор 15 образуют 4-й (выходной) разряд регистра. Шина 16 подключена на выход инвертора 10, шина 17 поди на управляющей шине установится единйчный уровень. С прямого выхода RS-триггера 2 единичный уровень поступит на вход триггера 1. По окончании сигнала запись RS-триггер 1 сбросится. На шине 16 установится нулевой уровень, а на выходе инвертора 9 установится единичный уровень, который поступает на R-вход RS-триггера 3. RS-триггер 3 установится в единичное состояние. С инверсного выхода RSтриггера 3 нулевым уровнем сбросится RSтриггер 2 и установится в единичное состояние RS-триггер 4. С прямого выхода RSтриггера 2 на S-вход триггера 1 поступит нулевой уровень и на прямом выходе триггера 1 установится единичный уровень, который поступит на вход инвертора 9. На выходе инвертора 9 установится нулевой уровень, который поступит на R-вход триггера 3 и сбросит его. Таким образом, на входе инвертора 12 будет присутствовать нулевой уровень, который поступает с инверсного плеча RS-триггера 3 в течение времени, длительность которого равна задержке íà RS-триггерах 1, 2, 3 и инвертора 9.

В течение этого времени на управляющей шине 17 будет присутствовать сигнал с единичным уровнем. После сброса RS-триггера 3 на выходе инвертора 11 установится единичный уровень, который поступает на Rвход RS-триггера 5: RS-триггер 5 установится в единичное состояние. С инверсного выхода RS-триггера 5 установится в единичное состояние RS-триггер 6 и сбросится RS-триггер 4. С прямого выхода RSтриггера 4 на вход RS-триггера 3 поступит нулевой уровень. На прямом выходе RS-триггера 3 установится единичный уровень, который поступит на вход инвертора 11. С выхода инвертора 11 íà R-вход RS-триггера 5 поступит нулевой уровень и сбросит его. На время задержки сигнала на RS-триггерах 3, 4, 5 и инверторе 11 на входе инвертора 14 будет присутствовать нулевой уровень. В течение этого времени на управляющей шине 18 будет присутствовать сигнал единичного уровня. После сброса RS-триггера 5 на выходе инвертора 13 установится единичный уровень, который поступит на Rвход RS-триггера 7. RS-триггер 7 установится в единичное состояние. С инверсноговыхода RS-триггера 7 нулевым уровнем установится в единичное состояние RS-триггер 8 и сбросится RS-триггер 6. С прямого выхода RS-триггера 6 íà S-вход RS-триггера 5 поступит нулевой уровень. На прямом выходе RS-триггера 5 установится единичный уровень, который поступает на вход инвертора 18. Нулевой уровень с выхода инвертора 13 поступит на R-вход RS-триггера 7 и сбросит его.

На время задержки Hà RS-триггерах 5, 6, 7 и инвертора 13 на входе инвертора 15 присутствует нулевой уровень. В течение этого времени на управляющей шине 19

643976 будет присутствовать сигнал единичного уровня.

RS-триггер 8 останется в единичном состоянии и на шине 22 установится нулевой уровень. При поступлении второго сигнала записи, цикл сдвига повторится; но так как на S-входе RS-триггера 7 присутствует единичный уровень, сдвиг остановится на ячейке, образованной RS-триггерами 5, 6 и инверторами 13, 14, и RS-триггер 6 установится в единичное состояние, а управляющие сигналы сформируются поочередно на шинах 16, 17, 18. При поступлении третьего сигнала записи установится в единичное состояние триггер 4, а управляющие сигналы сформируются на шинах 16, 17. При поступлении четвертого сигнала записи установится в единичное состояние триггер 2, а управляющий сигнал сформируется на шине 16.

На шине 21 установится нулевой уровень— сигнал заполнения регистра.

При заполненном регистре вновь поступ а ю щие да ни ы е будут тер яться.

Для поразрядного считывания с регистга на шину 24 поступает сигнал единичного уровня, триггер 8 сбрасывается. На Sвход RS-триггера 7 поступит нулевой уровень и RS-триггер 7 устанавливается в единичное состояние. С инверсного выхода RSтриггера 7 нулевым уровнем RS-триггер 8 установится в единичное состояние и сбросится триггер 6. На S-вход триггера 5 поступит нулевой уровень и он установится в единичное состояние и соответственно на выходе инвертора 13 установится нулевой уровень, который поступит на R-вход триггера 7. RS òðèããåð 7 сбросится, так как на еГо S-входе присутствует единичный уровень, поступающий с RS-триггера 8. На время задержки на RS-триггерах 5, 6, 7 и инверторе 13 на шине 19 будет присутствовать управляющий сигнал и произойдет сдвиг с третьей ячейки в выходную и на шине 22 установится нулевой уровень. С RSтриггера 5 нулевым уровнем с инверторного выхода RS-триггер 6 установится в единичное состояние, RS-триггер 4 сбросится.

Аналогично на шине 18 сформируется управляющий сигнал, а затем управляющий сигнал сформируется на шине 17 и сбросится RS-триггер 2. На шине 21 установится единичный уровень. При каждом поступлении сигнала единичного уровня на шину 24 происходит сдвиг в регистре вправо, при

Формула изобретения

2о Регистр сдвига, содержащий в каждом разряде два RS-триггера и два инвертора, шины записи, управления, считывания и сброса, отличающийся тем, что, с целью повышения быстродействия регистра и обеспечения возможности одновременной записи и считывания, в нем вход первого инвертора каждого разряда регистра соединен с прямым выходом первого RS-триггера данного разряда, инверсный выход которого соединен с R-входом второго RS-триггера предызо дущего разряда, с вхбдом второго инвертора и S-входом второго RS-триггераданного разряда, прямой выход которого соединен с S-входом первого RS-триггера, а выход первого инвертора данного разряда соединен с R-входом RS-триггера последующе го разряда, шина записи подключена к Rвходу первого RS-триггера первого разряда, шины управления — к выходам вторых инверторов, шина заполнения регистра к инверсному выходу второго RS-триггера

4о первого разряда, шина наличия данных в регистре —, к инверсному выходу второго

RS-триггера последнего разряда, к одному из входов которого подключена шина считывания, а к другому — шина сброса.

Источники информации, принятые во вни45 мание прп экспертизе

l. Авторское свидетельство СССР № 432602, кл. G 11 С 19/00, 19.09.72.

2. Авторское свидетельство СССР

¹ 503296, кл. G 11 С 19/12, 22.03.77. поступлении каждого четвертого единично-го сигнала регистр обнуляется и на шине 22 устанавливается единичный уровень.

Для обнуления всего регистра используется шина 23.

Использование предлагаемого регистра сдвига позволяет получить следующие преимущества перед использованием известных: а) увеличить скорости приема данных; б) увеличить скорости переноса в регистре; в) уменьшить количество и номенклатуру используемого оборудования; г) производить одновременную запись

15 и считывание данных с различным быстродействием.

643976, Составитель Л. Амусьева

Редактор Д. Мепуришвили Техред 0.,1 уговая Корректор Jf. Небола

Заказ 8034/49 Тираж Ьфб Подписное

UHHHllH Государственного комитета СССР по делам изобретений и открытий

1l3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал П ПП «Патент», г. Ужгород, ул. Проектная, 4