Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

п1) 645268

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт, свид-ву (22) Заявлено 28.09,77 (21) 2530338/18-24 с присоединением заявки № (51) М. Кл.з

6 11С 29/00 (43) Опубликовано 30.01.79. Бюллетень № 4 (45) Дата опубликования описания 30.01.79 (53) УДК 681.327.6 (088.8)

I ло делам изобретений и открытий (72) Авторы изобретения

К. Г. Волков, А. В. Городний, В. И. Корнейчук, С. И. Аль-Укейли и В, В. 1цведов

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (71) Заявитель (54) ЗАПОМИНА1О1ЦЕЕ УСТРОЙСТВО С

САМОКОНТРОЛЕМ

ГесУдарстввнный комитет (23) Приоритет

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства с самоконтролем.

Одно из известных устройств содержит накопитель, регистр адреса, регистр слова, блоки кодирования и декодирования (1).

Это устройство характеризуется сложностью реализации блоков кодирования и декодирования.

Из известных устройств наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к регистру адреса н регистру слова; соединенного с блоком контроля и блоком кодирования, и блок управления (2).

Однако в этом запоминающем устройстве требуются большие аппаратурные затраты на реализацию блока кодирования, а также большое число дополнительных разрядов в накопителе для записи контрольных разрядов корректирующего кода.

Целью изобретения является упрощение конструкции и повышение информационной емкости устройства. Поставленная цель достигается тем, что устройство содержит регистр отказов и элементы И, входы которых подключены к выходам регистра слова и блока управления, а выходы — к выходам устройства, входы регистра отказов соединены с выходами блока управления, а выходы — со входами регистра слова.

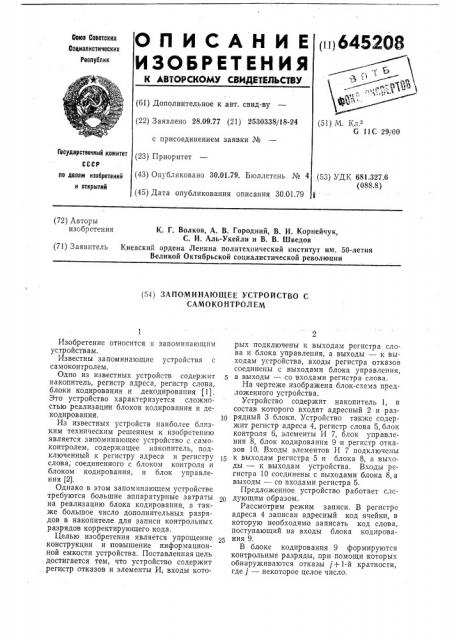

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит накопитель 1, в состав которого входят адресный 2 и раз1р рядный 3 блоки. Устройство также содержит регистр адреса 4, регистр слова 5, блок контроля 6, элементы И 7, блок управления 8, блок кодирования 9 и регистр отказов 10. Входы элементов И 7 подключены

15 к выходам регистра 5 и блока 8, а выходы — к выходам устройства. Входы регистра 10 соединены с выходами блока 8, а выходы — со входами регистра 5.

Предложенное устройство работает следующим образом.

Рассмотрим режим записи. В регистре адреса 4 записан адресный код ячейки, в которую необходимо записать код слова, поступающий на входы блока кодирования 9.

В блоке кодирования 9 формируются контрольные разряды, при помощи которых обнаруживаются отказы j+1-й кратности, где 1 — некоторое целое число.

Информационные и контрольные разряды слова с выходов блока кодирования 9 постуйают в регистр слова 5.

В блок управления 8 поступает код операции «Запись». По сигналу «Выдача кода» с выхода блока управления 8 код слова из регистра слова 5 поступает на входы разрядного блока 3 накопителя 1, где записывается по адресу, определяемому кодом, записанным в регистре адреса 4.

Рассмотрим теперь режим считывания.

В регистре адреса 4 записан адресный код ячейки, информацию из которой необходимо считывать. По сигналу «Выдача кода» с выхода блока управления 8 код адреса поступает на входы адресного блока 2 и с выходов разрядного блока 3 накопителя 1 считанный код поступает на входы регистра слова 5, где записывается по сигналу «Прием кода» с блока 8.

Считанный код поступает на входы блока контроля 6, который обнаруживает отказы кратности, 1, 2, 3, j+1. При этом для каждой кратности отказа блок контроля 6 имеет отдельный выход.

В случае когда нет отказов, т. е. на всех выходах блока контроля 6 имеются сигналы, равные логическим нулям, то блок управления 8 формирует сигнал, по которому элементы И 7 открываются, и код считанного слова поступает на выходы устройства.

В случае, когда в коде слова есть отказ -й кратности, где 1(i(j, то на выходах блока контроля 6, соответствующих однократному, двухкратному, ..., i-кратному отказам, появятся cnrnaлы, равные логической «единице».

При наличии единичного сигнала хотя бы на одном из выходов блока контроля 6 блок управления 8 формирует сигнал записи «единицы», например, в младшем разряде регистра 10.

По сигналу блока управления 8 в регистре 10 записывается «единица» в младшем разряде, после этого следует операция суммирования по модулю «два» кодов в регистре слова 5 и в регистре 10. Для выпо.пнения этой операции с выхода блока управления 8 поступает сигнал «Выдача кода» в регистр 10, код этого регистра, содержащий «единицу» в младшем разряде, поступает на счетные входы регистра слова 5.

При этом изменяется значение считанного младшего разряда считанного слова.

В случае, если имеет место отказ в младшем разряде, то выход i-й кратности отказа блока контроля 6 изменит свое значение, т. е. значение его будет равным логическому «нулю». Следовательно, отказ в считанном слове после первого суммирова. ния по модулю «два» будет (i — 1)-й кратности.

5 В этом случае, т. е. если кратность отказа уменьшилась на «единицу» (и соответственно число «единиц» на выходах блока контроля 6 стало на «единицу» меньше), по сигналу «Сдвиг» с выхода блока

10 управления 8 сдвигается на один разряд информация в регистре 10 и снова выполняется операция суммирования по модулю

«два».

В случае, когда после суммирования по

15 модулю «два» кратность отказа в коде считанного слова увеличивается, то число «единиц» на выходах блока контроля 6 увеличивается на «единицу».

Для восстановления исходного состояния значения этого разряда необходимо снова просуммировать по модулю «два» коды регистров 5 и 10, после чего выполняется операция «Сдвиг».

Операции суммирования по модулю

«два» и «Сдвиг» выполняются до тех пор, пока из блока контроля 6 не поступает в блок управления 8 нулевой код, что говорит об устранении всех отказов.

При наличии нулевого кода на выходах блока контроля 6 выдается команда «Установка в нуль» на одном из выходов блока управления 8.

В предложенном устройстве упрощается реализация блока кодирования, и при этом требуется меньшее число контрольных разрядов корректирующего кода.

Фор мул а из о бр етен и я

Запоминающее устройство с самоконтро40 лем, содержащее накопитель, подключенный к регистру адреса и регистру слова, соединенного с блоком контроля и блоком кодирования, и блок управления, от л и ч аю щ е е с я тем, что, с целью упрощения и

45 повышения информационной емкости устройства, оно содержит регистр отказов и элементы И, входы которых подключены к выходам регистра слова и блока управления, а выходы — к выходам устройства,вхо50 ды регистра отказов соединены с выходами блока управления, а выходы — со входами регистра слова.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 407399, кл. G 11С 29/00, 1972.

2. Городний А. В., Корнейчук В. И. Проблема высоконадежной памяти — «Автоматика и телемеханика», 1974, № 7, с. 155, 645208

Составитель В. Рудаков

Корректор 3. Тарасова

Техред С, Антипенко

Редактор В. Левитов

Типография, пр. Сапунова, 2

Заказ 2632/13 Изд. № 139 Тираж б80 Подписное

НПО Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Я-35, Раушская наб., д. 4/5