Инвертор на транзисторно-транзисторных логических элементах

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (i ц 6452 80

Гл13 Сооетскнт

Содналистическик

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.04.74 (21) 2015216(18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.01.79. Бюллетень № 4 (45) Дата опубликования описания 30.01.79 (51) М. Кла

Н ОЗК 19(00

Государстеенный комитет (53) УДК 621.373 (088.8) ло делам изобретений и открытий (72) Авторы изобретения

Д. К. Сургуладзе и В. М. Махарадзе (71) Заявитель (54) ИНВЕРТОР НА ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫХ

ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

Изобретение относится к импульсной технике и может использоваться в устройствах автоматики и вычислительной техники.

Известны инверторы на транзисторнотранзисторных логических элементах.

Один из известных инверторов содержит усилитель, эмиттерный повторитель и ключ.

Недостаток этого инвертора заключается в низкой надежности (1).

Наиболее близким техническим решением к изобретению является инвертор на транзисторно-транзисторных логических элементах, содержащий парафазный усилитель, эмиттерный повторитель и ключ, подключенные к выходам парафазного усилителя (2).

Однако этот инвертор имеет недостаточно высокое быстродействие.

Цель изобретения — повышение быстродействия инвертор а.

Для этого в инвертор на транзисторнотранизсгорных логических элементах, содержащий парафазный усилитель, эмиттерный повторитель и ключ, подключенные к выходам парафазного усилителя, введен диод, анод которого подключен к выходу инвер тор а, а катод — к коллектору тр анзистора парафазного усилителя.

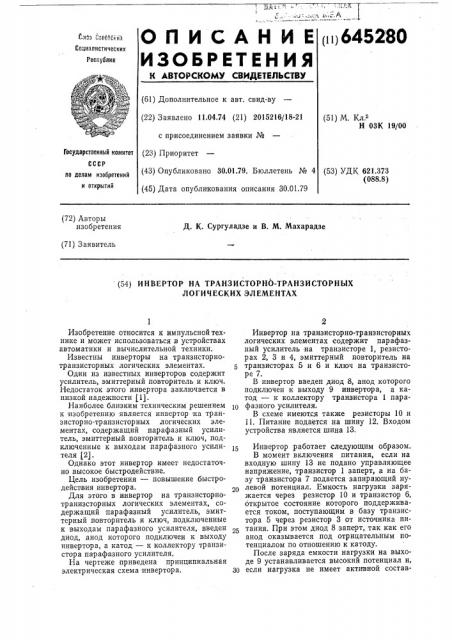

На чертеже приведена принципиальная электрическая схема инвертора.

Инвертор на транзисторно-транзисторных логических элементах содержит парафазный усилитель на транзисторе 1, резисторах 2, 3 и 4, эмиттерный повторитель на транзисторах 5 и 6 и ключ на транзисторе 7.

В инвертор введен диод 8, анод которого подключен к выходу 9 инвертора, а катод — к коллектору транзистора 1 парафазного усилителя.

В схеме имеются также резисторы 10 и

11. Питание подается на шину 12. Входом устройства является шина 13.

15 Инвертор работает следующим образом.

В момент включения питания, если на входную шину 13 не подано управляющее напряжение, транзистор 1 заперт, а на базу транзистора 7 подается запирающий нулевой потенциал, Емкость нагрузки заряжается через резистор 10 и транзистор 6, открытое состояние которого поддерживается током, поступающим в базу транзистора 5 через резистор 3 от источника питания. При этом диод 8 заперт, так как его анод оказывается под отрицательным потенциалом по отношению к катоду.

После заряда емкости нагрузки на выходе 9 устанавливается высокий потенциал и, 30 если нагрузка не имеет активной состав3 ляющей, схема практически не потребляет мощности.

При поступлении на входную шину 13 положительного импульса транзистор 1 отпирается, и потенциал его коллектора начинает уменьшаться. Наступает момент, когда переходы эмиттер — база транзисторов 5 и 6 смещаются в обратном направлении, а диод 8 отпирается.

Наличие дополнительной низкоомной цепи питания через открытый диод 8 за счет разрядного тока емкости нагрузки позволяет значительно увеличить начальный эмиттерный ток транзистора 1, который после отпитания транзистора 7 практически полностью поступает в его базу. Это приводит к значительному ускорению разряда емкости нагрузки и способствует повьгшению быстродействия схемы. По мере разряда емкости нагрузки доля дополнительного тока через диод 8 в коллекторном токе транзистора 1,постепенно уменьшается, и транзистор 1 переходит в режим насыщения, После этого момента базовый ток транзистора 7 определяется величиной резистора 3 и практически остается постоянным в течение действия управляющего напряжения на входной шине 13. Емкость нагрузки продолжает разряжаться почти постоянным

645280 коллекторным током транзистора 7, который к концу разряда переходит в режим насыщения.

При отключении входного управляющего напряжения транзистор 1 запирается, благодаря наличию низкоомного резистора 4 транзистор 7 быстро переходит в режим отсечки базового тока, и процесс заряда емкости нагрузки происходит так же, как

10 и при включении схемы.

Формула изобретения

Инвертор на транзисторно-транзистор16 ных логических элементах, содержащий парафазный усилитель, эмиттерный повторитель и ключ, подключенные к выходам парафазного усилителя, отл ич а ю щи йся тем, что, с целью повышения быстро20 действия,.в нето введен диод, анод которо го подключен к выходу инвертора, а катод — к коллектору транзистора парафазного усилителя.

Источники информации, 25 гринятые во внимание при экспертизе

1. Шагурин И. И. Транзисторно-транзисторные логические схемы. М., «Сов. Радио», 1974, с. 89, рис. 31.

2. Патент США ¹ 3562560, кл. 307 †3, 30 опублик. 09.02.71.