Двоичный преобразлватель кодчастота

Иллюстрации

Показать всеРеферат

452 84

ОПИС

ИЗОБРЕ

Союз Советова

Социалистических

Республик к авто скомю св (61) Дополнительное к авт. (22) Заявлено 10.12.76 (21) с присоединением заяв (23) Приоритет (43) Опубликовано 30.01.79 (45) Дата опубликования о

Кл.а

Н 03К 23!24

Государственный комитет

Совета Министров СССР

К 621.373 (088.8) по делам изобретений и открытий (72) Автор изобретения

Б. А. Фурман

Харьковский ордена Ленина политехнический институт им. В. И. Ленина (71) Заявитель (54) ДВО И Ч Н Ь1 Й П РЕОБ РАЗО ВАТЕЛ Ь КОД вЂ” ЧАСТОТА

Изобретение относится к информационно-преобразовательной и вычислительной технике.

Известно устройство, осуществляющее преобразование кода в частоту, содержащее триггерный двоичный делитель частоты, емкостные элементы укорочения импульсов, двухвходовые элементы И, один из входов которых в каждом разряде связан с выходом элемента укорочения, а второй служит входом управления, и элемент

ИЛИ: 11.

Недостатками этого устройства являются нестабильность параметров выходных импульсов, связанная с разбросом и нестабильностью применяемых емкостей, а также невозможность выполнения схемы полностью на интегральных элементах, Известен также управляемый делитель частоты, содержащий триггерный двоичный делитель, каждый разряд которого соединен через управляемые кодом вентили с элементом И,(21.

Недостаток этого устройства состоит в низкой точности преобразования выходных импульсов.

Цель изобретения — повышение точности преобразования.

Поставленная цель достигается тем, что в двоичный преобразователь код †час2 тота, содержащий триггерный двоичный делитель частоты и элемент ИЛИ, в каждый разряд преобразователя введен дополнительны и D — Т-триггер, причем счетньвй вход каждого из этих D — Ттриггеров соединен с единичным выходом триггера двоичного делителя частоты, инверсные входы установки нуля дополнительных D — Т-три|ггеров — с входом двоичного делителя частоты, управляющие

D-входы соединены с шинами управляющего кода, а единичные выходы подключены к входам элемента ИЛИ.

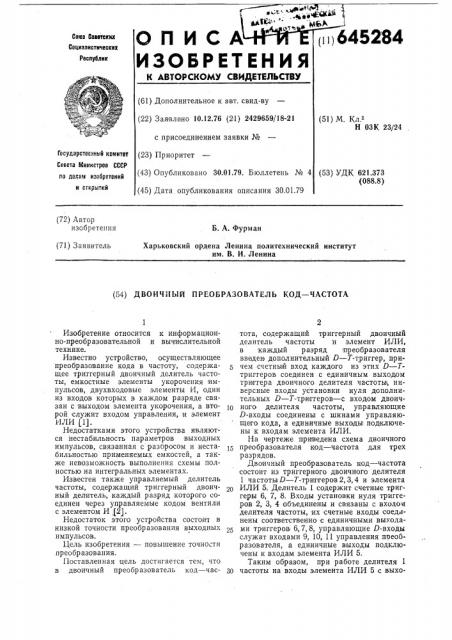

На чертеже приведена схема двоичного преобразователя код — частота для трех разрядов.

Двоичный преобразователь код — частота состоит из триггерного двоичного делителя

1 частоты17 — Т-триггеров 2,3,4 и элемента

ИЛИ 5. Делитель 1 содержит счетные триггеры 6, 7, 8. Входы установки нуля триггеров 2, 3, 4 объединены и связаны с входом делителя частоты, их счетные входы соединены соответственно с единичными выходами триггеров 6, 7, 8, управляющие D-входы служат входами 9, 10, 11 управления преобразователя, а единичные выходы подклю. чены к входам элемента ИЛИ 5.

Таким образом, при работе делителя 1 частоты на входы элемента ИЛИ 5 с выхо645284

10 л

fm,z = fez+2 — в, Составитель М. Леонова

Текред Н. Строганова

Корректор О. Тгорииа

Редактор И. Грузова

Заказ 2642/18

Тираж 1059

Изд. № 156

Подписное

Типография, пр. Сапунова, 2 дов триггеров 2, 3, 4 поступают серии импульсов фиксированной длительности, равной длительности импульсов входной частоты, с частотой двоичных субгармоник, где к — номер разряда делителя 1.

2к

Среднее значение частоты, синтезируемой на выходе элемента ИЛИ 5, определяется как где n †чис разрядов делителя 1, а наличие или отсутствие тех или иных субгармоник в указанной сумме зависит от наличия или отсутствия сигналов «единицы» на D-входах триггеров 2, 3, 4.

Работа синтезатора происходит следующим образом.

Каждый импульс входной частоты f„за исключением импульсов, вызывающих переполнение делителя 1 частоты (при трехразрядном делителе каждый восьмой импульс), приводит к формированию сигнала на единичном выходе одного из триггеров (6, 7, 8), а следовательно, и на счетном входе соответствующего из триггеров 2, 3, 4, что вызывает переход последнего в единичное состояние. Так как одновременно с входом делителя 1 частоты импульсы входной частоты поступают и на инверсные входы установки нуля триггеров 2, 3, 4, то при указанном срабатывании одного из них его возврат в исходное (нулевое) состояние происходит на заднем фронте импульса входной частоты. При этом сама возможность записи единицы в триггерах 2, 3, 4, 5 определяется наличием на ихб-входахуправляющего кода на соответствующем из входов (9, 10, 11) управления преобразователя.

Формула изобретения

Двоичный преобразователь код — частота, содержащий триггерный двоичный делитель частоты и элемент ИЛИ, отлича15 ю шийся тем, что, с целью повышения точности преобразования, в каждый разряд преобразователя введен дополнительный

D — Т-триггер, причем счетный вход каждого из этих0 — Т-триггеров соединен с единичным выходом триггера двоичного делителя частоты, инверсные входы установки нуля дополнительных D — Т-триггеров соединены с входом двоичного делителя частоты, управляюшие D-входы соединены с шинами управляющего кода, а единичные выходы подключены к входам элемента

ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. «Archiv fur Electrotechnik», 1964, В,49 н. 4, S 218.

2. Авторское свидетельство СССР № 456366, кл. Н 03 К 21/36, 1972.