Устройство для контроля микроэлектронных логических схем

Иллюстрации

Показать всеРеферат

ааьа., О П И С А Я "Е

ИЗОБРЕТЕН ИЯ

Союз Советсимк

Соцмалмстмческмх

Республик »646280 (61) Дополнительное к авт. свил-ву М. 273342 г (51) М. Кл

G 01 И 31/28

Н 03 К 17/00 (22) Заявлено14.04.77 (21) 2474411/18-21 с присоединением заявки №йсударственкьа ксиктет

СССР в делам нзобрвтенкк н вткрыткк (23) Приоритет (53) УДК 621.326. .74(088.8) опубликовано 05 .02.79.Бюллетень № 5

Дата опубликования описаний 08.02 79

Б. А. Ящук и Н. Н. Поддубный (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОЭЛЕКТРОННЫХ

ЛОГИЧЕСКИХ СХЕМ

Изобретение относится к контрольноизмерительной технике, в частности к технике программируемых тес новых испытаний микроэлектронных логических схем, может быть использовано для регулировки, контроля правильности функционирования и контроля электрических параметров микроэлектронных логических схем вычислительной техники.

Известно устройство для контроля микроэлектронных логических схем, содержащее блок управления, входной, выходной и запоминающий регистры, прот раммируемый блок питания, амплитудный селектор, цифровой блок сравнения, формирователь входных сигналов, блок запуска, блок индикации, цифропечатающий блок, блок ввода и вывода, временной селектор, управляемый элемент задержки (1)

Недостатком этого устройства являеч ся возможность выхода его из строя или повреждения проверяемой микроэлектронной логической схемы в случае, если к

2 выходам формирователей входных сигналов устройства подключаются выходы проверяемой схемы.

С целью повышения надежности, в и:.ьвестное устройство для контроля микроэлектронных логических схем по авт. св. % 273342 введен блок контроля; коммутаторов входов, причем его информационные входы соответственно соеди нены с выходами блока формирователей входных сигналов управляющий вход соединен с одним из выходов блока управления,первый выход - с одним из управ» ляющих входов блока формирователей входных сигналов, а его второй выход15 с одним из входов цифропечатающего блока.

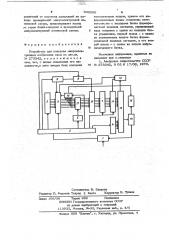

На чертеже приведена структурная электрическая схема предлагаемого устройства.

2О

Устройство содержит блок ввода 1, блок управления 2, входной регистр. 3, выходной регистр 4, программируемый блок питания 5, блок формирователей

646280 входных сигналов 6, амплитудный селектор 7, управляемый элемент задерж ки 8, блок запуска 9, временной селектор 10, запоминающий регистр 11, цифровой блок сравнения 12, блок индикации

13, выводной блок 14, цифропечатаюший блок 15, блок контроля коммутаторов входов 16,.

Работает устройство следующим образом. После включения напряжения питания сигнал из блока управления 2 зайрещает появление сигналов на выходах блока формирователей входных сигналов

6, а блок контроля коммутаторов входов 16 по сигналу из блока управления

2 определяет, являются ли подключен ные Ф выходам блока формирователей входных сигналов 6 выводы МЛС ее вхо-дами.

Отличить вход ми;кроэлектронной логи- 20 .ческой схемы 17 от выхода можно йо ве- личине напряженйя- на выводе, тока, отдаваемого в нагрузку, входному сопротивлению и т. п., Пусть, напрймер, проверяемая микро электронная логическая схема 17 состо - ит из ийтегральных микросхем. В функцйю блока контроля коммутаторов вхоцов 16 входит измерение напряжения на" выводах схемы 17. Если это напряжение хотя бы на одном выводе превышает напряжение на входах интегральйых микро l схем или. меньше, чем это напряжение, это значит, что ко входу блока форми75 рователей входных сигналов 6 ошибочно подключен не вход схемы 17, и поэтому блок контроля коммутаторов входов 16 запрещает формирование сигналов "на вы- ходах блока формирователей входных сиг- налов 6, а на блоке индикации 13 ин40. дицируются номера выводов микроэлектронных логических схем, напряженйе на которых не соотвеФсч вует- входному напряжению интегральных микросхем.

Если напряженйе на выводах схемы

17 соответатвует напряжению," нормальному для взводов схемы 17 блок контроля коммутаторов входов 16 разрешает поступление сигналов с выходов блока

50 формирователей входных сигналов 6 на входы йроверяемой" схемы 17.

Таким образом, блок контроля -коммутаторов входов 16 предотвращает короткое замыкание выходов блока формиро55 вателей входных сигналов 6 на выходы проверяемой схемы 17.

Далее в устройство вводится тестовая программа проверки данной схемы 17, 1

Зта программа с помощью блока ввода 1 и блока управления 2 записывает во входной 3 и выходной 4 регистры информацию, которую необходимо подать на входы схемы 17 и которая должна быть на выходах исправной МЛС.

Эта же программа устанавливает на программируемом блоке питания 5 тре- буемое напряжение питания схемы 17; на амплитудном селекторе 7 - допустимые уровни логического ".0" и "1" выходных сигналов, на управляемом элементе задержки 8 - пределы временной селекции выходных сигналов.

На блоке формирователей входных сигналов 6 - уровни логического "0" и ."l" сигналов, подаваемых на входы

МЛС 17.

После этого из блока управления 2 в блок запуска 9 поступает сигнап, разрешающйй считывание информации со входного регистра 3 в блок формирователей входных сигналов 6. С блока запуска 9 на управляемый элемент задержки 8 поступает сигнап начала отсчета времени, совпадающйй по времени с из- .

I менением сигналов на выходах блока формирователей . входных сигналов 6, ко- торый с элемента задержки 8 в качестве запрещающего сигнала поступает на все входы многоканального временного селектора 10.

Сигналы на выходах проверяемой схемы 17 появляются с некоторой задержкой, зависящей от схемы 17. Через временной селектор 10 в амплитудный селектор 7 проходят только те сигналы со схемы 17, которые появляются раньше . прихода запрещающего сигнала с элемента: задержки 8 на временной селектор 10.

Сигйалы, прошедшие через временной селектор, подвергаются амплитудному контролю в амплйтудном селекторе 7.

Сигналы, удовлетворяющие требованиям по амплитуде и времени, записываются в запоминающий регистр 11.

Информация,зайисанная в запоминающем регистре ii, вводится в цифровой: блок сравнения 12, где сравнивается с требуемой реакцией для задайного теста. Результаты сравнения выводятся на блок индикации 13 и на выводной блок

14 и далее — на цифропечатающий блок

15.

Таким образом, введеный в схему блок контроля коммутаторов входов обеспечивает защиту выходов блока форми646280

Составитель В. Евпаков

Редактор Б. Федотов Техред 3. Фанта Корректор Н Ъпица

Заказ 106/36 Тираж 696 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 рователей от коротких замыканий на выходы проверяемой: микроэлектронной логической схемы, предотвращает выход из строя блокаконтроля и проверяемой микроэлектронной логической схемы.

Формула изобретения.Устройство для контроля микроэлектронных логйческих схем по авт.св.

Мю 273342, от л,и ч а ю щ е е с я тем, что, с целью повышения его надежности,в него введен блок контроли коммутаторов входов, причем его ин» формационные входы соединены соот ветствелно с выходами блока формирователей входных сигHaJloB p8BJ_#_3MItKO вход соединен с одним из выходов блока управления, первый выход - с одним из управляющих входов блока форми рователей входных сигналов, а его втсьрой выход - с одним из входов цифропечатаюшего блока.

Источники информации, принятые во внимание при э;.спертизе

1. Авторское свидетельство СССР

15 No 273342, Н 03 К 17/ОО, 1970.