Система для обмена данными управляющей вычислительной машины с периферийным устройством

Иллюстрации

Показать всеРеферат

Э.

Ф Г: .. ц-! э;;,, д

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К Ав?ОЛЕСКОМУ СВИДВ?ИЛЬС?ВУ

<» 646326

Союз Соаетскин

Социалистииескин

Республик (6|) Дополнительное к авт, свил-ву,¹ 490115 (22) Заявлено 25 10 76 (21) 2414618/18-24

2 (51) М. Кл.

Ci 06 F 3/04 с присоединением заявки № (23) ПриоритетГосударственньй нщатет

СССР пе денек нэаеретеннй н открытнй

Опубликовано 05.02.79.рюллетень № 5 (53) УДК 681.326 (088.8) Дата опубликования описания 08.02.79 (72) Автор изобретения

Ю. В. Ерипов (71) Заявитель (54) СИСТЕМА ДЛЯ ОБМЕНА ДАННЫМИ

УПРАВЛЯЮЩЕЙ ВЪ|ЧИСЛИТЕЛЪНОЙ МАШИНЫ

С ПЕРИФЕРИЙНЫМ УСТРОЙСТВОМ

Изобретение относится к вычиспитепьной технике и явпяется усовершенствов нием известной системы, описанной в авт. св. %4901)5.

Ь основном авт. св. Ив 490115 опи-! сана система, содержащая регистр обмена, периферийный регистр, коммутатор, блок управления, блок выбора приоритета, блок управления периферийным устройством и центральный процессор.

Указанная система не обеспечивает обмен информации между периферийным устройством и управпяющей вычислительной машиной в дуппексном режиме, что снижает пропускную способность системы.

Цепь изобретения состоит в повышении пропускной способности системы.

Поставленная цель достигается тем, что в систему по авт. св. N 490115 введены адресный регистр, бпок управления адресным регистром, дешифратор, формироватепь признака обращения, формирователь сигнапа перекпю-ения и выходной коммутатор, причем управпяюший вход коммутатора соединен с управляю-H BMH входами форм ировате пя признака обрашения, формироватепя сигнапа переключения и блока управпения адресным регистром, выход которого подключен к первому входу адресного регистра второй вход коммутатора соединен с первыми входами формирователя признака обрап.ения и формирователя сигнала перекпю чения, выход которого подключен к третьему входу коммутатора, выход формироватеня признака обращения соединен со входом бпока управпения адресным регистром и вторым входом адресного регистра, третий вход которого подкпкл чен к третьему выходу бпока управпения, выходы адресного регистра подключены к адресному входу выходного коммутатора и через дешифратор к третьему входу формироватепя признака обращения, информационные входы и выходы периферийного регистра подключены соответственно к информационным выходам и входам

646326 выходного коммутатора, BxoAbr и выходы которого подсоединены к соответствующим входам и выходам системы.

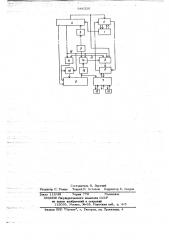

На чертеже представлена блок-схема системы, которая содержит: центра пый процессор 1, регистр обмена 2, блок 3 выбора приоритета, блок 4 управления, блок 5 управления периферийным устройством, коммутатор 6, выходной коммутатор 7, периферийный регистр 8, адресный регистр 9, блок 10 управления адресным регистром, формирователь

ll признака обращения, дешифратор 12, входы и выходы системы 13,, подключаемые к периферийному устройству, форми-. рователь 14 сигнала переключения, ши на 15 синхронизации, сигнал на которую подается со второго выхода блока

4 управления, и шина 16 синхронизации, на которую сигнал подается из блока 5 управления периферийным устройством.

11ентральный процессор 1 соединен с регистром обмена 2 шинами,ио которым производится обмен информацией в параллельном коде между процессором 1 и регистром обмена 2.i Управление регистром обмена 2 осуществляет блок

4 управления, Источники данных периферийного устройства соединены со входами-выходами

13, которые через выходной коммутатор

7 связаны с периферийным регистром 8.

Сигналы с выхода дешифратора 12 через формирователь 14 сигнала переключения подаются на управляющие вхды коммутатора 6, обеспечивающего в зависимости от режима работы подачу на управляющий вход периферийного регистра 8 сигналов синхронизации либо с соответствующего выхода блока 4 управления (шина 15 синхронизаци), либо с выхода блока 5 управления периферийным устройством (шина 16 синхронизации) .

Управление адресным регистроМ 9 осуществляется сигналами, поступающими на соответствующие входы из блока 10 управления адресным регистром и из формирователя 11 признака обращения.

В исходном положении сигнал на шине 15 синхронизации из блока 4 управления в периферийное устройство не выдается. При наличии сигнала на шине 16 синхронизации, генерируемого блоком 5 управленим периферийным устройством, формирователь 11 призкака обращения вырабатывает сигнал, М

ЗО

Ф

96

Я обеспечивающий по соотве Tcтвующему входу установку адресного регистра 9 в исходное состояние, которое преобразуется дешифратором 1 2 в сигнал, которым формирователь 14 сигнала переключения переводит коммутатор 6 в состояние, обеспечивающее прохождение сигналов синхронизации с гыхода блока 5 управления периферийным устройством на управляющий вход периферийного регистра 8. Кроме того, состояние разрядов адресного регистра 9 дешифруется в выходном коммутаторе 7, и тем самым обеспечивается разрьгг цепей обмена источников данных, подключенных ко входам-выходам 13, и периферийного регистра S.

Обмен данными управляющей вычислительной машины с периферийным устройством может производиться как по инициативе цснтрального,роцессора 1, который формирует в этом случае сигнал, поступающий в блок 4 управления, так и по инициативе периферийного устройства, которое формирует сигнал, поступающий из его блока 5 управления периферийным устройством через блок

3 выбора приоритета на соответствующий вход блока 4 управления.

Блок 4 управления, получив команду на обмен данными центрального процессора 1 с периферийным устройством, выдает на шину 15 синхронизации послеповательность импульсов. С приходом первого импульса последовательности формирователь 11 признака обращения в течение времени действия последовательности импульсов синхронизации на шине

15 вырабатывает потенциальный сигнал, которым адресный регистр 9 переводится в режим записи информации. Одно-. временно, блок 10 управления адресным регистром по сигналу с выхода формирователя 11 признака обращения начинает вырабатывать из последовательности импульсов синхронизации первую пачку сдвиговых импульсов, которые поступают на вход синхронизации адресного регистра 9, обеспечивая запись кода . операции (организация передачи информации в одном или обоих направлениях) и адреса входа-выхоиа 13, поступающего из блока 4 управпеиия.

Tlo обличении заииси информации в

alt, есный регистр 9, состоявшие разрядов етого регистра дешифруется в выходном коммутаторе 7, обеспечивая подключение соответствующего входа-выхода 13 к

64 (j:Д2 6 периферийному регистру Р. Кроме того, дешифратор .12 дешифрует H BblpQt,ëòüþëåò сигнал, который через формирователь 14 сигнала переключения выдается на управ ляющие входы коммутатора 6, обеспечивая формирование второй пачки сдвиговых импупь ов из последовательности импульсов синхронизации на шине 1 5 и подачу этой пачки сдвиговых импульсов на вход синхронизации периферийного регист- 16 ра 8. Одновременно блок 4 управления вьграбатывает третью пачку сдвиговых импульсов, которые прикпадьгваются к входу синхронизации регистра обмена 2.

Информация с выхода регистра обмена 2 под действием третьей пачки сдвиговых импульсов поступает HQ вход периферийного регистра 8 и записывается в него.

Лнапогич ым образом информация

20 из периферийного регистра 8 переписывается в регистр обмена 2.

По окончаний сеанса обмена информацией блок 4 управления прекращает выдачу сигнала на шину 15 синхронизации. Формирователь 11 признака обращения при напичли сигнала на его входе по шине синхронизации 16 формирует сигнал, которым адресный регистр

9 и блок 10 управления адресным регистром переводятся в исходное состояние. В выходном коммутаторе 7 разрываются соединения входов-выходов 13

-и периферийного регистра 8. На выходе

7 дешифратора 12 заканчивается формирование сигнала, обеспечивающего через формирователь 14 сигнала переключения и коммутатор 6 подачу на управляющийвход периферийного регистра 8 сигнала синхронизации с шины 15. Центральный

40 процессор 1 осуществляет считывание информации с регистра обмена 2 и начинает подготавливать информацию дня следующего сеанса обмена информацией.

В периферийном устройстве информация

45 с периферийного регистра 8 переписывается в соответствующий источник данных, подключеииьФ ко вкоду-выходу 13.

После этого периферийньй регистр 8 может быть использован в составе пери56 ферийного устройства дпя решения других задач, для чего через коммутатор 6 из блока 5 управления периферийным устройством HB вход синхронизации регистра 8 подается сигнал синхронизации с шины 16.

Таким образом, введение в систему по авт. св. No490115 ряда дополнитеи ных блоков позволило повысить пропускную способность системы обмена управляющей вычислительной машины с периферийным устройством за счет одновременной работы нескольких источников

pBHHbfx в составе периферийного устройства.

Формула изобретения

Система для обмена данными управляющей вычислительной машины с периферийным устройством по авт. св.

Н. 490115, отличающаяся тем, что, с целью повышения пропускной способности системы, в нее введены адресный регистр, блок управ;.ения адресным регистром, дешифратор, формирователь признака обращения, фор» мироватепь сигнала переключения и выходной коммутатор, причем управляющий вход коммутатора соединен с управляющими входами формирователя признака обращения, формирователя сигнала переключения и блока управления адресным регистром, выход. которого подключен к первому входу адресного регистра, второй вход коммутатора соединен с первыми входами формирователя признака обращепия н формирователя сигнала переключения, выход которого подключен к третьему входу коммута-îðà,,выход формирователя признака обращения соединен со входом блока управления адресным регистром и вторым ВхороМ ад» ресного регистра, третий ахоп которого подключен к третьему выходу блока управления, выходы адресного регистра подключены к адресному входу выходного коммутатора s через дешифратор к третьему mopy формирователя признака обращения, информационные входы и выходы периферийного регистра подключены соответственно и информационным выходам и входам выходного коммутатора, входы и выходы которого подсоединены к соответствуккцим входам и выходам системы.

646326

Составитель В. Вертлиб

Редактор С. Равна Техред И. Асталош Корректор Н. Петрик

Заказ 113/39 Тираж 779 Подписное

ЦПИИПИ ГЪсударотвенного комитета СССР по делам изобретений и открыччЯ

113035, Москва, Ж-35, Раушскан наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4