Устройство управления вычислительной машины

Иллюстрации

Показать всеРеферат

у;

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ ii®646332

Союз Советскм

Социалм ставских

Республик

К АВТОРСКОМУ СВИДИТЮЛЬСТВУ (6l) Дополнительное к авт. саид-ну (22) Заявлено02.06.7S (21) 2139607/18-24

2 (51) М. Кл.

6 06 F 9/06 с присоединением заявки № (23) Приоритет

Гееудератеенньа кеметет

СССР ее делам нзебретенкй н открытей

Опубликовано 05.02.7а Бюллетень № 8 (53) УДК 681,8 (088.8) Дата опубликования описания 08.02,79

E. А. Горбачев, А, А. Заблоцкий, В. А, Никольцев и В. Г, Сеньков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО УПРАВЛЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ

МАШИНЫ

Изобретение относится к области вычислительной техники и может найти применение при проектировании высоконадежных устройств управления вычислительной машины с жесткой программой. 5

Известно устройство управпения вычисиительной машины, состоящее из бпока коммутации и синхронизации, вырабатываюшего серию управлявших сигнапов блока управления командами, содержащего регистр. команд, счетчика комайд и дополнительных регистров, узла управпения операциями, содержащего дешифратор кода операций (бпок операций) и вентипьные схемы, образующие бпоки центрального и местного управления операциями 1 .

Недостатком этого устройства явпяется низкая помехозащищенность, 20

При работе вычиспитепьной машины в условиях значитепьных помех возможны ситуации, при которых происходит выработка лишних управпяюших сигнааов, что приводит к неверному решению выпопняемой задачи, в свою очередь приводит к неправильной работе объекте регулирования или к выходу последнего из строя.

Из известных устройств управпения наиболее бпизким по технической сущности явпяется устройство управпения, содержащее дешифратор кода операций (,блок ввода-вывода, счетчик команд и распредепитеяь импульсов, причем первый и второй выходы дешифратора кода операций соединены соответственно с первым входом распредепитеия импупьсов и счетчика команд, а третий выход дешифратора кода операций соединен со входом блока ввода-вывода, первый и второй выходы распредепитепя импульсов соединены соответственно с первым входом блока дешифратора кода операций и со вторым входом счетчика команд, выход счетчика команд сое646332!

20

30 аднен со вторым входом дешифратора кода операций f2).

Такое устройство управления обладает низкой помехозащищенностью, так как его работа зависит от воздеиствия импульсных помех в каналах тактовой и цикповой частот, подаваемых на входы распределителя импульсов.

При этом тактовая частота определяет темп выполнения операций вычислительной машиной, а цикйоввя — темп выполнения программы.

Каждым импульсом цикловой частоты происходит запуск вычислительной машины с начального адреса, записанного в определенную ячейку оперативной памяти. Обновление этой ячейки происк ° ходит перед концом работы программы, т. е. программа,записав в ячейку начальный адрес следующей программы, останавливает вычиспитепьную машину.

Запуск вычислительной машины производится импульсом цякловой частоты.

При этом, если импульс цикловой частоты придет до того.как машина остановилась, то это приведет к сбою.всего вычислительного процесса.

Белью предлагаемого изобретения ,является повышение помехоэащищенности работы устройства. Поставленная цель .достигается тем, что в устройство введены репе времени и логический блок, причем вход устройства соединен со входом реле времени, выход которого соединен со вторым входом распределителя импульсов, выход логического бло кв соединен соответственно с третьим входом распределителя импульсов и счетчика команд, выход блока ввода-вывода соединен с первым входом логического блока, второй и третий входы которого

1 соединены соответственно со вторым

1 входом устройства и с четвертым выходом дешифратора кода операций. Логи- ческий блок содержит триггер, пер вый и второй элементы И, первый и второй элементы задержки, причем первый вход логического блока соединен со входом первого, элемента задержки, выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с нулевым входом триггера, единичный выход которого соединен со входом второго элемента задержки, выход второго элемента задержки соединен с первым входом второго элемента И, второй вход которого сое35

4 пинен со вторым входом блока, выход второго элемента И соединен с единичным входом триггера и с выходом блока, третий вход блока соединен со вторым входом первого элемента И.

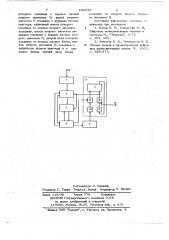

Сущность изобретения поясняется чертежом, где изображена структурная схема устройства управления вычиспитепьной машины.

Устройство содержит реле времени .1, распределитель импульсов 2, счетчик команд 3, дешифратор кода операций 4, блок ввода-вывода 5, логический блок .6, включающий в себя триггер 7, первый элемент И 8, первый элемент задержки 9, второй элемент задержки 10, второй элемент И 11.

Вход реле времени 1 соединен со входом 12 устройства, который подключен к каналу тактовой частоты вычислительной машины, выход реле времени

1 соединен со входом распределителя импульсов 2. Второй вход распределителя импульсов 2 соединен с выходом дешифратора кода операций 4, а третий вход распределителя импульсов 2 соединен со входом счетчика команд 3 и выходом логического блока 6.

Один выход распределителя импульсов 2 соединен со входом счетчика команд 3, а другой выход со входом дешифратора кода операций 4. Третий вход счетчика команд 3 соединен с первым выходом дешифратора кода операций 4, а выход счетчика команд 3 — со входом дешифратора кода операций 4.

Второй и третий выходы дешифратора кода операций 4 соединены соответст- венно со входом блока ввода-вывода 5 и с первым входом логического блока 6.

Выход блока ввода-вывода 5 соединен со вторым входом пбгического блока 6, 1

Третий вход логического блока 6 соединен со входом 13 устройства, который подключен к каналу цикловой частоты вычислительной машины.

Работа устройства после приведения в исходное состояние всех элементов вычислительной машины начинается с поступления на вход 13 устройства сигнала цикповой частоты, который разрешает начало выполнения программы.

Первый сигнал цикловой частоты проходит через первый элемент И 8 на единичный вход триггера 7 и устанавливает его в состояние 1, одновременно этот сигнал поступает на распределитель импульсов 2, разрешая

646332 тО

его работу, и на счетчик команд 3, I устанавливая в нем номер начальной команды программы. Сигнал с нулевого плеча триггера 7 через первый элемент задержки 9 закрывает первый элемент И 8 и запрещает дальнейшее поступление сигналов из начала тактовой частоты на распределитель импульсов 2 и счетчик команд 3. Первый элемент задержки 9 должен иметь время задержки не менее времени приведения в исходное состояние всех элементов и служит для задержки пропускания первого сигнала цикловой частоты на входы распределителя импульсов 2 и счетчика команд 3 через первый элемент И 8 на время переходных процессов, связанных с установкой в исходное состояние вычисттительной машины.

Сягнальr тактовой частоты поступают на вход 12 устройства и через реле времени 1 попадают на вход распределителя импульсов 2, работа которого разрешена первым сигналом цикловой частоты. Реле времени 1 пропускает на вход распределителя импульсов 1 сигналы, имеющие период следования не меньше допустимого для данной вычислительной машины, что дает возможность защититься от помех в канале тактовой частоты. Распределитель импульсов 2 обеспечивает синхроимпульсами счетчик команд 3 и дешифратор кода операций 4.

После выполнения программы дешифратор кода операций 4 вырабатывает сиги л окончания работы, который запрещает работу распределителя импульсов 1. Одновременно дешифратор кода операций 4 открывает второй элемент

И 1 1 и запускает блок ввода-вывода

5, который вырабатывает сигнал, псступаюший на вход логического блока 6.

Этот сигнал через второй элемент задержки 10 поступает на второй элемент И 11, проходит через него и устанавливает триггер 7 в положение О, после чего сигнал с нулевого плеча триггера 7 через первый элемент задержки

9 поступает на первый элемент И 8 и разрешает прохождение следующего сигнала из канала цикловой частоты.

Время задержки второго элемента задержки 10 должно быть не меньше времени окончания работы распределителя импульсов 2 и блока ввода-вывода 5 после выработки блоком операций.4 сигнала окончания выполнения црограммы.

Использование в устройстве реле времени и логического блока, содержащего триггер, первы% и второй элементы

И и первый и второй элементы задержки, позволяет защитить каналы тактОе1ой и цикловой частоты соответственно от воздействия помех в этих каналах, так как сигналы помех в канале тактовой частоты не приводят к нарушеттМю временной диаграммы взаимодействия устройств вычислительной машины, а помехи в канале цикловой частоты не приводят к перезапуску программы до окончания ее выполнения.

Формула изобретения

j.. Устройство управления вычислительной машины, содержащее дешифратор кода операций, блок ввода-вывода, счетчик команд и распределитель импульсов, причем первый и второй выхоттьт дешифратора кода операций соединены соответственно с первым входом распределителя импульсов и счетчика команд, а третий выход дешифратора кода операций сое динен со входом б пока ввода-выводя, первый и второй выходы распределите ля импульсов соединены соответственно с первым входом дешифратора кода операций и со вторым входом счетчика команд, выход счетчика команд соединен со вторы входом дешифратора кода операций, о т л и ч а юш е е с я тем, что, с целью повышения помехозащишенности в устройство введены реле времени и логический блок, причем первый вход устройства соединен со входом реле времени, выход которого соединен со вторым входом распределителя импульсов„выход логического блока соединен соответственно с третьим вхоцом распределителя импульсов и счетчика команд, выход блока ввода-вывода соединен с первым входом логического блока, второй и третий входы которого соединены соответственно со вторым входом устройся ва и с четвертым выходом дешифратора кода операций.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что логический блок содержит триггер, первый и втс рой элементы И, первый и второй элементы задержки, причем первый вход логического блока соединен со входом первого элемента задержки, выход

7 646332 8 которого соединен с первым входом соединен со вторым входом первопервого элемента И, выход первого го элемента И. эпемента И соединен с нулевым входом Источцики информации, цринятьи. « триггера, единичный выход. которого внимание при экспертизе соединен со входом второго элемента $ 1. Каган Б. hi., Каневский М, M. задержки, выход второго эпемента эа- Цифровые вычислительные машины и держки соединен с первым входом вто- системы, М., Энергия, 1Е7 3, рого элемента И, второй вход которого с. 363, 385. соединен со вторым входом блока, вы- 2. Анисмов Б. В., Четвериков В. H. ход второго элемента И соединен с 10 Основы теории и проектирования цифроединичным входом триггера и с вы- вых вычиспитепьных машин. М, 1962, ходом блока, тре л и вход блока с. 366-375.

Составитепь И. Сигапов

Редактор С. Равва ТехредС.Мигай Корректор H ПетРик

Заказ 113/39 Тираж 779 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фипиап ППП Патент, r. Ужгород, ул. Проектная, 4