Микропроцессор

Иллюстрации

Показать всеРеферат

(61) Дополнительное к авт. свид-ву (22) ЗаявлЕно 02.07.76 (21) 23805451 т 8-2,1 с присоединением заявки № (23) Приоритет г (51) М. Кл.

G 06 F 15/00

Госудерстеенней нометет

СССР. ео делан нзееретеннй н открытей рпубликовано05.02,79Бюллетень № 5 (53) УГИ681. 325

{088.8) Дата опубликования описания 08.02.7g (72) Авторы изобретении

A. И. Кривоносов, H. В. Кириченко, В. A. Калмыков и A. В. Сычев (71) Заявитель (54) МИКРОПРОЦЕССОР

Изобретение относится к области вычислительной техники и может быть использовано при создании больших интегральных схем, предназначенных для построения вычиспительнътх управляющих систем.

Известны микропроцессоры, содержащие управляющую и информационные магистрали, арифметико-логический блок, блок памяти чисел, программнопогическую матрицу, счетчик команд циклов), блок сдвига и управления Я

Недостатком известного микропр6цессора является большой объем оборудования

Наиболее близким по существу техническим решением задачи является микропроцессор, содержащий блок управления, первый вход которого соединен с первым входом микропроцессора, выход блока управления соедннен,с первыми входами первого, . второго и третьего мультиплексоров, второй вход первого мультиплексора, соедннен с первым вхо»дом микропроцессора и первым входом счетчика команд, первый выход которого непосредственно, а второй выход через третий мультиплексор соединены с первым и вторым выходами микропроцессо9 ра, вь ход первого мультиплексора через последовательно соединенные арифметикологический блок и второй мультиплексор соединен с третьим выходом микропроцессора и вторым входом .блока управления, т0 память, вьтходьт которой через первый дешифратор соединены с первым входом триггера условного перехода, а через стэковую память соединены с входами второго, третьего и четвертого дешифраторов, выход второго дешифратора соединен со вторым входом триггера условных переходов(2).

Недостатком известного микропроцессора является недостаточная надежность. © Белью изобретения является повытоение надежности., Поставленная цель достигается тем, что в микропроцессор введены реверсинный счетчик пятый дешифратор, четыре

64633

3 элемента И, причем выход реверсивного счетчика через пятый дешифратор соединен о первыми входами первого и второго элементов И, вторые .и третьи о входы которых соединены соответствен- S .но с выходами триггера условного перехода и третьего дешифратора, четвертый вход первого элемента И соединен с первым входом микропроцессора, четвертый вход второго элемента И соединен со,вторым входом микропроцессора, управляющим входом стэковой памяти и первым входом третьего элемента И, второй вход которого соединен с выходом четвертого дешифратора и первым входом четвертого элемента И, второй вход и выход которого соединены соответси венно с третьим входом микропроцессора и вторым входом счетчика команд, выход второго элемента И соединен с четвертым выходом микропроцессора и первым входом реверсивного счетчика, второй вход которого соединен с выходом третьего элемента И.

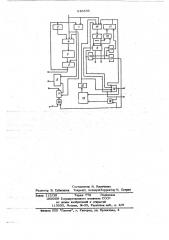

Блок-схема микропроцессора приведена на чертеже.

Микропроцессор содержит блок 1 управления, оперативную память 2, арифметико-погический блок 3, мупьтиппек30 соры 4-6, счетчик 7 команд, память 8, стаковую память 9, реверсивный счетчик

10, триггер 11 усповных переходов, дешифраторы 12-16, элементы И 1720.

Устройство работает следующим образом.

Управляющая и числовая информация через элемент И 17 поступает в

40 памя ь 8. Преобразованное в памяти 8 управляющее слово поступает в стэковую память 9 и записывается в первую его ячейку.

Il приходу второго тактового имо

4$ пульса первое управляющее слово переписывается во вторую ячейку, а второе слово записывается в первую ячейку н так далее.

Одновременно с записью информации

50 в память 9 производится суммирование в счетчике 10 единичного импульса, сформированного на выходе элемента И

18, который выдается также на выход микропроцессора и является стробом

$$ выдачи управпяюп.их cnoi иэ внешней программно-цогической матрицы ила внешнего постоянного запоминающего устройства.

go тех пор, пока в память 9 не будет внесено и спов (где p - чиспо ячеек в памяти 9), на выходе его присутствует нупевой код, который распознается в дешифраторе 15, на выходе которого присутствует нулевой потенциал, запрещающий вычитание единицы из. счетчика 10 и прибавпение единицы в счетчик 7.

Этот запрет осуществляется на элементах И 19, 20.

При записи tl спов в память 9 в счетчике 10 накопится t1 импульсов, при этом на выходе дешифратора 16 появится сигнал, который бпокирует выдачу сигнапа на выход микропроцессора и запрещает.прохождение информации через элемент И 17, Начиная с этого момента времени„ микропроцессор готов к выполнению программы, хранящейся в стэковой памяти 9. При выдаче каждого слова на выходы текущей микрооперации из сол держнмого счетчика 10 вычитается едй-. ница, запрещающий сигнал на выходе дешифратора 16 исчезает, что позвопяет принимать управляющие слова в память

9. При появлении на выходе стэковой памяти 9 управляющего слова характеризующего прием чисцовой информации, на выходе дешифратора 14 вырабатывается сигнал, запрещающий прием информации в память 9.

В этом случае эта информация поступает в память 2 или в счетчик 7, ипи в блок 1, или s блок 3, Коммутация информации межцу этими блоками осуществляется . мультиплексорами 4-,. 6.

При появлении на выходе памяти 8 управляющего слова, характеризующего условный или безусловный переходы ипи другие ветвлвння программы, на выхо— де дешифратора 12 вырабатывается сигнал, устанавливающий в единичное состояние триггер 11, нулевой выход которого бпокирует прием информации в память 8 и выдачу управпяющего сигнала на выход процессора.

При появлении этого управляющего слова на выходе стэковой памяти 9 на выходе дешифратора 13 вырабатывается сигнал, устанавливающий триггер

11 в нулевое состояние, после чего прием информации в стэковую память 9, модификация содержимого счетчика

10 и выдача управляющего сигнала на выход процессора разрешается, чем обеспечивается правильный выбор кодов программы при ветвлениях и усповных переходах. При напичии нупевого кода на выходе стэковой памяти 9 модификация содержимого счетчика 7 блокируется, что исключает ложное формироl ванне адреса текущей команды и выдачи переноса из счетчика 7 на выход процессора в хопостых циклах.

Таким образом, изобретение позвопяет совместить информационную и управпяюшие магистрапи практически без потери быстродействия, что приводит к исключению восьми наружных выводов

Ь микропроцессоре по сравнению с црототипом. Это позволяет ввести в состав микропроцессора значительно бопьшее число признаков внешних усповий и повысить его разрядность в два раза, что обеспечивает повышение надежности микропроцессора и снижение аппаратных затрат при построении вычиспитепьных систем.

Микропроцессор, содержаший блок управпения, первый вход которого соединен с первым входом микропроцессора, выход блока управления соединен с первыми входами первого, второго и третьего мупьтиппексоров, второй вход первого мупьтиппексора соединен с первым вхс дом микропроцессора и первым входом з: . счетчика команд, первый выход которого соединен непосредственно, а второй вйход через третий мупьтиппексор соединен ". первым и вторым выходами микропроцессора, выход первого мупьтиппексс ра через последовательно соединенные арифметико-логический бпок и второй мультиплексор соединен с третьим выходом микропроцессора и вторым входом блока управцения, память, выходы котоФормула изобретения

46ЗЗ6 6 рой через первый дешифратор соединены с первым входом триггера усповного перехода, а через стэковую память соединены с входами второго, третьего и четвертого дешифраторов, выход второго дешифратора соединен со вторым входом триггера условных переходов, отличающийся тем,что, с целью повышения надежности, в него

16 введены реверсивный счетчик, пятый дешифратор, четыре элемента И, причем выход реверсивного счетчика через пятый дешифратор соединен с первыми входами первого и второго эпементов И, М вторые и третьи входы которых соединены соответственно с выходами триг гера условного перехода и третьего дешифратора, четвертый вход первого эпемента И соединен с первым входом

М микропроцессора, четвертый вход второго эпемента И соединен со вторым входом микропроцессора, управляюшим входом стэковой памяти и первым входом третьего эпемента И, второй вход которого соединен с выходом четвертого дешифратора и первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с третьим входом микропроцессора и вторым входом счетчика команд, выход второго эпемента И соединен с четвертым выходом микропроцессора и первым входом реверсивного счетчика, второй вход которого соединен с выходом третьего . элемента И.

Источники информации, принятые во внимание. при экспертизе

1. Эпектроника", М 8, 1974, с. 46-51.

4 2. Разработка микропроцессоров и микропроцессорных систем, ч. 1. Обзоры по электронной технике, серия .3 Микроэлектроника, вып. 5, 1ЙИП.

Эпектроника, М., 1975, .с. 28-20.

Составитепь H. Кириенко

Редактор Э. Губнинкая ТехредИ. ЛсталошКорректор.H. Петрик

Заказ 113/39 Тираж 779 .. Поднисное ..

БНИИПИ Государственного комитета СССР но данам изобретений и открытий

113035, Москва, Ж«35, Раукскан наб., д. 4/8

Фнннан ППП " Патент, r. Ужгород, уа. Проектнан, 4