Многоканальный коррелятор

Иллюстрации

Показать всеРеферат

Сотоз Соеетскмк

Социалистических Ó6»<

634 1 (61) Дополнительное к авт. свил-ву (22) Заивлецо24.02.77 (21) 2458916/18-24 с присоединением заявки № 2 л, F 15/34

Геаударстваиньй оиттат

СССР аа делам язобрвтвай и ат рмтий (23) Приоритет

О нубл икова но 05,02.79 Бюллетеи ь ¹ 5

68 1. 323 (088. 8) Дата опубликования оиисания 08,02.7 (72) Авторы изобретения (71) Заявитель (54) МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР

Изобретение относится к вычислитель

1 ной технике и может быть использовано дпя вычисления взаимных и автокоррепяционных функций.

Известен цифровой коррелятор, характеризуюшийся частично коррепированной выборкой с одной стороны или невысоким быстродействием с другой стороны

И

Наиболее близким по технической сушности является многоканальный коррелятор,содержаший в каждом канале аналого-цифровой преобразователь, соединенный с выходным регистром, цифровую линию задержки, блок умножения, выход которого подключен к блоку усреднения, дополнительный аналого-цифровой преобразователь, соединенный с дополнительным выходным регистром, выход которого соединен с первыми входамиблоков

i умножения каждого канала, входы всех аналого-пнфровых преобразователей обьедн нены н являются входом коррелятора, ка налы не симметричны, так как онн соде жат неодинаковые линии задержки; у zo торых время задержки возрастает в каждом последукицем канале.

В корреляторе степень корреляции определяется из соотношения между числом каналов М, шагом задержки д

5 ь1 и периодом квантования ь и Г

Отсюда, если используется, например, восьмиканальный коррелятор, при вычислении принимают во внимание только

10 каждый восьмой отсчет, что приводит к потере точности f2).

Целью изобретения является повьпиеwe точности.

Поставленная цепь достигается тем, т5 что в коррелятор введен распределитель и в каждый канал - первый и второй регистры и коммутатор, причем в каж дом канале первый и второй входы коммутатора соединены соответствейно с

2О выходами первого и второго регистров, выход второго регистра подключен к первому входу первого регистра и ко входу р цифровой линии задержки, выход которой соединен с первым входом второго ре23

В. И. Григорьев, В. П. Кузьменко и Ф, Е. Лисник

646341

20 гистра, вторые входы первого и второго регистров подключены к выходу выходного регистра, выход коммутатора каждого канапа соединен с соответствуютпим входом распределителя, выходь, "которого соединены со вторыми входа;ти блоков умножения.

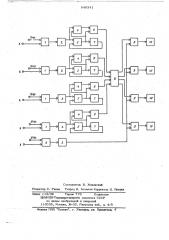

1-та чертеже изображена блок-схема описываемого коррепятора, Он содержит, аналого-цифровой преобразоватепь 1 с регистром 2, общий анапого-цифровой преобразователь 3, регистры 4,5, коммутатор 6 сомножителей, цифровая линия задержки 7„. распределитель 8 каналов, блок умножения 9, блок усреднения

10.

Коррелятор состоит из М канапов, каждый из которых содержит анапогоцифровой преобразователь (AUll) 1, выходной регистр 2, который своими выходами подключен к соответствующим входам регистров 4 и 5, Выходы регистров 4 подключены к одним входам коммутаторов 6 сомножителей, а выходы регистров 5 подключены ко входам цифровых пиний 7 задержки, выходы которых соединены со вторыми входами регистров 5, и вторым входом регистров

4, и коммутаторов С сомножителей, выходы которых подключены ко входам распределителя 8 каналов. Выходы рас пределителя 8 каналов подключены к одним входам соответствующих блоков умножения 9, вторые входы которых соединены с выходом выходного регистра 2, подкпюченного своим входом к

АЦП 3. Выходы блоков умножения 9 соединены со входами блоков усреднения 10.

Под воздействием управляющих импульсов, запускающих аналого-цифровые преобраэоватепи 1, последовательно в порядке возрастания номера канапа с частотой дискретизации исходных процес. сов эапопняются регистры 2. При срабатывании AUTI М-oro канала и заполнения соответствующего регистра 2 отсчеты по всем каналам поступают в. регистры 5, откуда,они переписывают ся в цифровую пинию 7 задержки и одновременно через коммутатор 6 и распредепитепь 8 каналов поступают на. одни входы блоков 9 соответствующих каналов. На вторые входы блоков умножения 9 поступает отсчет, произведенный в один момент времени с преобразователем М-ого канада и находящийся в соответствующем регистре 2 блока ум25

Я о

И

И ножения. Резупьтаты перемножения отсчетов поступают в блоки усредненйя

10. Б поспедуюшие моменты времени до прихода в регистр 2 первого канала следующего отсчета в регистр 5 с тактовой частотой работы цифровой пинии задержки 7 считываются ранее записанные в ней отсчеты и порядке, обратном поступпению, и через коммутатор 6 и распредепптепь 8 кацапов подаются на одни входы тех же блоков умножения.

На протяжении всего цикла вычислений (до прихода следующего отсчета в регистр 2 первого канаца) в регистре 2 общего аналого-цифрового преобразователя хранится отсчет, снятый в один момент времени с отсчетом, хранимым в регистре 2 М-ого канала, а распредепитепь 8 коммутирует сомножитепь первого канала на вход блока умножения первого канапа, сомножитепь второго канала на вход бпока умножения второго канапа и т. д. Таким образом, между сомножителями первого и общего канапов временной сдвиг равен (М -1) Ь С, (2 М - 1) л С, (ЗМ-1)

Ь -,между сомножителями второго и общего каналов — (М-2), (2N-2}, (ЗМ-2} ... и т. д.

С приходом следующего отсчета в регистр 2 первого канала и регистр 2 общего канала (они совпадают по времени) цикл вычислений производится аналогично во всех каналах,за исключением первого, В первом канапе считывание с линии задержки 7 и регистр 5 отсчета, записанного в пинию задержки 7 в предыдущем цикпе, совпадает по времени с перезаписью нового отсчета из регистра 2 и коммутации его коммутат ром 6 на вход распределителя 8 каналов. Таким образом, в первом канале .сдвиг во времени между сомножитепями (отсчетом первого канада и отсчетом, находящимся в,регистре 2 общего канала) равен 0;йТ, во втором — (М-1) Ь Г, в третьем— (N-2) и . и т. д. Распределитель 8 каналов коммутирует сомножите IH спедующим образом: с первого канала на бпок умножения.9 М-oro канала, со второго канала на блок умножения 9 первого канала, с третьего канала на бпок 9 второго канала и т. д. Таким образом,сомножитепи сдвигаются на один канал в сторону уменьшения номера канала. Считывание последующих отсчетов с цифровой пинии 7 первого канала

646341

iв регистр 5сопровождается перезаписью предыдущего отсчета в регистр 4 и коммутацией его на вход распределителя 8 каналов.

Такая последовательность работы сохраняется на протяжении всего цикла до 5 прихода спедующего отсчета в приемный регистр 2 второго кацапа.

По приходу следующего отсчета в приемный регистр 2 второго канала и регистр 3 общего цикл вычислений проис- б ходит аналогично ранее описанному во всех каналах за исключением первых двух, где последовательность вычислений соответствует описанному выше дпя . первого канала, а сомножителя распредепитепем 8 каналов сдвигаются на два канала в сторону уменьшения номера канала. Такая тенденция поспедоватепьности работы сохраняется до прихода следующего отсчета в приемный регистр

2 М-ого канала, с приходом которого весь описанный алгоритм работы повторяется.

Введение дополнительных регистров, а также коммутатора и распределителя каналов позволяет распараллеливать вычис пение корре пяди онных функций по идентичным каналам при исследовании случайных процессов как со слабо, так

:Ю и с сильно коррепированной выборкой, -. e. с потерей и без потерь информации между отсчетами, ч..о дает возможность обрабатывать кратковременные быстропротекающие процессы в реальном мас,ФЗ штабе времени.

Формула изобретения

Многоканальный коррелятор, содержащий в каждом канапе аналого-цифровой преобразователь, соединенный с выходным регистром, цифровую линию задержки, блок умножения, выход которого подключен к блоку усреднения, дополнительный аналого-цифровой преобразователь, соединенный с дополнительным выходным регистром, выход которого соединен с первыми входами блоков умножения каждого канала, входы всех аналого-цифровых преобразователей объединены и являются входом коррелятора, о т и ич а ю шийся тем, что, с цепью повышения точности, в коррелятор введен распределитель и в каждый канал— первый и второй регистры и коммутатор, причем в каждом канапе первый и второй входы коммутатора соединены соответственно с выходами первого и второго регистров, выход второго регистра подключен к первому входу первого регистра и ко входу цифровой линии задержки, выход которой соединен с первым входом второго регистра, вторые входы первого и второго регистров подключены к выходу выходного регистра, выход коммутатора каждого канала сое динен с соответствующим входом распределителя, выходы которого соединены со вторыми входами блоков умножения.

Источники информации, принятые во внимание при экспертизе

1. Жовинский В. H., Арховский В. Ф.

Корреляционные устройства. М.,"Энергия,".

1974, 2. Авторское свидетельство СССР

%292169, б 06 Г 15/34, 1971.

64634 1

Составитель В. Жовииский

Редактор С. Равва Техред И. Асталош Корректор H. Петрик

Заказ 1 13/39 Тираж 779 Подписное

ЦНИИ ПИ Гооударствениого комитета СССР по дедам изобретений и открытий

113035„Москва, Ж-35, Раушская иаб., д. 4/5

Фиииаи ППП "Патент", г. Ужгород, уд. Проектная, 4