Решаюший блок цифровой интегрирующей структуры

Иллюстрации

Показать всеРеферат

. - .а; 7 " 646;Б4

ОписАние

ИЗОБРЕТЕН ИЯ

И АВТОееСКОА4у СВИдВТВЛЬСуееу

Союз Советских

Социалистиыеских

Республик (61) дополнительное к авт. свил-ву

2 (51} М. K!I (22) Заявлено 28.03.77 (21) 2488925 18-24 с присоединением заявки-№ (23) Приоритет

<; 08 ii02

Гесударстеенный неинтет ссср ее делам нэобретеннй н откр9тнй

Опубликовано 05.02.7S.Бюллетень pfo 5 (53) УДК 681.14 . (088.8) Дата опубликования описания 07.02.79

A. В. Каляев, В. Ф. Гузик, Р. М. Крюков, И. М. Криворучко и В. H. Максименко (72) Авторы изобретения

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель. (54) РЕШАЮЩИЙ БЛОК 0ИФРОВОЙ ИНТЕГРИРУЮЩЕЙ

СТРУКТУРЫ

Изобретение относится к области вычислительной техники и предназначе-. но для использования в цифровой интет рирующей структуре.

Известны решающие блоки, содержащие два сумматора, регистр подынте-гральной функции, умножитель, регистр остатка, дополнительный сумматор Г1 (.

Недостатком его является недостаточное быстродействие.

Из известных устройств наиболее близкйм по технической сущности к данному изобретению является решающий блок цифровой интегрирующей структуры, содержащий сумматор входных приращений, сумматор подынтегральной функции, сумматор остатка интеграла, умножитель, регистр подынтегральной функции, регистр остатка интеграла, регистр выходного приращения, масштабный узел и элементы задержки, причем первый выход сумматора вход-. ных приращений соединен с первым входом сумматора подынтегральной функции, первый выход которого подклточен

2 через первый элемент задержки ко вто рому входу сумматора подынтегральной функции, а второй выход - к первым входам умножителя и регистра подынтегральной функции, выход которого сое5 динен с третьим входом сумматора псьдынтегральной функции первый выход умножителя соединен с первым входом сумматора остатка интеграла, первый выход которого соединен через второй элемент задержки со вторым входом сумматора подынтегральной функции, .а второй выход- с первыми входами регистра выходных приращений и регистра остатка интеграла, выход которого подключен к третьему входу сумматора остатка интеграла; первый выход масш» табного узла соединен с первым входом сумматора входных приращений, а .второй выход - со вторым входом регистра подынтегральной функции; первый вход масштабного узла, вторые входы умножителя, сумматора входных приращений, регистра остатка интеграла и третий вход регистра подынтегральной функции

46354

50

3 6

- являются информапионными входами бло ка, а первый выход регистра .выходног о приращения — информационным выходом блока; вгорой и третий входы масштабного узла, четвертый вход регистра подынтегральной функциви и третий вход регистра остатка интеграла являются управляющими входами блока, а второй выход регисгра выходного приращенияуороввввщим выходом боохо 21.

Недостатком известного блока является невысокое быстродействие. йель изобретения - повышение быстродействияхПобтавленная пелЪ достигается тем, что в блокв введены дополни"гельно регистры нодынтегральной функции и регистры остатка интеграла, причем второй и третий выходы сумматора входно го приращения соединены соответственЙО с четвертым и пя гым Входами сум матхора подыитегральиой функцйи, третий и четвертый выходы которого подключены соответственно к первйм входам первого и вторбго дополнительных регистров подынтегральиой функции и к третьему и четвертому входам умножителя, второй и третий выходы умножителя соединены соответственно с четвертым и пятым входами сумматора остатка интеграла, третий и четвертый выходы которого подключены соответсч веиио ко второму и третьему входам регистра выходного приращения и к первым входам йервого и второго дополнительных регистров остатка интеграла; вйходы дополнительных регистров подин тегральной функпии соединены соответственно с шестым и седьмым входами сумматора подынтегральной функции; выходй дюполнительныхв регистров остатка . интеграла соедиб неий соответственно с шестым и седьмым входами суммагора остатка интеграла; второй выход масш» табного узла соединен со вторыми входами дополнительных "регистров подйн: тегральной функции; третьи входы допол нительных регистров подынтегральной функции являются информационными входами блока, а их четвергые входыуправляюшими входами блока; вторые входы дополнительных регистров остатка: интеграла являются информационными . входами блока, а их третьи входыуправляюшими входамй блока.

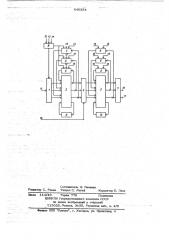

Блок-схема решающего блока пред ставлена на чертеже.

10 t5

ЗЗ

В состав решающего блока входят: сумматор 1 входных приращений, сумматор 2 подынтегральной функции, регистры 3 подынтегральной функции, умножитель 4, сумматор 5 остатка интеграла, регистры 6 остатка интеграла, регистр 7 выходных приращений, масштабный узел 8, элементы задержки 9, 10, информационные входы 11, 12, 13, управляющие входы 14, 15, информационный выход 16, управляю щий выход 17.

Устройство работает следующим образом.

По сигналу, поступающему иэ масштабного узла 8 в сумматор 1, происходит выделение восьмеричного кода числа "входных приращений, которое поступа- . ет на вход сумматора 2, где происходит сложение со значением содержимого регистров 3, поступающего на входы сумматора.2 в восьмеричйом коде. Йо лученное в сумматоре 2 значениейодын-. теграиьной функции в восьмеричном коде поступает на входы умножителя 4, где происходит его умножение на неза-, висимую переменную, постунающую по входу 13., В сумматоре 5 происходит сложение полученного в восьмеричном коде после умножителя 4 приращения интеграла с остатком интеграла, который хранится в регистрах 6.

В цепль перейоса сумматора 2 вклю.чен однотактный элемент задержки 9, который служит для образования пере носа при сложении приращения интеграла с текущим значением нодынтеграль ной функций.

В цепь" переноса сумматора 5 вклю чен однотактный элемент задержкй 1О, который служит для образования пере носа при сложении приращения интеграл иа с текущим значением остатка инте» грела.

Приращения интеграла с выхода сумматора 5 поступают в регистр 7, где происходит выделение выходных приращений интеграла на выход 16 решающего блока.

В случае переполнения разрядной сетки регистров 3, регистр 7 выдаст сигнал в устройство управления по выходу 17. в

ПредЛагаемый решающий блок позволяет увеличивать в 2,5-2,78 раз быстродействие, без ухудшения точ

646354 ности вычислений и увеличения затрат оборудования.

Формула изобретении $

Решающий блок цифровой интегрирую- щей структуры, содержащий сумматор . входных йриращений, сумматор подынтегральной фуикцйи, сумматор остатка 30 интеграла, умножитель, регистр йодынтегральной функции, регистр остатка ин . теграла, регйстр выходного приращения, масштабный узел и элемент задерж- ки, прячем первйй выход сумматора 15 входных приращений соединен с первым входом сумматора . подыйтегральной функции, первый выход которого. подключен через первый элзмеит задержки ко вто рому входу сумматора подййтегральной 20 функции, а второй выход - к первым входам умножителя и регистра подынтегральной функции, выход которого сое.динен с третьим входом сумматора подынтегральной функции, а первйй выход умножитела соединен с первым входом сумматора остатка - интеграла, первый выход которого соединен череэ второй элемент задержки со вторйм входом сумматора подынтегральной функции, а второй выход - с первыми входами регистра выходных приращений и регис ра ос.татка интеграла, выход которог6 подключен к третьему входу сумматора

ФЗ остатка интеграла; первмй выход масщ табного узла соединен с жрвым входом сумматора входных црирашений, а второй выход со вторым входом-регистра подынтегральной функпии, перви@ вход масштабного узла, вторые входя умно40 жителя, сумматора входных приращений, регистра остатка ин еграла и третиивход регистра подынтегральйой функции являются информационными входами бло» ка, а первый выход регистра выходного

45 приращения - янформапнонным вйходом блока; второй и третий .входь масштабйого узла, четвертый вход регяетра no" дынтегральной функции и третий вход регистра остатка йнтеграла являются:

50 управляющими входамй блока, а второй б. выход регистра выходного приращениауправляющим выходом блока, отличающийся тем, что, с пелью повышения быстродействия, в него введены дополнительно регистры подынтегральн6й функции и регистры остатка иЪтеграла, причем второй и третий выходы сумматора входного приращения соединены соответственно с четвертым и пятым входами сумматора йодынтег- . ральной функции, третий и четвертый вы" ходы которого подключены соответствен но к первым входам первого и второго дополнительных регистров подынтегральной функции и к третьему и четвертому входам умножитела, второй и третий выходы умножителя соединены соответственно с четвертым и пятым входами ,сумматора остатка интеграла, третий и четвертый выходы которого подключены соответственно ко второму и третьему входам регистра выходного йрирашония u K нервым входам первого и второго дополнителыых регистров остатка интеграла; выходы дополнительных регистров подынтегральной функции соединены соответственно с щесчмм и седьмым входами сумматора поцыйтегральной функпни; выходы дополнительных регистров остатка интеграла соединены corn ветственно с шестым и седьмым входами сумматора остатка интеграла; второй выход масштабного узла соединен со вторыми входами дополнительных регистров подыитегральной функции; третьи вы: ходы дополнительных регистров подынтегральйой функции являются информационными входами блока, а их четвертые входы - управляющими входами блока: вторые входы дополнительных регистров остатка интеграла являются информапиониыми входами блока, а их. третьи входыуправлякяцими входами блока.

Источники информации, принятые во внимание цри экспертизе

1. Авторское свидетельство СССР

И 410417, кл. (j 063 3./02, 1974.

2. Вычислительное устройство цифровой иигегрирующей структуры. Сб.

Цифровые модели Интегрирующей- структуры", Ч агаирог, 1970 .646354

/Я 15 g

Составитель Н. Палеева

Редактор С. Раьве . Техред С. Мигай Корректор E. Папп

Заказ 1 14/40. Тираж 779 Подписное

ИНИИПИ Государственного комитета СССР по делам изобретений и открытий

:113035, ÌîñKàà, Ж-35, Раушская наб., д. 4/5 ь34аюФую)Ф»Ы Ф» 1 ФЮ Фэ М5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4 г