Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1 1I 646374

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлеио16.12.76 (21) 2430439/18-24 с присоединением заявки № (51) М. Кл

С.1 1 С 1 5/00 (23) Приоритет

Государственный комнтет

СССР во делам нзобретеннй н открытий

Опубликовано 05,02.79.Бюллетень № 5

Дата опубликования описания08.02.79 (53) УДК 681 32.7 (088.8) (72) Автор изобретения

С, И, Хмельник

Ордена Октябрьской Революции всесоюзный государственный проектно-изыскательский и научно-исследовательский институт энергетических систем и электрических сетей "Знергосетьпроект" (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО ак при К g j (3) а„ при К = 1

Ьк =

Изобретение относится к области запоминающих устройств.

Одно из известных устройств содержит регистр опроса, регистр маски, ассоциативный накопитель, детекторы (1) .

Недостатком известного устройства являются большие аппаратурные затраты.

Из известных устройств наиболее близким техническим решением к данному изобретению является ассоциативное запоминающее устройство (АЗУ), содержащее регистры, накопитель, детектирующие блоки, одни входы которых подключены к блоку управления (21.

Накопитель известного АЗУ содержит большое количество сложных запоминающих элементов, позволяющих считывать информацию без ее разрушения с одновременным выпоЛнением некоторых логических функций, Следствием этого являются большие аппаратурные затраты и низкая надежность АЗУ.

Целью настояшего изобретения является упрощение и повышение надежности устройства.

Поставленная цель достигается тем, что устройство содержит дешифратор, ш ифратор и элементы ИЛИ, входы которых подключены к соответствуюшим выходам регистров, а выходы соединены с соответствующими входами дешифратора, другие входы детектирующих блоков подключены к выходам дешифратора, а выходы — к соответствующим входам шифратора.

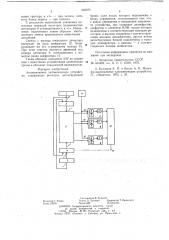

На чертеже изображена блок-схема предл о же н ного АЗ У.

Прежде чем описывать это АЗУ, рассмотрим одно из свойств полного дешифратора. Такой дешифратор имеет два и-разрядных входа и 2 выходов. На первый вход подается и-разрядный код

К (а) = а,... а„...а„, (1) а на второй вход код

К(Ь) = Ь1 ... Ь„... Ь„. (2)

Обычно первый вход присоединяется к единичному выходу некоторого регистра, а второй — к нулевому выходу этого регистра.

Если в этом регистре хранится код (1) числа а, то b< = а, и на а-выходе дешифратора появляется сигнал.

Предположим теперь, что слово К(Ь) не является инверсией слова К(а), а именно, 646374

При этом сигнал появится и на с-выходе, где код числа

-К(с) =а ...а1 ...сх

Пусть далее 1 к = )к " к

4 = кийк

1 при К + j на а -выходе с имеет вид (4) (5) (6) (7) Нулевой выход регистра I и единичный выход регистра 2 подключены ко входам элементов ИЛИ 3, а нулевые выходы регистров 1 и 2 — ко входам элементов ИЛИ 4.

Выходы элементов ИЛИ 3 и 4 соединены со входами дешифратора 5 (единичным и нулевым соответственно). Выходы дешифрато0 при К = j

Если разряды кодов (1) и (2) подчиняются соотношениям (5), (6), (7), то дешифратор возбуждает выходы и и с, соответствующие кодам (1) и (4) или, что одно и то же, кодам

6 ...6„- 1 61, ...6, 6i ...6 i О 6„, ...6,.

Таким образом, если разряды кодов (1) и (2), присоединенных к первому и второму входу полного дешифратора соответственно, удовлетворяют соотношениям (5), (б), (7), то дешифратор возбуждает выходы, соответствующие всем кодам, совпа- 20 дающим с кодом

К(В) =6 ...61 ...6, в тех разрядах, номера которых равны номерам разрядов кода

K(G) = " Ж "Tn имеющих единичное значение, Аналогично, если вместо выражения (7) имеет место соотношение

1 при К Ф ) и К + i

)к=

0 при К = j или К = i

30 то дешифратор возбуждает выходы, соответствующие кодам:

6 н .. 1;... 11 ... 6„

6 1 ... Ii, 0 ... 6n

6 i .. 0 .-- 11 ". 6п

61 ...0 ...01...6 35

Этот вывод можно продолжить и для большего числа нулевых разрядов 1,.

Предложенное АЗУ; схема которого изображена на чертеже, использует это свойство полного дешифратора.

Устройство содержит и-разрядный регистр 1 ключевого слова существенных разрядов K(G), и-разрядный регистр 2 базисного кода значений разрядов К(В), группу из и элементов ИЛИ 3 для выполнения поразрядной операции фл6., группу из и 45 элементов ИЛИ 4 для выполнения поразрядной операции раб, дешифратор 5, детектирующие блоки 6, в состав которых входят триггеры 7, блока 8 опроса состояния триггера и детекторы 9. Одни входы 10 блоков 6 подключены к блоку управления 11, выходы блоков 6 соединены со входами шифратора 12, имеющего выход 13. ра 5 соединены с другими входами детектирующих блоков 6.

Устройство работает следующим образом.

Для ассоциативного поиска в регистры 1 и 2 записываются ключевой и базисный коды соответственно. Для записи или стирания некоторого хода в регистр 1 записывается код 11...11, а в регистр 2 — данный код.

В соответствии с описанным свойством дешифратор возбуждает те выходы, которые соответствуют всем кодам, удовлетворяющим условию ассоциативного поиска по базисному К(В) и ключевому K(G) кодам. На этих выходах появляются единичные сигналы.

В частности, если,= 1 для всех К, то дешифратор 5 возбуждает единственный выход, соответствующий коду К(К) . Однако, как правило, в результате ассоциативного поиска некоторое подмножество выходов де шифратора 5 вырабатывает единичные сигналы. Эти сигналы поступают в детектирующие блоки 6. Далее эти сигналы обрабатываются по разному в зависимости от типа операции.

При записи или стирании кода, хранящегося в регистре 2, дешифратор 5 вырабатывает единичный сигнал на единственном выходе и этот сигнал поступает на вход триггера 7 соответствующего детектирующего блока 6. Триггер 7 устанавливается в

«1» (при записи) или в «О» (при стирании), что определяется типом управляющего сигнала на входе 10. В результате выполнения операций записи и стирания некоторое подмножество триггеров 7 оказывается в еди-. ничном состоянии. Каждый такой триггер идентифицирует код, хранящийся в АЗУ.

При ассоциативном поиске сигналы с выходов дешифратора 5 попадают на блоки 8 опроса состояния триггеров 7. Сигналы с результатом опроса поступают на детекторы 9.

Если триггер 7 находится в состоянии «1» то элемент памяти, входящий в состав детектора 9, устанавливается в «1». Мы будем говорить в таком случае, что детектор

9 устанавливается в «1». Таким образом, детектор устанавливается в «1» в том случае, если на соответствующем выходе дешифратора 5 возник единичный сигнал и соответствующий триггер 7 находится в единичном состоянии. Другими словами, детектор 9 устанавливается в «1», если код, соответствующий данному выходу дешифратора 5, удовлетворяет. условию поиска и входит. в подмножество кодов, предварительно записанных в АЗУ.

Коммутация сигналов, поступающих с выходов дешифратора 5, внутри детектирующих блоков производится с помощью управляющего блока 11 (управляющие сигналы на входе 10 открывают для сигналов дешифратора либо вход установки триггера в «О» — при стирании, либо вход уста646374

Составитель В. Рудаков

Редактор С. Равва Текред О. Луговая Корректор Т. Вашкович

Заказ 120/4! Тираж 680 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 1 3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная. 4 новки триггера в «1» — при записи, либо вход блока опроса — при поиске).

В результате выполнения указанных поисковых операций некоторое подмножество детекторов 9 устанавливается в «1». Извле- 5 чение полученного таким образом многозначного ответа производится известными способами.

Сигнал с выхода очередного детектора поступает на вход шифратора 12. Ответ возникает на его п-разрядном выходе 13.

При этом ответом является двоичный код номера детектора 9, совпадающего, с номером входа шифратора 12.

Таким образом, описанное АЗУ по сравнению с известными устройствами значительно проще и обладает повышенной надежностью.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее регистры, детектирующие блоки, одни входы которых подключены к блоку управления, отличающееся тем, что, с целью упрощения и повышения надежности устройства, оно содержит дешифратор, шифратор и элементы ИЛИ, входы которых подключены к соответствующим выходам регистров, а выходы соединены с соответствующими входами дешифратора, другие входы детектирующих блоков подключены к выходам дешифратора, а выходы — к соответствующим входам шифратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 434482, кл. G 11 С 15/00, 1970.

2. Балашов Е. П. и Кноль А. И. Многофункциональные запоминающие устройства.

Л., «Энергия», 1972, с. 51.