Стабилизатор переменного напряжения

Иллюстрации

Показать всеРеферат

(ii) 647670

Союз Советских

Социалистимеских

Республик

ОП ИСАНИЕ

И3ОБРЕТЕ Н Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлеио25.05.77 (21) 2490938/24-07 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано15.02.79. Бюллетень №6

Дата опубликования описания19.02.79 (51) М, Кл.

С» 05 F 1/56

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621,316. .722.1 (088.8) (72) Автор изобретения

В. И. Юдин (71) Заявитель (54) СТАБИЛИЗАТОР ПЕРЕМЕННОГО НА ПРЯДЕНИЯ

Изобретение относится к области электрорадиотехники; в частности к исто4никам питания, и может быть использовано в системах питания устройств автоматики и вычислительной техники.

Известен стабилизатор переменного напряжения (1) .

Наиболее близким к изобретению техническим решением является стабилизатор переменного напряжения, содержащий включенные последовательно в выходную шину параллельно соединенные регулирующие транзисторы противоположной по отношению друг к другу проводимости с диодами, каждый из которых включен в проводящем направлении по отношению к питающему напряжению последовательно с соответствующим регулирующим транзистором, причем диоды включены в цепь коллектора, а эмиттеры регулирующих транзисторов объединены и подключены к выводу для подключения нагрузки, параллельно выводам для подключения нагрузки подсоединены резисторные делители, средняя точка каждого из которых подключена к базе соответствующего усилительного транзистора, коллектором соединенного с базой соответствующего из регулирующих транзисторов одинаковой с усилительным транзистором проводимости, источник опорного напряжения и два резистора (2). Однако такой стабилизатор имеет невысокий КПД, так как каждый из стабилизаторов потребляет часть входной мощности, работая не в режиме стабилизации.

Целью изобретения является повышение

КПД и коэффициента стабилизации. Это достигается тем, что в предлагаемом стабилизаторе источник опорного напряжения вы10 полнен в виде последовательно соединенных резистора и включенных встречно двух стабилитрояов, подключенных параллельно выводам для подключения нагрузки, а к точке соединения резистора и стабилитронов под15 соединены эмиттеры усилительных транзисторов, причем каждый из резисторов включен между базой и коллектором соответствующего из регулирующих транзисторов.

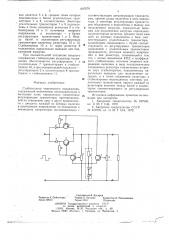

На чертеже дана принципйальная электрическая схема опйсываемого стабилиза20

В выходную шину последовательно включены регулирующие транзисторы 1 и 2 с диодами 3 и 4. Параллельно выводам для подключения нагрузки подключены резистор647670

Формула изобретения

1 Составитель В. Косырев

Редактор A. Пейсоченко Техред О. Луговая Корректор Д.Мельниченко

Заказ 309/41 Тираж 1014 Подписное

ЦНИИПИ Государственно-о комитета СССР по делам изобретений и откр ьп ий

I 13035, Москва, )К35, Раушская иаб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ные делители 5 и 6, средние точки которых подсоединены к базам усилительных транзисторов 7 и 8, соответственно. Эмиттеры усилительных транзисторов 7 и 8 подсоединены к точке соединения резистора 9 и стабилитронов 10 и 11 источника опорного напряжения, а коллекторы — к базам регулирующих транзисторов 1 и 2. Между базой и коллектором регулирующих транзисторов включены резисторы 12 и 13.

Стабилитроны 10 и ll через резистор 9 подключены параллельно выводам для подключения нагрузки.

При положительной полуволне входного напряжения стабилизации выходного напряжения обеспечивается регулирующим 1 и is усилительным 7 транзисторами и стабилитроном 10, а при отрицательной полуволне— регулирующим 2 и усилительным 8 транзисторами и стабилитроном 11.

Стабилизатор переменного напряжения, содержащий включенные последовательно в выходную шину параллельно соединенные регулирующие транзисторы противоположной по отношению друг к другу проводимости с диодами, каждый из которых включен в проводящем направлении по отношению к питающему напряжению последовательно с соответствующим регулирующим тра нзистором, причем диоды включены в цепь коллек.тора, а эмиттеры регулирующих транзисторов объединены и подключены к выводу для подключения нагрузки, параллельно выводам для подключения нагрузки подсоединены резисторные делители, средняя точка каждого из которых подключена к базе соответствующего усилительного транзистора, коллектором соединенного с базой соответствующего из регулирующих транзисторов одинаковой с усилительным транзистором проводимости, источник опорного напряженйя и два резистора, отличающийся тем, что, с целью повышения КПД и коэффициента стабилизации, источник опорного напряжения выполнен в виде последовательно соединенных резистора и включенных встречно двух стабилитронов, подключенных параллельно выводам для подключения нагрузки, а к точке .соединения резистора и стабилитронов подсоединены эмиттеры усилительных транзисторов, причем каждый из резисторов включен между базой и коллектором соответствующего из регулирующих транзисторов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство № 497565, кл. G 05 F 1/44, 1972.

2. Авторское свидетельство СССР № 457079, кл. G 05 F 1/44, 1972.