Устройство для извлечения квадратного корня

Иллюстрации

Показать всеРеферат

.Я

ИЗОБРЕТЕН ИЯ

«»647684

Союз Советских

Социалистических

Респубт мк (6/) дополнительное к авт. свил-ву (22) Заявлено 10.01,71 (21) 2443065/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.02.795юллетень ¹ 6

Дата опубликования описания 17.02.79! (51) М. Кл

С 06 F 7. 38

Государственный комитет

СССР по делам изооретений и открытий (53) УДК 681.3 (088.8) (72) А вторы В. И. Жабин, С. П. КобзаР, Во И. КэРнейчУк, В. А. ПэнэмаР нкэ, етзобретения Я. А. Рахлин, Л. А. Савченкэ, В. П. Тарасегкэ и Я. И. Тэрэшанкэ

Киевский ордена Ленина политехнический ин=титут (71) Заявитель имени 50-летия Великой Октябрьской сэциалистическэй ревэлюции (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ

Изобретенис относится к области вычислительной техники и может AblTt использовано в цифровых вычислительных машинах.

Известные устройства f!j для извлечения квадратного корня отличаются большой сложностью и содержат сумматор, регистр, счетчик, две группы элементов И, блок управления.

Наиболее близким по технической сущности к предложенному является устройство (2) для извлечения квадратного корня, содержащее регистр операнда, вспомогательный регистр, сумматор, первый вход которого подключен к единичному выходу младшего разряда регистра операнда.

Однако известное устройство требует больших аппаратурных затрат и, кроме того, не допускает использования в нем динамических регистров (например, интегральных сдвиговых регистров на МДП-структурах).

Цель предложенного изобретения — упрощение устройства и обеспечение возможности использования его в интегральном исполнении.

Указанная цель достигается тем, что устройство содержит регистр коррекции, блок формирования цифры, триггер, первый и второй элементы И, элементы ИЛИ и НЕ; vepвый тактирующий вход устройства подключен к первым входам регистра операнда, вспомогательного регистра и регистра коррекции, второй тактирующий вход устройства подключен к синхронизирующему входу триггера и ко входу элемента НЕ, выход которого соединен с первым входом перво о элемента И, выход которого подключен к единичному входу старшего разряда регистра операнда, первый вход элемента ИЛИ соединен с единичным выходом младшего разряда регистра коррекции, единичный вход старшего разряда которого подкл|очен к выходу элемента ИЛИ, второй вход которого соединен с выходом второго элемента

И, первый вход которого соединен с первым выходом блока формирования цифры, а его второй вход подключен к нулевому выходу триггера, первому входу блока формирования цифры и выходу устройства, единичный выход триггера подключен ко второму входу блока формирования цифры, третий вход которого подключен к выходу регистра коррекции, а четвертый вход соединен с единичным выходом младшего разряда вспомо647684 гательного регистра и с единичным входом старшего разряда вспомогательного регистра, второй выход блока формирования цифры соединен со вторым входом сумматора, выход которого подключен ко второму входу первого элемента И и ко входу триггера, а также тем, что блок формирования цифры содержит: первый и второй элементы

ИЛИ, первый и второй элементы И, элемент ИЛИ вЂ” НЕ,первый и второй элементы задержки,. первый вход первого элемента

ИЛИ подключен к первому входу элемента

ИЛИ вЂ” НЕ и к третьему входу блока формирования цифры, четвертый вход блока формирования цифры подключен ко вторым входам первого элемента ИЛИ и элемента ИЛИ-НЕ, через первый элемент задержки — к третьему входу первого элемента ИЛИ и через первый и второй элементы задержки — к третьему входу элемента ИЛИ вЂ” HE и к первому выходу блока формирования цифры, третий вход блока формирования цифры подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход — к первому входу второго элемента

ИЛИ, второй вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом элемента

ИЛИ вЂ” НЕ, а второй вход — с первым входом блока формирования цифры, выход второго элемента ИЛИ является вторым выходом блока формирования цифры.

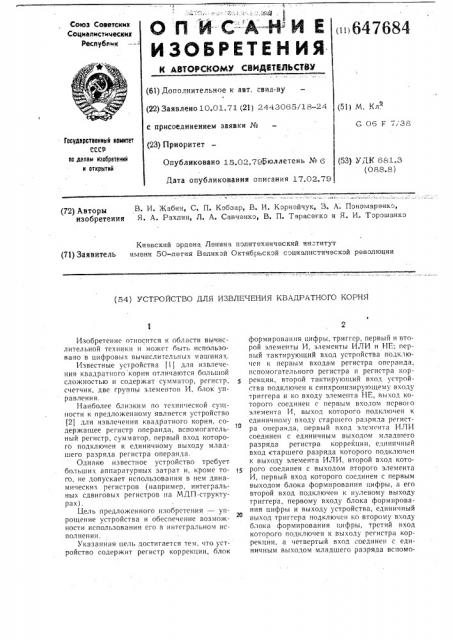

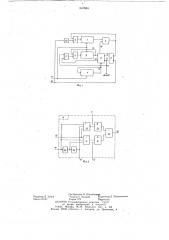

На фиг. 1 представлена схема устройства; на фиг. 2 — возможный вариант реализации блока формирования цифры.

Схема устройства содержит: регистр операнда 1, сумматор 2, триггер 3, первый и второй элементы И 4, 5, блок 6 формирования цифры, вспомогательный регистр 7, регистр коррекции 8, элемент ИЛИ 9, элемент НЕ IO, первый, второй, третий и четвертый входы соответственно 11, 12, 13, 14 блока формирования цифры, первый и второй выходы 15 и 16 блока формирования цифры, первый и второй тактирующие входы 17 и 18 устройства.

Схема блока формирования цифры (фиг. 2) содержит: первый и второй элементы ИЛИ 19, 20, первый и второй элементы

И 21, 22, элемент ИЛИ вЂ” НЕ 23, первый и второй элементы задержки 24, 25 соответственно.

Регистр 1 имеет (n + 5) разрядов, регистр 7 — (n + 3) разрядов и регистр

8 — (п + 4) разрядов, где п — разрядность опера нда.

В исходном состоянии в регистр 1 записан операнд, в регистре 7 — единицa çàïèсана в третьем слева разряде, в регистре

8 — все нули, триггер 3 находится в нулевом состоянии. На входах 12, 13, 14 существует нулевой сигнал, а на входе 11 — единичный сигнал. Поэтому на выходе 15 блока формирования цифры будет присутствовать нулевой сигнал, а на выходе 16 — «!», Таким образом, на выходе переноса сумматора будет сформирован единичный сигнал, 5 а на выходе суммы — сигнал, идентичный младшей цифре регистра операнда.

byäåì считать, что в каждом i-м такте (i = 1,2..., n + 4) каждого цикла на шине

17 появляется единичный тактирующий сигнал, а в (п + 4)-м такте каждого цикла на шине 8 появляется единичный тактирующий сигнал. Цикл работы устройства состоит из и + 4 тактов.

Рассмотрим работу устройства в 1-м такте произвольного цикла (i = l, 2 ..., и + 4).

15 На тактирующей шине 7 появляется единичный сигнал, который проходит на цепи сдвига вправо на один разряд регистров 1, 7 и 8. В освободившийся старший разряд регистра через элемент И 4 записывается

20 цифра, полученная на выходе суммы сумматора 2 (это возможно ввиду отсутствия единичного сигнала на шине 18 и, следовательно, наличия его на выходе элемента HE !

О). В старший разряд регистра 7 записывается цифра, бывшая в младшем разряде

25 этого регистра в предыдущем такте. Если двумя тактами ранее в младшем разряде регистра 7 находилась единица, то формирователь 6 формирует единичный сигнал на шине 15. Если в этом же такте триггер 3 находится в нулевом состоянии, то на выходе элемента И 5 и элемента ИЛИ 9 появляется единичный сигнал и в следующем такте в старший разряд регистра 8 записывается единица. Во всех остальных случаях в старший разряд регистра 8 записывается

35 цифра, быв и а я в предыдущем гакте в младшем разряде этого регистра. Если триггер

3 находится в нулевом состоянии (т. е. на шине 11 присутствует единичный сигнал), то на втором выходе формирователя 6 единичный сигнал появится только в случае

40 отсутствия единичного сигнала на шинах

13, 14 и 15 (отсутствия единиц в младших разрядах регистра 8 в данном такте и регистра 7 в этом такте и двумя тактами ранее). Если же триггер 3 находится в. единичном состоянии (на шине 12 установлен единичный сигнал), то единичный сигнал на выходе 16 появится в следующих случаях: либо в младшем разряде регистра 8 записана единица (на шине 13 имеется еди-. ничный сигнал), либо в младшем разряде регистра 7 единица находилась в прошлом такте или находится в этом такте (что соответствует единичному сигналу на шине

14). На входы сумматора 2 поступают сигналы с блока 6 с цепи переноса сумматора, а также сигнал из регистра 1, соответствующий значению цифры из его младшего разряда. В (п + 4)-м такте каждого цикла на тактирующей шине 18 появляется единичный сигнал, который поступает на вход элемента НЕ 10 и на синхронизирующий

647684

Формула изобретения вход триггера 3. На выходе элемента 10 единичный сигнал исчезает и в старший разряд регистра 1 записывается ноль в следующем такте. Триггер 3 изменяет свое состояние в соответствии с сигналом на выходе суммьг сумматора 2. Кроме этого в первом цикле одновременно с появлением сигнала на шине 18 осуществляется сброс в нуль регистра 8. Результат появляется на выходной шине, связанной с нулевым выходом триггера 3, последовательно со старших разрядов.

Очередная цифра результата формируется в конце каждого цикла в его (п + 4)-м такте.

Рассмотрим цифровой пример. Пусть необходимо вычислить квадратный корень из

9 = (1001)ф. Результат будет равен 3 =

= (0011) Ь.

Предложенное устройство является устройством последовательного действия и применение в нем регистров в интегральном исполнении на основе гЧДП-структур позволяет значительно снизить стоимость, уменьшить габариты устройства и повысить его надежность.

1. Устройство для извлечения квадратного корня, содержащее регистр операнда, вспомогательный регистр, сумматор, первый вход которого подключен к единичному выходу младшего разряда регистра операнда, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр коррекции, блок формирования цифры, триггер, первый и второй элементы И, элементы ИЛИ и НЕ, первый тактирующий вход устройства подключен к первым входам регистра операнда, вспомогательного регистра и регистра коррекции, второй тактирующий вход устройства подключен к синхронизирующему входу триггера и ко входу элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого подклк)чен к единичному входу старшего разряда регистра операнда, первый вход элемента ИЛИ соединен с единичным выходом младшего разряда регистра коррекции, единичный вход старнгего рязряда которого подключен

l0

2S зо зз

4О

45 к выходу элемента ИЛИ, второй вход которого соединен с выходом второго элемента

И, первый вход которого соединен с первым выходом блока формирования цифры, а его второй вход подключен к нулевому выходу триггера, первому входу блока формирования цифры и выходу устройства, единичный выход триггера подключен ко второму входу блока формирования цифры, третий вход которого подключен к выходу регистра коррекции, а четвертый вход соединен с единичным выходом младшего разряда вспомогательного регистра и с елин чным входом старшего разряда вспомогательного регистра, второй выход блока формирования цифры соединен со вторым входом сумматора, выход которого подклгочсн ко второму входупервого элемента И и ко входу триггера.

2. Устройство по и. 1, отличающесcsl тем, что блок формирования цифры содержит первый и второй элементы ИЛИ, первый и второй элементы И, элемент ИЛИ вЂ” HE, первый и второй элементы задержки, первый вход первого элемента ИЛИ подключен к первому входу элемента ИЛИ вЂ” НЕ и к третьему входу блока формирования цифры, четвертый вход блока формирования цифры подключен ко вторым входам первого элемента ИЛИ и элемента ИЛИ---НЕ, через первый элемент задержки — к третьему входу первого элемента ИЛИ и через первый и второй элементы задержки — к третьему входу элемента ИЛИ- — НЕ и к первому выходу блока формирования цифры, второй вход блока формирования цифры подключен к первому входу первого элемента

И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход — к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом элемента ИЛИ вЂ” НЕ, а второй вход — с первым входом блока фор- мирования цифры, выход второго элемента

ИЛИ является вторым выходом блока формирования цифры.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 435522, кл. G 06 F 7 / 38, 1972, 2. П атент Я пон ии № 50 — 7900, кл. 97(7) Е32, 1975.

647684

Рг. s

uz. 2

Составитель Н. Шелобанова

Техред О. Луговая Корректор Д. Мельниченко

Тираж 779 Подписное (1НИИПИ Государственного комитета СССР по дел ам изобретен ий и от к р brr и и

113035, Москва, Ж-З5, Раугиская иаб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Д. Зубов

Заказ 311/41