Преобразователь время-вероятность

Иллюстрации

Показать всеРеферат

о п и с-" À- a "É 1

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик п,647693

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт, свил-ву (22) Заявлено05.03.77 (21) 2461165/1824

Я 1 (51) M. Кл

Cj 06 F 15/36 с прпсоелииеиием заявки (е (23) Приоритет

Гааударстеенный иамитет

СССР па делам изабретений н аткрытнй

Опубликовано 15.02.79Г>юллетеиь _#_. 6

1ата опубликования описания 18.02.79 (53) УДК 681. 3 (088. 8) В. Г. Корчагин, h. С. Мартыненко, Ю. В;. Садомов и Л. М. Хохлов (72) Авторы изобретения

Государственное союзное конструкторско-технологическое бюро по проектированию счетных машин и Опытный завод (71) Заявители (54) ПРЕОБРЛЗОВ ТЕЛЬ ВРЕМЯ-ВЕРОЯТНОСТЬ

Изобретение относится к обпасти вычиспитепьпой техники и может найти испопьзование в вероятностных машинах и устройствах при решении различных задач

В настоящее время вырос и продолжает развиваться обширный класс вероятностных вычиспитепьных машин, которые оперируют со специальным машинным языком, заданным в вероятностной фор-. ме.

Составной частью вероятностных вычислительных машии, обеспечивающих ввод и обработку исходной информации в автол.атическом режиме, являются преобраэоватепи информации и, в частности, преобразователи вида время-вероятность.

Известно устройство дпя преобразования аналоговой, в частности, временной информации в вероятностную (lj.

Это устройство отличается спожиостью, так как решение задачи преобразования в нем осуг ествпяется по двухступенчатой схеме, на первой ступени происходит преобразование вида время-код, а на второй - код-вероятность, Это обстоятельство приводит к большим потерям скорости преобразования, что отрицатепьно сказывается на техникоэкономических показателях вычислительной системы в цепом.

Наиболее .близким техническим решением к предпагаемому явпяется пре10 обраэоватепь время-вероятность, содержащий датчик случайных чисел, выход которого соединен с первым входом первого триггера и с первым выходом схемы сравнения, второй выход которой

15 является выходом преобразователя, первый вход схемы сравнения подключен к входу элемента задержки и к выходу эпемента И, первый вход которого соединен с генератором импульсов, а второй вход - с выходом первоготриггера, второй вход которого подключен к первому входу второго триггера и явпяется первым входом преобраэоватепя, и к

25 случая:

1. Коды равны. Содержимое счетчика

d уменьшается на единицу, такт опроса повторяется, 2. Преобразуемый интервал времени меньше случайного интервала времени.

На вход преобразователя до окончания случайного временного интервала пришел импуп с конец интервала". В этом спу

"( чае схема 6 сравнения формирует на и (( информационном выходе логическую 1, явпяк щукгя вероятностно-кодированным значением преобразованного временного интервала.

5 .6476 управляющему входу блока элементов И, группа информационных входов которого соединена с соответствующими выходами датчика случайных чисел, при этом второй вход триггера является вторым входом 5 преобразователя, а выход второго триггера подключен к второму входу схемы сравнения(2) .

В этом преобразоватепе достигнуто .. значительное повышение скорости пре- to образования при одновременном сохранении точности преобразования и сложности схемы.

Недостатком данного устройства является то, что точность преобразова- 15 ния (шаг квантования) находится в пряч4ой зависимости от разрядности составпяющцх схему элементов, таких как регистр сдвига, генератора случайных чисел, вентипьной группы. 20

Белью настоящего изобретения явпяется упрощение схемы преобразователя и повышение точности устройства.

Поставленная цепь достигается тем, что в преобразователь введены вычитаюший счетчик и элемент ИЛИ, выход которого соединен с третьим входом схемы сравнения, а входы подключены к группе разрядных выходов вычитаюшего счетчика, группа разрядных входов ко- ЗО торого соединена с выходами блока элементов И, вход вычитающего счетчика соединен с выходом элемента задержки.

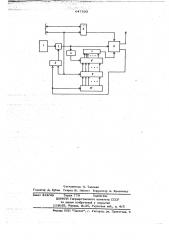

На чертеже представлена блок-схема 55 преобразователя.

Устройство состоит из генератора импульсов 1, элемента 2 И первого триггера 3, элемента 4 задержки, второго триггера 5, схем ы 6 сравнения, 4О элемента 7 ИЛИ, вычитающего счетчика 8, бпока 9 элементов И, датчика 10 случайных чисел.

На входы триггера 5 поступают с датчика временного интервала (на чер- 45 теже не показан) импульсы, соответствующие начану и концу преобразуемого интервала времени. Результат преобразования снимается с информационного входа схемы 6 и подается на внешние устройства (на чертеже не показаны).

Преобразователь работает следующим образом.

Перед начапом работы все блоки и элементы преобразователя находятся

55 в исходном (нулевом) состоянии, при этом датчик 10 случайных чисел формирует -разрядный двоичный код чисел, имеющих равномерный закон рас» предел ения.

Начало работы преобразоватепя определяется появлением на одном его входе импуцьса начало интервала, который устанавливает триггеры 3 и 5 в единичные состояние и, включая блок

9, обеспечивает поразрядную перезапись кода из датчика 10 в счетчик 8. Элемент 2 открывается, так что тактовые импульсы с генератора 1 поступают через элемент 4 задержки на счет ный вход вычитаюшего счетчика 8, а также на опросный вход схемы 6, кото-рая вырабатывает B каждом такте результат сравнения по кодам, хранящимся в триггере 5 и снимаемый с выхода эпе ента 7. Таким образом, преобразуемый интервал времени сравнивается со случайным временным интервалом, величина которого равна произведению периода тактовых импульсов на случайное двоичное число, занесенное в счетчик в начале цикла преобразования.

Окончание случайного интервала времени (если он длиннее преобразуемого интервала времени) определяется моментом, при котором содержимое счетчика 8 становится равным нушо и ко торый (момент) реализуется путем потактного вычитания единицы из текущего содержимого счетчика и появлением на выходе эпемента "ИЛИ кода О.

По результатам каждого такта опроса схемы 6 сравнения возможны три

Одновременно с управляющего выхода схемы 6 на входы триггера 3 и датчика 10 поступает сигнап окончания цикла преобразования. При этом элемент 2 запирается, а датчик 10 формирует на своих выходах код очередного случайного числа: преобразоватепь готов к приему очередной информации.

3. Преобразуемый интервал времени больше спучайного временного интервапа

Схема 6 сравнения формирует на информационном выходе логический О", явпяюшийся вероятностно-кодированным значением преобразованного интервала времени. Подготовка к очередному цикпу преобразования далее осушествпяется как это описано в п. 2.

Предноженное устройство выгодно отличается от прототипа значительной простотой, что проявилось, в частности, в замене и — разрядного сдвигового регистра, П --разрядной рептильной . группы (бпок 9) соответственно на (op Ч ) -разрядный счетчик и (1о П1разрядную вентипьную группу, а rl - разрядный генератор модифицированных спучайных двоичных чисел, сос:,тояший из датчика двоичных чисеп и комбинационной ll — разрядной схемы, заменен на (80(< и )-разрядный датчик случайных чисе п.

Так, при разрядности указанных элементов прототипа - 128, разрядность элементов настояшего изобретения составит всего 7 единиц, что открывает, как видно, немалые возможности для сушественного увепичения точности устройства (за счет уменьшения шага квантования).

Формула изобретения

Преобразователь время-вероятность, содержаший датчик случайных чисел, вход которого соединен с первым входом первого триггера и с первым входом

647693 схемы сравнения, второй выход которой явпяется выходом преобразователя, пер. вый вход схемы сравнения подключен к выходу элемента задержки и к выходу

5 эпемента И, первый вход которого соединен с генератором импульсов, а втс рой вход - с выходом первого триггера, второй вход которого подключен к первому входу второго триггера и явпяется

10 первым входом преобразователя, и к управляюшему входу блока элементов И, группа информационных входов которого соединена с с ответствующими выходами датчика случайных чисел, при этом

15 второй вход второго триггера является вторым входом преобразователя, а выход второго триггера подкпючен к второму входу схемы сравнения, о т п ичаюшийся тем,что,сцепью упрошения преобразователя и повышения его точности, в него введены вычитак ший счетчик и элемент ИЛИ, выход которого соединен с третьим входом схемы сравнения, а входы подключены .к группе разрядных выходов вычитаюшего счетчика, группа разрядных входов которого соединена с выходами блока эпементов

И, вход вычитаюшего счетчика соединен с выходом элемента задержки.

Источники информации, принятые во внимание при экспертизе

1. Мирский Г. Я. Аппаратурное определение характеристик случайных процесссв, М., Энергия, 1972, с. 425.

2. Заявка Мо2138490/24, кп. Cj06F15/36, 1975, по которой принято попожитепьное решение о выдаче авторского свидетепьства.!

647693

Составитель Н. Талеева

Редактор Д. Зубов Техред lO. Ниймет Корректор А. Кравченко

Заказ 313/42 Тйраж 779 Подписйое

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", r, Ужгород, ул. Проектная, 4