Устройство для умножения и деления нормализованных чисел

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 190476(21) 2349039/18-24 с присоединением заявки № (23) Приоритет

Государственный комитет

СССР но делам изобретений н открытий (53) УДК 581. 325

{088 . 8) Опубликовано 250279. Ьюллетень №

Дата опубликования описания 25.0279 (72) Автор изобретения

Б.A. Баклан

Государственное союзное конструкторскотехнологиЧеское бюро по проектированию счетных машин и Опытный завод (Я) Заявители

{54) УстРОЙстВО ДлЯ умнО»{ениЯ и Деления

НОРМАЛИЗОВАННЫХ ЧИСЕЛ торого соединен с выходом блока вычисления обри †н велкчины, а третий вход блока формирования частичных прокзведений соединен с выходом второго регистра, второй выход сумматора частичных произведений соединен с вторым входом второго регистра (21.

Целью изобретения является упрощение устройства и увеличение быстродействия при Выполнении деления

Достигается это тем, что в устройство введены элемент И и коммутатор множителя, первый вход которого соединен с выходом блока управления, а выход — с четвертым входом блока формирования частичных произведений, второй вход коммутатора множителя соединен с выходом второго регистра, первый вход элемента И соединен с вторым выходом сумматора частичных произведений, второй вход элемента И вЂ” с вы ходом блока управления, выход элемента И соединен с пятым входом блока формирования частичных произведений и входом блока управления.

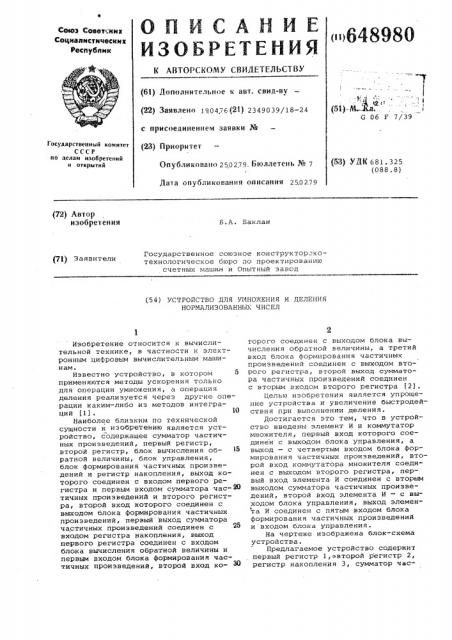

На чертеже изображена блок-схема устройства.

Предлагаемое устройство содержит первый регистр 1, второй регистр 2, регистр накопления 3, сумматор час Изобретение относится к вычислительной технике, в частности к электронным цифровым вычислительным машинам.

Известно устройство, в котором применяются методы ускорения только для операции умно>кения, а операция деления реализуется через другие операции каким-либо из методов интеграций (1). Ю

Наиболее близким по технической сущности к изобретению является устройство, содержащее сумматор частичных произведений, первый регистр, второй регистр, блок вычисления об- S ратной величины, блок управления, блок формирования частичных произведений и регистр накопления, выход которого соединен с входом первого регистра и первым входом сумматора час-+ тичных произведений и второго регистра, второй вход которого соединен с выходом блока формирования частичных произведений, первый выход сумматора частичных произведений соединен с входом регистра Накопления, выход первого регистра соединен с входом блока вычисления обратной величины и первым входом блока формирования частичных произведений, второй вход кот (51) -мйл.

G 06 F 7/39 тичных произведений 4, блок уг! р:(в(-. ленин 5, блок б формирования -.:;с д". ных произведений, блок 7 вы !!. -.ння

ОбратнОй Величины е.(1емс :н .т (! .Мутатор 1лнажителя 9„

Устройство рабат 1sT следу(в! 11н((::. - Разом. я

Операции умнажеи11Я 11 делен!::л !>1.:.1-полняются над и-разрядным(1 нс>р(»!:; H-зов анными числами „вел1(ч11!1(1 ка (: рых заключена ь диапазоне ат -- - до 1, П

Где П1 ОС11ОВННИЕ СИСТЕМЫ С -1Н(>ЛЕН,.(л .

При выполнении операции умнс же(:.Ня множитель располагается в реги(T1.-: 2, мнОжимОе в реГистре 1 прои зве дение образуется в регистр(. 2 (с:.:;-;,р.;-:,и(.—;

Разряды) / в регистае 3 (млав>(;!(:= сн>-.(РЯДЫ!) . ЭЛЕМЕНТ И 8 СИГНаЛОМ ИЗ бЛСЯ».-1 управления 5 закрь";т .

БлОк б фарм>!Рован(!л части.! ((1!.;

ПРОИЗВРДен11 Й высоабатыв а(эт 1, :: (;i-! н!»1 .". произведения мнажимага на г1-ус i!i.

2(! из K (K > 1) разрядов мнажи.е 1:., тупающие из регистра 2 153p(3-. ко н:утатор множителя 9, Кс>- (му-i i-г.: р налом и3 блО (1 усlравлен(5! нс>ро с ((>" чается таким образом, что при у(.(но-жении очередная группа разр;i!!!3(1 м: жителя Выбирае 1cR H 3 К стар(яi >( рядов регистра 2, а при дел:нин из K млад!1(их разрядов это1 с х;,=- р( гист.>а. Сумматор частичных про!(ЗВ=-Дений 4 Выполн Яет с(10}1 ение с »1. ».-,-:,»(с».- »(н

ГО Рег((стра 3 с О 1еаедным -(айтсн(((В>» произведением, результат сложеня i

Э аПИСЫВ с(ЕТС 5! В РЕГИСТР Н аl(ОП> :-..Н ii B разрядность которого увеличена

K+1 ра зряд, ПЕррд HaiIНЛОМ ЧМI.(-, ((,Н (;., которое начинается са стар; !.:!!с рн 3,:...-дав, регистр 3 сбрасывается 1-. (Оль

В первом цикле умножения на н.";сн блока б формирования части:=",-:ы:-: .(Рс:— изведений поступают мно>тимо(нз ре-Гистра 1 л К c арших разрядсн ii!o:(Hтел я из ре 1 ис гаа 2 через 1» й!»i ; =! "(. p множителЯ 9 . B блоке 6 ви10>н1н(.. (i: Я их перемнажс.ние и частичнсе дение IIocT упает на Вход су!л»(нт р» 4( частичных произведений 4, где с(слссць(— вается с содержимым регистра 3 . Результат сложения записывается В реГистр 3...затем ПРОНЭВОДНТ<- л:- Дв -г влево на К разрядов регистра::; 2 (, 3i

:5 при этОм сОдРржимае старших й(»з:. IBОВ

Регистра 3 передается н м>;адн.:(й разряды регистра 2, В кажДом послРДующем ii!! Кла i :i старших разрядов регистра 2 1»э! сз коммутатор 9 выбирается о -1(3pciн»1; группа раэрядОВ мнО>кителя и о. 1! i й:=(Н-"

НЫЕ ДЕЙСТВИЯ IOBTOP511I>TC II .

Возника(о((((ле прн суммиров (!Ии (айги»1ных ПРО>13ведений переносы В с1 ар шие разряды, перешедшие из г>егнстра б()

3 в регистр 2, подаются с вы;;с>д, сум матора 4 на счетный вход рег>стр» 2, который выполнен В Виде ре1. c":! Bсчетчика. После зыполнениli --,- - !(н;<к — разрядност(. сом:-:о к((TO б--, -:",,-В регистре 2 образуется И старших р,.-р>!((с>:: I!pop введений, В регистре 3 лн.(:;.:,-(я половина нраизведений на э :. o:, :,,1(ро!.,ей с у(лнОжени я заканчиВается .

:::и(11 !1Ы((олнении деления вначале дер:- 3.:(ешается В регистре 2 а де. вЂ,. Те!!1 — В регистре 1. Операция делен-.:.л раз . И1>ается на 2 этапа. На первом э .а!.е а((ределяется приближенное зна,paтнай величины делителя D u

Н=. (O,ÏЯТ(Я ЗиаЧЕНИЯ

В>, В =- 1 — В!> ....,,, (1)

:,Р С вЂ” д елимае,"

— целитель;

0„. — пг>иближеннае значение вели-!

"»îi-.,:iocTü определения величины 0

Дс;;!;..!=; Ыть такой, чтобы обеспечива-! -, .;;. : :.1 Ц Q Г(l! Е Н и Е Е$ С Л! O B H Я б «В m-k (2) l (ну. (а

Л вЂ” — - (<- m " ) 2 < =„, П;ли-i!iÍ:= 1>„ определяется с помощью (.н(>!(а ычисления обратной величины 7, ;-;".сос:!н. мoi:ет быть выполнен,. напри!

iH ocHoBe таблины обратных ве. . :. (:-.< ii .

B:сод б !IОК а 7 и 3 реГистра 1 пО ,".; . -тс л К+2 с1арс(!Их разрядов делителя

0 . „. .D соо г.ие1 ств1»и им В

К! 2 :ллно обрд I Hых Величин блока 7

11остс(н. (Сна (К+1) разрядное число 1>,, нр(! являющее собой (к+1) старший (>н,р q -;H;-!Тнсго от деления 1 на (>сНЭ а 7 ВЕЛИЧНйа Г „,. ПадаЕтСЯ В

"..:»а: б йрм«pав(1;!Ия частичных произве -нн, оннавремеHHo на друГой ВхОд с !((к-" б поступает делитель из ре1.

Произведен>1е В 0 образуется за (н(:< (а. В и рвам цикле в блоке 6 ,..,..;!Ролан(ля .1астичных произведений н;:::с:.:... -: тся перемножение делителя В (:;,iB .ò:..oè р=:Bðëä величины П,получен,(.(. 1(стичнае 1(роизведение через сум4 нередаетс5 в регистр 3. Зат.-»., . . блоке б образуется произведение (!а К дробных разр5!Дов величины Р,> ,I полученное частичное произведение (;!Рибавляется к г!редварительно сдвину;. »>му влево содержимому регистра 3.

Величина E находится как дополне«роизведения В В,до 1. В соответс.ТВН;; с условием 2, в старших разря-.ах с .>>.eBol.n до (К-1)-й величина Е содержит нули. Для их устранения

i(рои=ьодI«тсл сдвиг регистра 3 влево на К разрядов и затем его содержимое нс ред 33!ся в регистр 1. Цля вычисленил ве.:. (ины (,„= С П на вход блока ь (>с>р>л(!ровани5! Частичных произведеHi(Pi. по (аются делимое С из регистра 2 и величин- . D . .Иэ блока 7. !".х проиэе,,ение также выполняется на 2 цик.(а I 1 33yльтат образуется в регист-!

1>L J *

Второй этali деления основан на ,:>(vò;ó;èö1iõ соотношениях. Пусть частб 4»8980

1011 1111 1010

0111 1001

Aî

1 .Е х 1011

Р. =l

Е х Р3

1100 0111 0011.

0000 1011

1100 0111 1110

11000111 1.110 ОООО

0100 1101

2. Е х 0111

P„=i

1.1 01

\ 011

11001000 0010

0000

11001000 0011 1000

О 1 1

=-0 ) 3

=О) 3. Е х 0

А. (Р„» (-дни1A„(P„

Сдвиг

2 К, 3 к — -> к50 ное А= — умножив числитель и зна лев с

НатЕЛЬ На ВоПОЛУЧИМ А= „ вЂ, ОТКУДа

A =Ao+ ЕА=А»В(О .1„(g ") -(2к- ) о К,7K-»> Ф

+»» Ь -(ЗК-») 2К К-» где а. — группа из К разрядов част- 5 ного;

Ц вЂ” номер старшего разряда группы; — номер младшего разряда группы. О

Так как условия 1 и 2 выполнены, то величины A и Ао совпадают с точностью до 1 {к-1) разряда. следовательно, при проведении вычислений по формуле (3), н первом цикле н качестне множителя может быть использована группа К ста.рших разрядон

I ао к „величины Aî

После ныполнения цикла умножения полученное частичное произведенлс

Е а о к» прибавляется к величине

Я

А в результа-е чего н (К-i)-й разряд суммы может возникнуть 1 переноса Р », что эквивалентно увеличению множителя на 1 младшего разряда группы и должно быть учтено дополни- 25

-(К-»1 тельным прибавлением величины Е 1п к ранее полученной сумме. В резуль— тате выполненных действий полу 1им величину

Е (О»о К-» + Рк-„) »

30 суммарное приращение которой

E{+< „Р ),„,-(K-f ) -K t -(K-») -(>»-» )

> по отношению к величине А не пренышает 1 (К-1)-го разряда. Подставив значение неличины А„в выражение (3), получим

Величин 1 A » 4 совпадают с то ностью до 1 (2к — 1)-го разряда, поэтому в качестве второй группы разрядов множителя примем соответствующие разря- @

I ды величины A — а „,. „и выполним действия, аналогичные описанным, в результате чего получим величину и (зк-» 7 — «к-», >

A=Ag (с(гк,3к-л »11 о»зк>+к-» " + )

t"

Выполним аналогичные вычисления вЂ, раз

К

ПОЛУЧИМ (>»Фк-,) 55

А - A ы. E (а,, „„. (-((2 к-1) (1+К,И+аК-a + ) так как величина стоящая н скобках

) меньше 1 н » и Е < ю то

A A -(»» к- ii . 60 (»rn

К г.е. ошибка вычисления частного после — циклов не превышает 1(и+к †11 -го я

1< разряда. Например, пусть т = 2, К .=- 4, С = О 10) 10) 1,8 = 0,10001700 на 1-ом этапе деления определяем

D 1,1100 и вычисляем

А =.- 1.011111110100. Е = 0.00001011.

ВтОрОй этап деления начинаем с умножения Е на 4 старших разряда ве личины А,При э o1» K старших нулей величины Е учитываются начальным сдвигом А„-, на К разрядов влево.

Сдвиг A. влево на К разрядон

Сцвиг А9. влевО на К разОЯ>>ов

1100 10000011 1600 ОООО

0010 0001 100 10000011 1010 0001

1100 100000111010 0001 0000

0110 1110

1100 1000 0011 1010 011.1 1110

ll00 1000 0011 1010 0111 1110 ОООО так как дробь периодическое, то дальше будут псвтОрЯтьсЯ шаги 2,3,4.

Прямое деление дает следующий результат:

0.10001100 — — 1..>ДОЯСОООЩС1()10()()СОИ(Сравнение результатов показывает, что ошибка после 4-х циклон вычислений менее 1 19-го разряда.

Предлагаемое устройство в процессе ныполнения 2-го этапа деления функционирует следующим образом. ПО сигналу из блока управления 5 коммутатор множителя 9 переключается на выборку групп К младших разрядов рег1»стра 2, а также ОТ1»рывается элемент И 8 для прохождения сигнала пeреноса с выхода суммагора 4.

Вниду того, что вели гина Е была сдвинута влево на К разрядов, то н начале 1-го цикла г;роизнодится сдвиг регистров 2 и 3 также на К разрядон влево, при этом содержимое старших К

648980 разрядов регистра 3 переписывается в младшие разряды регистра 2, откуда через коммутатор 9 поступает в блок 6 формирования частичных произведений, одновременно на другой вход блока 6 поступает множимое из регистра 1. В блоке 6 сомножители перемножаются и б частичное произведение подается на вход сумматора 4, где складывается с содержимым регистра 3.

Перенос с выхода сумматора 4 поступает на регистр 2 и одновременно, )Q через элемент И 8 — в блок управления 5 и в блок формирования частичных произведений 6. Блок управления 5 запрещает передачу разрядов множителя через коммутатор 9 на вход блока 6 формирования частичных произведений, через который в это время по сигналу от элемента И 8 множимое из регистра

1 подается на вход сумматора 4 для дополнительного сложения с содержимым регистра 3. Результат дополнительного сложения с выхода сумматора 4 также записывается в регистр 3. После выполнения дополнительного сло>ке. ния производится переход к выполнению второго цикла. Если при выполнении суммирования содержимого регистра 3 и частичного произведения, сигнал переноса иэ сумматора 4 не поступает, то сигнал на выходе вертиля дополнительного сложения 8 отсутст- 30 вует и переход к следующему циклу вычислений производится непосредственно после прибавления частичного произведения, без выполнения дополнительного сложения. Зд

Второй цикл вычислений также начинается со сдвига регистров 2 и 3 влево на К разрядов, в результате которого в младших разрядах регистра

2 оказываются К очередных разрядов множителя. И все вычисления выполняются аналогично 1-му циклу. После выполнения + циклон в регистре 2 будут находиться N старших разрядов частного, в регистре 3 — число, которое совпадает с последующими разрядами частного с точностью (и+к-1)го разряда.

Предлагаемое устройство обеспечивает выполнение умножения за -и- циклов, каждый из которых включает в Я себя получение и накопление частичного произведения. Для выполнения деления дополнительно требуется четыре аналогичных цикла при вычислении величин Е и А,а также от 0 до — цик-55

>> лов сложения. Таким образом, в зависимости от длительности и количества дополнительных циклов сложения, время деления 1 в 1,5-2 раза превышает время умножения.

При этом аппаратура ускорения операции умножения в блоке частичных произведений полностью используется и при выполнении деления.

Формула изобретения

Устройство для умножения и деления нормализованных чисел, содержащее сумматор частичных произведений, первый регистр, второй регистр, блок вычисления обратной величины, блок управления, блок формирования частичных произведений и регистр накопления, выход которого соединен с входом первого регистра и первым входом второго регистра и сумматора частичных произведений, второй вход которого соединен с выходом блока формирования частичны>: произведений, первый выход сумматора частичных произведений соединен с входом регистра накопления, выход первого регистра соединен с входом блока вычисления обратной величины и первым входом блока формирования частичных произведений, второй вход которого соединен с выходом блока вычисления обратной величины, а третий вход блока Формирования частичных произведений соединен с выходом второго регистра, второй выход. сумматopa частичных произведений сое динен с вторым входом второго регистра, о т л и ч а ю щ е е с я тем, что,. с целью упрощения устройства и увеличения быстродействия при выполнении деления, в него введены элемент И и коммутатор множителя, первый вход которого соединен с выходом блока управления, а выход — с четвертым входом блока. Формирования частичных произведений, второй вход коммутатора множителя соединен с выходом втоторого регистра, первый вход элемента И соединен с вторым выходом сумматора частичных произведений, второй вход элемента И вЂ” с выходом блока управления, выход элемента И соединен с пятым входом блока Формирования частичных проиэьедений и входом блока управления.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3591787, кл. 235-159, 1971.

2. Авторское свидетельство СССР

Р 305475, N.Кл. G G06 F 7/39, 1971.

Составители А. Уткин

Редактор Е. Гончар Техреду И. Ниймет Ко ектоц Л. Василина

Заказ 559/46 Тираж 779 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Раушская наб. д. 4 5"Филиал ППИ Патент, г. Ужгород, ул. Проектная, 4