Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬГЕтЕНИЯ ""649ОЗ7

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Лополнительное к авт. свид-ву— (22) ЗаЯвлено 210475 (21) 2126212/18-24 с присоединением заявки №вЂ” (23) ПриоритетОпубликовано 250279.Бюллетень № 7

Зата опубликования описания 2502,79 (51) М. Кл.

G 11 С 15/00

Государственный комитет

СССР но делам изобретений и открытий (5З) УЛК 6 81 . 3 27 (088.8) (72) Авторы изобретения

Е.П.Балашов, В.Ф.Нестерук и Д.В.Пузанков (71) Заявитель

Ленинградский ордена Ленина электротехнический институт им. В.И.Ульянова (Л(енина) (54 ) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее накопитель, дешифратор, регистры и формирователи (11. Недостатком этого устройства являютея его ограниченные функциональные возможности.

Иэ известных устройств наиболее близким техническим решением к изобретению является логическое запоминающее устройство, содержащее группы одноразрядных блоков памяти, адресные входы которых подключены к адресным шинам, входы записи и считывания соединены с одноименными шинами запи-( си и считывания, стробирующие входы подключены к шине общего стробирования, а информационные входы и выходы соединены соответственно с выходами входного и со входами выходного регистров (2).

Недостатком этого логического запоминающего устройства является то, что оно не может быть использовано для обмена информацией между каналами с различными форматами передаваемых данных. Например, между каналом с форматом передаваемых данных равным разрядности запоминающего устройства (формат полного слова) и канапом, формат подаваемых данных которого равен кратной части формата полного слова (байтовый формат). Подобная проблема возникает при обмене данными между ядром вычислительной системы и периферийными устройствами. Это существенно ограничивает область применения устройства.

Целью изобретения является расширение области применения устройства, что позволит использовать логическое запоминающее устройство для обмена информацией между каналами, имеющими различные форматы передаваемых данных.

Это достигается тем, что устройство содержит дополнительные блоки памяти и шины группового стробирования по числу групп одноразрядных блоков памяти, управляющую шину стробирования, шину опроса, шину признака группового стробирования, шину ввода константы и шину индикации, подключенную к информационному выходу дополнительного блока памяти последней группы, каждая иэ шин группового стробирования подключена к стробирующим входам одноразрядных блоков памяти и к стробирующему входу дополнительного блока памяти соответст649037 вующей группы, соединенному с управляющей шиной стробирования, вход записи каждого дополнительного блока памяти подключен к шинам записи и считывания, входы считывания дополнительных блоков памяти соединены с шиной опроса, шина группового стро- 5 бирования первой группы блоков памяти подключена к шине признака груп-. пового стробирования, шина группового стробирования каждой последующей группы блоков памяти соединена с ин- Я формационным выходом дополнительного блока памяти предыдущей группы, а информационные и адресные входы дополнительных блоков памяти соединены соответственно с шиной ввода кон- )5 станты и с адресными шинами.

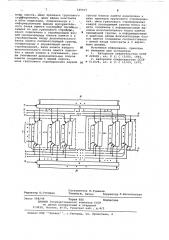

На чертеже приведена схема предложенного логического запоминающего устройства.

Устройство содержит одноразрядные щ блоки памяти 1, объединенные в группы 2, каждая из которых содержит дополнительный блок памяти 3, шину 4 группового .стробирования.

Адресные входы блоков памяти 1 и 3 подключены к адресным шинам 5. Входы записи и считывания блоков памяти 1 соединены с одноименными шинами записи 6 и считывания 7, а вход 8 записи блоков памяти 3 подключен как к шине записи 6, так и к шине считывания 7.

Входы считывания всех блоков памяти 3 соединены с шиной опроса 9.

Стробирующие входы блоков памяти

1 каждой иэ групп 2 подключены к шине

10 общего стробирования и к соответствующей шине 4 группового стробирования, а стробирующий вход каждого блока памяти 3 соединен с соответствующей шиной 4 группового стробирования и с управляющей шиной 11 40 стробирования.

Шина 4 группового стробирования первой группы 2 подключена к шине 12 признака группового стробирования, а информационный выход блока памяти 48

3 последней группы 2 соединен с шиной

13 индикации.

Информационные входы блоков памяти 1 подключены к выходам входного регистра 14, информационные входы 80 блоков памяти 3 — к шине 15 ввода константы, а информационные выходы блоков памяти 1 соединены со входами выходного регистра 16.

Устройство также содержит управляюь5 щую шину 17 и входы 18 входного регистра 14, управляющую шину 19

1 и выходные шины 20 выходного регистра 16.

Логическое запоминающее устройство имеет два режима работы: режим @» работы с полным словом и режим груп àoÀ работы.

Считаем,что до начала работы но всех ячейках блоков памяти 3 записаны68 нули. Выполнение операций записи или считывания в блоках памяти 1 и 3 происходит только в том случае, если они находятся в активном состоянии.

Переход каждого иэ блоков 1 и 3 в активное состояние возможен не толь- ко по сигналу, поступающему на стробирующий вход этих блоков. После выполнения операций записи или считывания блоки памяти 1 и 3 переходят в пассивное состояние.

Управляющие сигналы на шины 5-7, 9-12, 15,17 и 19 подаются от блока управления (на чертеже не показан).

Работа устройства в режиме с полным словом происходит следующим образом.

В первом такте на шину 10 общего стробирования поступает управляющий сигнал, переводящий в активное состОяние все блоки памяти 1.

Во втором такте управляющие сигналы подаются на адресные шины 5 и на одну из шин записи 6 или считывания 7.

Если во втором такте управляющий сигнал присутствовал на шине записи

6, то в адресном сечении блоков памяти 1, соответствующем коду адреса на адресных шинах 5, произведена запись содержимого входного регистра 14. Если же во втором такте управляющий сигнал поступал на шину считывания 7, то иэ адресного сечения блоков памяти 1, соответствующего коду адреса на адресных шинах

5, произведено считывание и занесение информации в выходной регистр 16

По окончании второго такта режим работы с полным словом заканчивается..

Работа логического запоминающего устройства в групповом режиме происходи следующим образом.

Считаем, что при выполнении операции записи, информация, поступающая на входы 18 входного регистра

14, имеет байтовый формат и заносится по сигналу в управляющей шине 17 во все группы разрядов входного регистра 14, соответствующие группам

2 блоков памяти 1, а при выполнении операции считывания, байт информации, считываемый в любой из групп 2, заносится по сигналу в управляющей шине 19 в определенную группу разрядов выходного регистра 16, предназначенную для вывода информации байтового формата.

В первом такте на управляющую шину 11 стробирования подается сигнал, переводящий все блоки памяти

3 в активное состояние.

Во втором такте при выполнении операции записи по сигналам, поступающим на шину опроса 9 и на управляющую шину 17, производится опрос адресноГо сечения блоков памяти 3, определяемого кодом адреса на адрес649037 ных шинах 5, и запись байта информации, поступившего в этом же такте на входы 18, во все группы разрядов входного регистра 14, соответствующие группам 2 блоков памяти 1.

Если в каком-нибудь блоке памяти

3 в опрошенном адресном сечении записана единица, то происходит ее считывание и сигнал с информационного выхода этого блока памяти 3 поступает на шину группового стробиронания 4 последующей группы 2 и нызынает переход в активное состояние всех блоков памяти 1 и блока памяти 3 последующей группы 2.

В третьем такте управляющие сигналы подаются на адресные шины 5, на шину ввода константы 15 и на шину записи 6, В результате в адресном сечении, определяемом кодом адреса на адресных шинах 5, той группы

2, блоки памяти 1 и 3 которой находятся в активном состоянии, будет произведена .запись содержимого соответствующей группы разрядов входного регистра 14 в блоки памяти 1 и единицы, поступающей по шине ввода константы 15, в блок памяти 3. 25

Таким образом, наличие единицы н одном из адресных сечений блока памяти 3 говорит о выполнении операции в данном адресном сечении блоков памяти 1 соотнетстнующей группы 2. 30

Повторение рассмотренной трехтактной последовательности обеспечивает поочередное выполнение операций в последовательно расположенных группах 2> а именно запись последовательно 35 поступающих байтов информации а одном и том же адресном сечении последовательно расположенных групп 2,либо считывание байтов информации из одного и того же адресного сечения последовательно расположенных групп 2.

Считывание информации выполняется с разрушением, вследствие чего в любой адресном сечении всех блоков памяти 3 не может находиться более одной единицы, что обеспечивает выполнение операции только в одной из групп 2.

Отличие работы логического запоминающего устройства при считывании информации в групповом режиме от 50 работы н гРупповом режиме при записи информации состоит в том, что во втором такте отсутствует сигнал на управляющей шине 17 входного регистра 14, а в третьем такте также сигнал на шине записи 6 отсутствует и подаются сигналы на шину считывания 7 и на управляющую шин. 19 выходного регистра 16.

Вследствие этого в блоках памяти находящихся в активном состоянии, выполняется операция считывания, а наличие сигнала на управляющей шине

19 выходного регистра 16 обеспечивает занесение считываемой информации с информационных выходов блокок 65 памяти 1 любой из групп 2 в определенную группу разрядов выходного регистра 16.

Вывод информации из выходного оегистра 16 на ныходные шины 20 i ë>,-.î> çводится в первом такте.

Появление но втором такте сиги=-ла на шине индикации 13, .подключ=.ííîé к информационному выходу блока памя-ти 3 последней группы 2, озна-=åò> что закончено н данном адресном сечении формирование полного слона иэ поступающих байтов информации при выполнении операции записи, либо закончено расформирование хранимого н данном адресном сечении запоминающего устройства полного слова на байты при выполнении операции считывания.

По сигналу ча шине индикации 13 блок управления формирует н э.-ом такте сигнал на шине 12 признака группового стробиронания„ переводя н активное состояние блоки памяти

1 и 3 первой группы 2. Одновременно изменяется и код адреса на адресных шинах 5.

В том случае, если работа !àãè >Fñкого запоминающего устройства н груп.повом режиме заканчивается после окончания формирования либо p;-.--.формирования полного слова, блок управления при последующем переходе к группсвому режиму работы дополнительно посылает но втором такте из первс и серии н три такта сигнал на нину 12 признака группоно.-с стробиронания. Работа логического за:1оминающего устройства в остальных трехтактных сериях не отличается от рассмотренной.

Описанное логическое запоминающее устройство обладает более широкой областью применения по сравнению с известными и может быть использовано, например, для органиэации обмена информацией с временной ее буферизацией между каналами связи, имеющими различные форматы передаваемых данных.

Формула изобретения

Логическое запоминающее устройство, содержащее группы одноразрядных блоков памяти, адресные входы которых подключены к адресно шинам, входы записи и считывания соединены с одноименными шинами записи и считывания, стробирующие входы подклю . ены к шине общего стробиронания, информационные входы и выходы соединены соответственно с выходами входного и со входами выходного регистров, о т л и ч а ющ е е с я тем, что, с целью расширения области применения устройства, оно содержит дополнительные блоки памяти и шины группового стробиронания по числу групп одноразрядных блоков памяти, управляющую шину стробиронания

649037 га

Составитель В.Рудаков

Техред М Петко Корректор Л.Веселовская

Редактор О.Стенина

Эаказ 568/49 Тираж 680 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5 филиал ППП Патент, г.ужгород, ул. Проектная, 4 шину опроса, шину признака группового стрр ирования, шину ввода константы и шину индикации, подключенную к информационному выходу дополнительного блока памяти последйЬй rgyndka)ji< каждая из шин группового с тробифования подключена к стробирующим Входам одноразрядных блоков памяти и к стробирующему входу дополнительного блока памяти соответствующей группы, соединенному с управляющей шиной стробирования, вход записи каждого 30 дополнительного блока памяти подключен к шинам записи и считывания, входы считывания дополнительных блоков памяти соединены с шиной опроса, шина группового стробирования первой группы блоков памяти подключена к шине признака группового стробирования, шина группового стробирования каждой последующей группы блока памяти соединена с информационным выходом дополнительного блока памяти предыдущей группы, а информационные и адресные входы дополнительных блоков памяти соединены соответственно с шиной ввода константы,и с адресными шинами.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 226681, кл. G ll С 15/00, 1965.

2. Авторское свидетельство СССР

Р 511628, кл. G 11 С 15/00, 1975.