Устройство синхронизации асинхронных цифровых последовательностей

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБ ЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и649148 (61) Дополнительное к авт. свид-ву (22) ЗаявлЕно14.02.77 (21) 2451933/18 09 (51) М. Кл, Н 04 1„7/02 с присоединением заявки №

Государственный комитет

СССР ао делам изоорвтений и открытий (23) Приоритет

Опубликовано25.02.79.Бюллетень № 7

Дата опубликования описания 28.02.79 (53) УДК 621.394.

° 662.2 (088. 8) (72) Авторы изобретения

А. Г. Андрушенко, В. И. Глушков, М. М. Бекеша, А. В. Шебелист и А. П. Шевченко (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ АСИНХРОННЫХ

ЦИФРОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к электросвязи и может использоваться в системах асинхронной передачи дискретной информации с решающей обратной связью.

Известно устройство синхронизации асинхронных цифровых последовательностей, содержащее последовательно соединенные генератор импульсов, делитель частоты и блок предварительного выделения информации, выход которого подключен к входам элемента ИЛИ и к входу первого и второго блокков вентилей, а также последовательно соединенные выделитель тактовых импульсов и блок управления делителем частоты, выходы которого подключены к другим входам делителя частоты, другой выход которого подключен к первому входу выделителя тактовых импульсов (1).

Однако вхождение в синхронизм известного устройства обеспечивается только за несколько циклов передачи.

Целью изобретения является увеличение скорости вхождения в синхронизм.

Для этого в устройство синхронизации асинхронных цифровых последовательностей, содержащее последовательно соединенные генератор импульсов, делитель частоты и блок предварительного выделения информации, выходы которого подключены к входам элемента ИЛИ и к входу первого и второго блоков вентилей, а также последовательно соединенные выделитель тактовых импульсов и блок управления делителем частоты, выходы которого подключены к другим входам делителя частоты, другой выход которого подключен к первому входу выделителя тактовых импульсов, введены реверсивный распределитель и буферный регистр сдвига, причем выход элемента ИЛИ через реверсивный распределитель подключен к другим входам первого и второго блоков вентилей и блока управления делителем частоты, а выходы первого и второго блоков вентилей через буферный регистр сдвига подключены к второму входу выделителя тактовых импульсов, другой выход которого подключен к другому входу реверсивного распределителя, а другой выход делителя частоты подключен к другому входу буферного регистра сдвига.

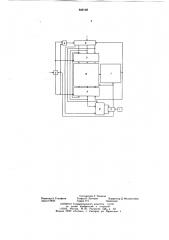

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство синхронизации асинхронных цифровых последовательностей содержит последовательно соединенные генератор 1 им649148

10 !

Ю

3 пульсов, делитель 2 частоты и блок 3 предварительного выделения информации, выходы которого подключены к входам элемента

ИЛИ 4 и к входу первого и второго блоков вентилей 5 и 6, а также последовательно соединенные выделитель 7 тактовь(х импульсов (ТИ) и блок управления 8 делителем частоты, выходы которого подключены к другим входам делителя 2, другой выход которого подключен к первому входу выделителя

7, реверсивный распределитель 9 и буферный регистр 10 сдвига, причем выход элемента

ИЛИ 4 через реверсивный распределитель 9 подключен к другим входам первого и второго блоков вентилей 5 и 6 и блока управления

8, а выходы блоков вентилей 5, 6 через буферный регистр 10 подключены к второму входу выделителя 7, выход которого подключен к другому входу реверсивного раси редел ител я 9, а другой в ы ход дел и тел я 2 подключен к другому входу буферного регистра 10.

Устройство работает следующим образом.

При включении устройства буферный регистр 10 сдвига специальным импульсом сброса устанавливается в нулевое состояние, а на втором выходе реверсивного распределителя 9 устанавливается высокий потенциал, разрешающий запись информации в буферный регистр 10. При этом на выходе буферного регистра 10 информации нет (низкие потенциалы) и на выходах выделителя 7 ТИ сигналы отсутствуют.

Информационные импульсы из линии связи поступают на блок 3, на другой вход которого поступают короткие стробирующие импульсы с первого выхода делителя 2. Частота этих импульсов кратна частоте входных информационных сигналов.

В зависимости от значения входного информационного сигнала («1» или «О») последний в виде короткого импульса, совпадающего по времени со стробирующим импульсом с первого выхода делителя 2, проходит на первый или второй выход блока 3 и записывается по соответствующему входу в буферный регистр 10. Через элемент ИЛИ

4 этот импульс поступает на первый вход реверсивного распределителя 9 и своим задним фронтом сдвигает высокий потенциал с его второго выхода на третий. На выходе буферного регистра 10 появляется высокий потенциал, поступающий на вход выделителя 7, на другой вход которого поступает очередной тактовый импульс с второго выхода делителя 2. С выхода выделителя 7 этот импульс поступает на второй вход реверсивного распределителя 9 и своим задним фронтом возвращает высокий потенциал с его третьего выхода на второй и одновременно сдвигает информацию в буферном регистре 10. Этот же импульс с выхода выделителя 7 поступает на блок управления 8.

Следующий информационный импульс, пройдя аналогичным образом через блок 3, также записывается в буферный регистр 10 и производит сдвиг высокого потенциала с второго выхода реверсивного распределителя 9 на его третий выход. Следующий за ним тактовый импульс с второго выхода делителя 2 проходит на выход выделителя 7, а своим задним фронтом производит описанные выше действия. Так продолжается до конца цикла передачи, если частота поступления информационных импульсов из линии связи в точности равна частоте следования тактовых импульсов. В конце цикла передачи на третий (установочный) вход реверсивного распределителя 9 поступает импульс установки, который устанавливает высокий потенциал на его втором выходе. Устройство готово для работы в следующем цикле передачи.

Если частота поступления информационных импульсов превышает частоту следования тактовых импульсов, то в течение цикла передачи наступает момент, когда перед очередным тактовым импульсом на вход устройства поступает не один, а два информацион25 ных импульса. В этом случае к моменту прихада очередного тактового импульса реверсивный распределитель 9 имеет высокий потенциал на своем четвертом выходе, а последний принятый информационный импульс оказывается записанным в буферный регистр

10. Высокий потенциал четвертого выхода реверсивного распределителя 9 поступает на один из входов блока управления 8. Поэтому очередной тактовый импульс через выделитель 7 и блок управления 8 поступает

З5 на один из входов делителя 2 в виде сигнала «ускорение», вызывая соответствующее изменение коэффициента счета делителя 2.

Одновременно этот очередной тактовый импульс поступает на буферный регистр 10 и на второй вход реверсивного распределителя 9, сдвигая своим задним фронтом в буферном регистре 10 последний принятый информационный импульс, а высокий потенциал реверсивного распределителя 9 — с его четвертого выхода на третий. Следующий информационный импульс из линии связи записывается в буферный регистр 10 и через элемент ИЛИ 4 сдвигает высокий потенциал с третьего выхода реверсивного распределителя 9 на его четвертый выход. По. поступлении следующего тактового импульса повторяется описанный выше процесс управления делителя 2. Этот процесс повторяется на протяжении нескольких тактов в данном цикле передачи, пока не наступает момент, когда перед поступлением из линии связи очередного информационного импульса с второго выхода делителя 2 выходит не один, а два тактовых импульса, после чего процесс корректирования прекращается, и устройство оказывается в следующем сос649148

Формула изобретения

5 тоянии: последний принятый информационный импульс хранится в буферном регистре

10, а высокий потенциал имеет место на втором выходе реверсивного распределителя

9, разрешая запись очередного информационного импульса в буферный регистр 10.

Если же частота тактовых импульсов превышает частоту поступления информационных импульсов, то в течение цикла передачи наступает момент, когда перед поступлением очередного информационного импульса на вход устройства с второго выхода делителя 2 выходит не один, а два тактовых импульса. В этом случае к моменту поступления очередного информационного импульса реверсивный распределитель 9 имеет высокий потенциал на своем первом выходе, а последний из принятых информационный импульс передается на предыдущем такте, т. е. буферный регистр 10 оказывается полностью обновленным. При этом очередной информационный импульс записывается в буферный регистр 10 и своим задним фронтом сдвигает высокий потенциал с первого выхода реверсивного распределителя 9 на его второй выход. Следующий тактовый импульс через выделитель 7 и блок управления 8 проходит на второй вход делителя 2 в виде сигнала «замедление», вызывая изменение его коэффициента счета на ту же величину, но с обратным, чем в предыдущем случае, знаком. Одновременно этот тактовый импульс через выделитель 7 считывает принятый информационный импульс, а своим задним фронтом обнуляет буферный регистр 10 и сдвигает высокий потенциал с второго выхода реверсивного распределителя 9 на первый. Следуюший информационный импульс из линии связи записывается в буферный регистр 10 и через элемент ИЛИ 4 сдвигает высокий потенциал с первого выхода реверсивного распределителя 9 на его второй выход. По поступлении следуюшего тактового импульса повторяется описанный процесс управления делителем 2. Этот процесс, как и в предыдущем случае, повторяется на протяжении нескольких тактов в данном цикле передачи, пока не наступает момент, когда перед приходом с второго выхода делителя 2 очередного тактового импульса из линии связи на вход устройства поступает не один, а два информационных импульса, после чего процесс корректирования прекращается, и устройство оказывается в следующем состояб нии: последний принятый информационный импульс хранится в буферном регистре 10, а высокий потенциал имеет место на третьем выходе реверсивного распределителя 9.

Очередной тактовый импульс с второго выхода делителя 2 сдвигает в буферном регистре 10 последний принятый информационный импульс, а высокий потенциал с третьего выхода реверсивного распределителя 9 сдвигается на его второй выход, разрешая запись очередного информационного импульса в буферр н ы и реги стр 10.

По окончании цикла передачи реверсивный распределитель 9 устанавливается в состояние, соответствующее наличию высо15 кого, потенциала на его втором выходе. Буферный регистр 10 при этом полностью обнулен. Устройство готово к работе в следующем цикле передачи.

Устройство синхронизации асинхронных цифровых последовательностей, содержащее последовательно соединенные генератор импульсов, делитель, частоты и блок предварительного выделения информации, выходы которого подключены к входам элемента ИЛИ и к входу первого и второго блоков вентилей, а также последовательно соединенные выделитель тактовых импульсов и блок управления делителем частоты, выходы которого подключены к другим входам делителя частоты, другой выход которого подключен к первому входу выделителя тактовых импульсов, отличающееся тем, что, с целью увелиз чения скорости вхождения в синхронизм, введены реверсивный распределитель и буферный регистр сдвига, причем выход элемента ИЛИ через реверсивный распределитель подключен к другим входам первого и второго блоков вентилей и блока управления

40 делителем частоты, а выходы первого и второго блоков вентилей через буферный регистр сдвига подключены к второму входу выделителя тактовых импульсов, другой выход которого подключен к другому входу

4 реверсивного распределителя, а другой выход делителя частоты подключен к другому входу буферного регистра сдвига.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

50 М 291357, кл. Н 04 1. 7)00, 1969.

649148

Редактор А. Гельфман

Заказ 578/54

Составитель Г. Теплова

Техред О. Луговая Корректор Д. Мельниченко

Тираж 774 Подписное

0НИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж-35, Раушская наб» д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4