Запоминающее устройство

Иллюстрации

Показать всеРеферат

п1165OIOI

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сааэ Сбветакнх

Социалистических

Республик д С

1 (61) Дополнительное к авт. свид-ву (22) Заявлено 29.01.73 (21) 1879977/18-24 с присоединением заявки Ке (23) Приоритет (43) Опубликовано 28.02.79. Бюллетень Vo 8 (45) Дата опубликования описания 28.02.79 (51) М. Кл. -

G 11С 11, 00

Государстеенный комитет (53) УДК 628.327.66

<О88.8} ло делам изобретений и открмтнй (72) Авторы изобретения В. Н. Сасковец, И. Я. Акушский, В. А. Шелков, Л. М. Мальцева и Л. И. Сакун

Ленинградское научно-производственное объединение

«Красная Заря» (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть испо ьзовано для хранения цифровой информации в различных устройствах электротехники.

Известны запоминающие устройства б (ЗУ), которые содержат и-разрядный регистр числа, куб памяти, содержащий две

2 "-разрядных ячеек памяти и т-разрядньай регистр адреса. Запись кода числа в куб памяти осуществляется через, регистр числа в одну из 2 " ячеек по адресу, заданному в регистре адреса, а считывание кода числа из ЗУ производится r o адресу чер ез р еги стр чи сл а (1) .

Недостатком известных ЗУ является не- 15 эффективное использование элементов памяти вследствие то го, что разрядность записываемых чисел бывает меньше и; кроме того, независимо по разным адресам могут быть записаны одинаковые числа, а также оборудование накопителя используется неэкономично при близких значениях разрядности адреса и числа.

Наиболее близкое к изобретению техническое решение — запоминающее устройст26 во, которое содержит счетчики импульсов, накопитель, вход которого соединен с выходом дешифратора, блок управления, вход которого соединен с шиной считывания, а выходы — с соответствующими входами первого счетчика импульсов, шины записи и стирания, адресные и числовые шины (2).

Недостатком известного запоминающего устройства является низкое его быстродействие, так как для записи или выборки числа из накопителя динамического типа необходимо предварительно выполнить в среднем "/2 тактов для того, чтобы подвести необходимый элемент памяти к шине записи или стирания.

Цель изобретения — повышение быстродействия запоминающего устройства.

Поставленная цель достигается тем, что устройство содержит блок анализа единичного состояния накопителя, один вход которого соединен с шиной считывания, другие входы соединены с соответствующими входами дешифратора, выход блока анализа единичного состояния накопителя подключен к входу блока управления, выход которого соединен с входом второго счетчика импульсов, второй вход блока управления соединен с шиной адреса, первый и второй управляющие входы блока управления соединены соответственно с шинами считывания и адресной. Такое устройство позволяет повысить цикл обращения к накопителю, т. е. время для записи и считывания уменьшается.

650101

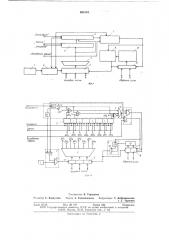

На фнг. 1 представлена блок-схема уci ройства; на фиг. 2 дан пример построения запОминающсГО усlpoi ства.

Устройство нмсст гc;!cpa òîð 1 имлульсоВ> вь!ход кото1>ого .no>I! a!o » к схсз!с 2 запуска. Выход схемы запуска сосдн..сн со счетным входом первого счетчика 3 импульсов. Выходы счетчика импульсов подкл1очены к входу дешифратора 4, который расшифровывает л1обос состояние счетчика 3 импульсов и возбуждает одну из своI1x выходных шин. Выходы дешифратоза соединены с соответствующими разрядами накопителя 5, выполненного в виде регистра и параллельно :a блок 6 анализа единичного состояния разрядов пако,1нтеля, Выход блока анализа едишгч»ol.о состояния подключен через схему 7 запуска к выходам второго счетчика 8 импульсов, а также к устройству 9 выработки сигналов считывания, которая с помощью своего выхода опрашивает состояние счетчиков 8 и 3. Счетчик 8 входами связан с адресными шинами. На выходе счетчика 8 установлена схема 10 выявления нулевого состочния, выход которой подсоединен к устройству 9 выработки сигнала считывания. Схема 2, блок 6 и схема 7 управляются шинами «Считыван1!О» и «Выработка адреса», а накопитель 5 -- шинами «Запись» и «Стирание». Генератор 1, схемы 2, 7, 10 и устройство 9 образуют вместе блок управления.

Работа устройства поясняется на примере запоминающего устройства на четыре трехразрядных числа (см. фиг. 2). Рассмотрим режим «Запись». Первоначально трехразрядный код числа napaллсльно с числовых шин поступает на вход счетчика

3 числа. На выходе дешифратора 4 прн этом возбуждается одна из восьми шин.

Так как каждая шина дешифратора заведена по порядку на соответствующий разряд накопителя 5, то при поступлен!1и сигнала «Запись» по шине 3 происходит установка в единичное состояние того разряда накопителя, на входе которого произошло совпадение сигналов возбу>кденной шины дешифратора с сигналом записи. Таким образом, при поступле:-ии других кодов на вход счетчика 3 также в накопителе 5 будут зафиксированы единичные состояния. Например, как показано на фиг. 2, в единичном состоянии находится второй разряд накопителя, которому соответствует число 2, третий разряд, которому соответствует число 3, пятый разряд, которому соответствует число 5, и седьмой разряд, которому соответствует число 7. Анaëo!.Inlно осуществляется режим «Стирание» информации в накопителе 5. При этом код числа поступает параллельно на вход счетчика 3, а сигнал «Стирание» на шине

«Стирание» устанавливает в нулевое состояние тот разряд накопителя, на входе ко >

15 0

:15

ДЗ б0 бб т01>ОГО П1>оизошло сОВГ!аде!!н(сигна!Ов От дсшиф1> а тора 4 II шины ::Сти11 апис>>.

В режиме «DI:lpaooII ;I адреса» нс1>во!1;1чально счетчики 8 и 3 дол;кпы быль уcl;Icol Оян!1С. СHI На;1011

«Выработка адреса» по шине «Выработка адреса» через элемент ИЛИ 11:a вход элемента И 12 схемы 2 запуска дается разрешенк!е ha прохождснис через элемент

И сиГналов ГенсргтОра 1 импул1 сов Ha счетный вхОд счетчи!ca 3. Пс1>вый !mini льс с генератора 1 устанавливает счетчик 3 в состояние 100 — «1». При этом возбуждается первая шина ДШ! дешифратора 4, которая управляет элементом И 13 блока 6 анализа единичного состояния. При этом элемент И 13 выделяет импульс, который поступает через элемент ИЛИ 14 блока 6 анализа и элемент И 15 chic !I:l 7 запуска на счетный вход цепи сложен!11! реверсивного счетчика 8 адреса. При совпадении трех сигналов: с первой шины дешифратора 4, с шины «Выработка адреса» через линию задержки 16 и элсме1!т 17 блока 6, с выхода первого разряда накопителя, который выделяет сигнал только находясь в единичном сос-.c:.;Inè, .:: первый разряд накопителя находится в нулевом состоянии, то сигнала на вход сче-чика 8 не поступает, и счетчик 8 остается в нулевом состоянии.

Далее на вход счетчика 3 через схему 2 поступает второй импульс. При этом счетчик 3 устанавливается в состояние 010—

«2», возбуждается шина ДШ2 дешифратора 4, которая заведена на вход элемента

И 18 блока 6 анализа. Элемент И 18 выделяет импульс, но все три его входа возбуждены из-за присутствия сигнала от второго разряда накопителя 5, находящегося в единичном состоянии, от шины «Выработка адреса» и в данный момент от шины ДШ дешифратора 4. Таким образом, счетчик 8 устанавливается в состояние 10 — «1». Так как сигнал от элемента И 15 также завсден через устройство 9, а n! Ie!IIIo линию задер>кки 19 и элемент 20, то он с задержкой, равной времени установления состояния 10 — «1» счетчика 8, опрашивает выходные цепи счетчика 8 и счетчика 3. Таким образом, на адресных шинах появляется код 10 — первый адрес, а на числовых шинах код 010 — код числа 2.

При поступлении третьего импульса генератора 1 в режиме «Выработка адреса;> на адресных шинах появляется код 01— второй адрес, а на числовых шинах 110— код числа 3, и т. д. до четвертого адреса и кода числа, равного 7. После выделения восьмого импульса с генератора 1 девятый импульс не проходит, так как режим «Выработки адреса» должен быть закончен.

В режиме «Считывание» по адресным шипам параллельно на вход счетчика 8 поступаст код адреса. Предположим, что это

650101 код адреса 11 — «3». 1хроме того, сигнал шины считывания через элементы ИЛИ и

И схемы 2 за уска разрешает импульсам генератора 1 поступать на счетный вход счетчика 3 числа. Первый импульс re»ератора устанавливает счетчик 3 в состояние

100 — «1». На выходе дешифратора возбуждается шина ДШИ однако элемент И 13 на элемент ИЛИ 14 блока 6 анализа импульса не выделяет, так как первый разряд накопителя 5 находится в нулезом состоянии.

С приходом второго импульса на счетчик 3 элемент И 18 выделяет сигнал через элемент ИЛИ 14 блока 6 анализа и элемент

И 21 схемы 7 запуска на счетный вход 3 счетчика, работающего на вычитание.

Счетчик 8 переходит из состояния 11 — «3-, в состояние 01 — «2». Элемент И 18 блока

6 анализа выделяет импульсы, так как на всех ее трех входах имеются сигналы от шины считывания через линию задержки

22 и элемент ИЛИ 17; сигнал от шины

ДШ. дешифратора 4 и сигнал от второго разряда накопителя 5, который находится в единичном состоянии.

Третий импульс с генератора 1, установив счетчик в состояние 110 †«3», возбуждает шину ДШ, дешифратора 4 и элемент

И выделяет импульс на вход «Вычитание» счетчика 8 и переводит его пз состояния

01 — «2» в состояние 10 — «1». Четвертый импульс, поступив на счетчик 3, не вырабатывает импульс на вход счетчика 8, так как четвертый разряд накопителя 5 находится в состоянии «О». Пятый импульс устанавливает счетчик 3 в состояние 101 — «5», а счетчик 8 переводит из состояния 10 — «1» в состояние 00 — «О». Схема 10 выявления нулевого состояния счетчика 8 выделяет импульс на элемент ИЛИ 20 устройства 9 для опроса состояния счетчика 3. Таким образом в числовые шины выдается код

101 — «5». Это и будет число по адресу «3».

Аналогично считываются числа по другим адресам. Так, по адресу «2» считывается код 110 — «3», по адресу «4» — число

7, а по адресу «1» — число 2. Однако каждый раз в начале режима «Считывание» необходимо предварительно установить счетчик 3 в нулевое состояние. Режим

«Считыьанис» может прекращаться (сни5

50 мается сигнал с шины «Считывание») после ка к.аого считывания кода числ а или при считывании части илп всего массива чисел.

Сигнал «Стирание» может вырабатываться также по окончании режима «Считывание». При этом в иакош1тсле соответствующий разряд переводится пз состояния

«1» в состояние «О». Если окажется, что двум или нескольким пользователям требуется записать ОднО и то же число, тогда этому числу соответствует определенный адрес. Этот адрес будет использован всеми по1ьзователями.

Испытания предлагаемого устройства показали, что время на считывание и запись информации в заноминающес устройство может быть уменьшено в среднем в 8 — 16 раз при значениях разрядности числа от

16 до 32.

Формула изобретения

Запоминающее устройство, содержащее счетчики импульсов, накопитель, вход которого соединен с выходом дешифратора, блок управления, вход которого соединен с шиной считывания, а выходы — с соответствующими входами первого счетчика импульсов, шины записи и стирания, адресныс и гнсловые шины, отл и ч а ю щееся .ем, что, с целью повышения быстродействия устройства, оно содержит блок анализа единичного состояния накопителя, один вход которого соединен с шиной считывания, другие входы соединены с соответсгвующими входами дешифратора, выход блока анализа единичного состояния накопителя подключен к входу блока управления, выход которого соединен с входом второго счетчика импульсов, второй вход блока управления соединен с шиной адреса, первый и второ управляющие входы блока управления соединены соответственно с шинами считывания и адресной.

Источники информации, принятые во внимание при экспертизе

1. Майоров С. А., Новиков Г. И. Структура ЦВМ. Л,, «Машиностроение;, 1970, с. 271.

2. Авторское свидетельство СССР № 496604, кл. G 11С 11/00, 1973.

650101 адресные шины

Чиспойх шины фиг т

«кг 7

Щгг

Составитель В. Гордонова

Редактор Е. Караулова Техред Л. Камышникова Корректоры: Т. Добровольская и 3. Тарасова

Заказ 97/15 Изд. № 197 Тираж 680 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035. Москва, %-35, Раушская наб., д. 4/5

Типографии, пр. Сапунова, 2