Усилитель на моп-транзисторах

Иллюстрации

Показать всеРеферат

(i и 65 92 I 2

ОПИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцналнстнческнх

Республик (61) Дополнительное к авт. свид-ву (22) За явлено 22.05.73 (21) 1923682/18-21 с присоединением заявки № (23) Приоритет (43) Опубликова но 28.02.79. Бюллетень ¹ 8 (45) Дата опубликования описания 28.02.79

C (51) М.

Н 03F 3!34

Государственный комитет (53) УДК 621.375.4 (088.8) по делам изобретений н открытий (72) Авторы изобретения

А. Г. Солод, В. Д. Бочко, С. И. Яровой и С. Г. Мерхалев (71) Заявитель (54) УСИЛИТЕЛЬ HA МОИ-ТРАНЗИСТОРАХ

Изобретение относится к радиоэлектронике и может быть использовано в качестве усилителя с большим коэффициентом усиления на МОП-транзисторах, выполненного по интегральной технологии с большой степенью интеграции.

Известны дифференциальные усилители на МОП-транзисторах, содержащие два входных транзистора и генератор тока в общей цепи истоков входных транзисторов (1).

Недостатком этих устройств является невозможность получения большого коэффициента усиления.

Ближайшим техническим решением к предлагаемому является дифференциальный усилитель на МОП-транзисторах, содержащий два входных транзистора, два нагрузочных транзистора и генератор тока в общей цепи истоков входных транзисторов (2).

f.

Недостатком этого устройства является невозможность получения большого коэффициента усиления при высокой степени интеграции.

Целью изобретения является увелнченис коэффициента усиления усилителя при сохранении высокой степени интеграции.

Указанная цель достигается тем, что истоки первого и второго входных транзисторов первого каскада подключены соответственно к затворам первого и второго входных транзисторов второго каскада, а истоки первого и второго входных транзисторов

5 второго каскада подключены к затворам соответственно второго и первого нагрузочных транзисторов первого каскада.

Коэффициент усиления второго дифференциального каскада выбирается из условия

К(1, что позволяет свести к минимуму площадь, занимаемую им на кристалле. Положительная обратная связь, обеспечиваемая вторым дифференцнальным каскадом, увеличивает динамическое сопротивление на15 грузки первого дифференциального каскада, что влечет за собой увеличение коэффициента усиления усилителя.

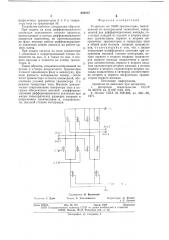

На чертеже представлена принципиальная электрическая схема устройства.

Устройство содержит первый дифференциальный каскад, состоящий пз входных транзисторов 1 и 2, на затворы которых подаются входные сигналы, нагрузочных транзисторов 3 и 4, на затворы которых подается напряжение положительной обратной связи, и генератора тока на транзисторе 5, и второй дифференциальный каскад, состоящий из входных транзисторов 6 и 7, на затворы зо которых подаются сигналы с вых. 1 и вых.2, 6502!2

Формула изобретения

;х у х.2

Составитель В. Выговский

Техред А. Камышникога

Корректоры: Л. Котова и Л. Орлова

Рсд",êòîð и. Дайч

Заказ 2721/5 Изд. № 170 Тираж 1059 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 нагрузочных транзисторов 8 и 9 и генератора тока на транзисторе 10.

Устройство работает следующим образом.

При подаче на вход дифференциального усилителя переменного сигнала процессы, 5 происходящие в плечах дифференциального усилителя идентичны, но противоположны по фазе, поэтому работу дифференциального усилителя можно показать на работе одного плеча. 10

При подаче сигнала на вход транзистора

1 усиленный и инвертированный сигнал появляется на вых. 2, а также на вых. 4 второго каскада и подается на затвор транзистора 3. 15

Таким образом, изменения напряжения на истоке и затворе нагрузочного транзистора

3 имеют одинаковую фазу и амплитуду, при этом разность потенциалов затвор — исток этого транзистора остается неизменной, обеспечивая условия работы транзистора 3 в режиме генератора тока. Высокое динамическое сопротивление генератора тока в нагрузке обеспечивает высокий коэффициент усиления дифференциального усилителя при малых геометрических размерах входных и нагрузочных транзисторов и, следовательно, высокой степени интеграции.

Усилитель на МОП-транзисторах, выполненный по интегральной технологии, содержащий два дифференциальных каскада, состоящих каждый из первого и второго входных транзисторов, первого и второго нагрузочных транзисторов и генератора тока в общей цепи истоков входных транзисторов, отличающийся тем, что, с целью повышения коэффициента усиления при сохранении высокой степени интеграции, истоки первого и второго входных транзисторов первого каскада подключены к затворам соответственно первого и второго входных транзисторов второго каскада, а истоки первого и второго транзисторов второго каскада подключены к затворам соответственно второго и первого нагрузочных транзисторов первого каскада.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 367578, кл. Н 03F 3/34, 1971.

2. Патент США № 3581226, кл. 330 †, 1971.