Устройство адаптивной коррекции сигналов в дискретных каналах связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1 i) 650234

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 27.12.76 (21) 2434030/18-09 с присоединением заявки № (51) М. Кл.2

Н 04В 3/04 (43) Опубликовано 28.02.79. Бюллетень ¹ 8 (45) Дата опубликования описания 28.02.79 (53) УДК 621.395.664 (088.8) по делам изобретеиии и открытий (72) Авторы изобретения

И. С. Павлов и Д. Л. Тихомиров (71) Заявитель (54) УСТРОЙСТВО АДАПТИВНОЙ КОРРЕКЦИИ СИГНАЛОВ

В ДИСКРЕТНЫХ КАНАЛАХ СВЯЗИ

Государствеииый комитет (3)

23 Приоритет

Изобретение относится к электросвязи, в частности к технике передачи данных, и может использоваться на коммутируемых и некоммутируемых каналах связи, характеризующихся группированием ошибок в пачки, в том числе на проводных телефонных каналах связи.

Известно устройство адаптивной коррекции сигналов в дискретных каналах связи, содержащее линию задержки с N отводами, каждый отвод которой подключен к первым входам основных перемножителей и каждого перемножителя N корреляторов, каждый из которых включает интегратор, выход каждого интегратора N корреляторов подключен к соответствующему основному перемножителю, выходы последних подключены к входам первого сумматора, выход которого подключен к одному входу второго сумматора, к другому входу которого подан эталонный инвертированный сигнал, выход второго сумматора подключен через аттенюатор к вторым входам перемножителей N корреляторов (1).

Однако известное устройство не обладает помехоустойчивостью как к помехам типа обрыва связи и понижений уровня, так и к импульсным помехам, что приводит к снижению точности.

Целью изобретения является повышение точности.

Для этого в устройство адаптивной коррекции сигналов в дискретных каналах связи, содержащее линию задержки с Х отводами, каждый отвод которой подключен к первым входам основных перемножителей и каждого перемножителя N корреляторов, каждый из которых включает интегратор, выход каждого интегратора Л корреляторов подключен к соответствующему основному перемножителю, выходы последних подключены к входам первого сумматора, выход которого подключен к одному

1,-. входу второго сумматора, к другому входу которого подан эталонный инвертированный сигнал, выход второго сумматора подключен через аттенюатор к вторым входам перемножителей N корреляторов, введены элемент задержки на длительность единичного элемента, последовательно соединенные инвертор, формирователь тактовых импульсов, статический триггер, элемент И, к другому входу которого подключен выход инвертора, регистр сдвига, на другой вход которого поданы тактовые импульсы, к другому входу статического триггера поданы сигналы оценки единичного импульса, и N ключей, прн этом каждый нз Л ключей

450234 Э

65 введен между выходом перемножителя коррелятора и входом интегратора, к управляющему входу N ключей подключены соответствующие выходы регистра сдвига, а выход элемента задержки на длительность единичного элемента подключен к входу линии задержки с У отводами.

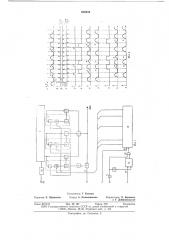

На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 — диаграммы, поясняющие его работу.

Устройство адаптивной коррекции сигналов в дискретных каналах связи содержит линию задержки 1 с Л отводами, каждый отвод которой подключен к первым входа::i основных перемножителей 2 и каждого перемножителя 3 N корреляторов 4, каждый из которых включает интегратор 5, выход каждого интегратора 5 N корреляторов 4 подключен к соответствующему основному перемножителю 2, выходы последних подключены к входам первого сумматора о, выход которого подключен к одному входу второго сумматора 7, к другому входу 8 которого подан эталонный инвертированный сигнал, выход второго сумматора 7 подключен через аттенюатор 9 к вторым входам перемножителей 3 N корреляторов 4 (фиг. 1) .

Устройство содержит также элемент задержки 10 на длительность единичного элемента, последовательно соединенные инвертор 11, формирователь 12 тактовых импульсов, статический триггер 13, элемент И 14, к другому входу которого подключен выход инвертора 11, регистр 15 сдвига, на другой вход 16 которого поданы тактовые импульсы, к другому входу 17 статического триггера 13 поданы сигналы оценки единичного импульса, и Ж ключей 18, при этом каждый из N ключей 18 включен между выходом перемножителя 3 коррелятора 4 и входом интегратора 5, к управляющему входу N ключей 18 подключены соответствующие выходы регистра 15, а выход элемента задержки 10 подключен к входу линии задержки 1. Вход элемента задержки

10 является входом устройства (фиг. 1).

Устройство работает следующим образом.

На вход устройства поступает демодулированный сигнал (фиг. 2а). Одновременно на инвертор 11 и на вход 16 регистра 15 поступают первые и вторые тактовые импульсы — такт Tl и такт Т2 (фиг. 2б, в). С инвертора 11 импульсы поступают на формирователь 12, на выходе которого формируются тактовые импульсы, приведенные на фиг. 2г.

Фиксация искажения единичного импульса помехой осуществляется внешним устройством (не показано), в котором формируется оценка каждого единичного элемента. Фиксация искажения единичного элемента производится на интервале т (фиг. 2а, б, в) т — — т —.сь где т — длительность едипи ного элемента, т — длительность тактового импульса (т << т) для каждого единичного элемента. Сигнал, определяющий ошибку в единичном элементе, поступает на вход 17 статического триггера 13, который при этом срабатывает (фиг. 2д).

На фиг. 2 в качестве примера показано наличие ошибки в единичных элементах сигнала, отмеченных

Под такт Tl после срабатывания статического триггера 13 в первый разряд регистра 15 записывается «единица», хранящаяся в указанном разряде регистра 15 в течение длительности одного единичного элемента. При отсутствии ошибки в единичном элементе на соответствующем такте в первый разряд регистра 15 не записывается «единица», и он остается на указанном такте в состоянии «нуль». Сдвиг информации в регистре 15 осуществляется под такт Т2.

Статический триггер 13 возвращается в исходное положение (фиг. 2г) по сигналу с формирователя 12, запускаемого от импульсов такта Т1.

Входной сигнал (фиг. 2а) поступает на элемент задержки 10 на длительность единичного элемента, тем самым в устройстве обеспечивается возможность получения оценки: искажен или не искажен помехой каждый единичный элемент до его поступления на линию задержки 1 с Л отводами.

Если единичные элементы, отмеченные ", искажены помехой, то они, проходя через линию задержки 1, не участвуют ь формировании весовых коэффициентов линии задержки 1 (фиг. 2е — 2л) за счет размыкания ключей 18 по сигналам с выходов регистра 15, На фиг. 2е, ж, з приведены диаграммы, поясняющие формирование весового коэффициента первого отвода линии задержки

1, а на фиг. 2и, к, л — второго отвода линии задержки 1. При этом на фиг. 2е, и приведены диаграммы управляющих сигналов на ключах 18, включенных между перемножителями 3 и интеграторами 5 корреляторов

4 соответственно первого и второго отводов линии задержки 1. При этом показано, что при единичных элементах, искаженных помехами, происходит размыкание ключей

18, принадлежащих первому и второму отводу линии задержки 1.

На фиг. 2ж, к приведены диаграммы демодулированных входных сигналов на входах соответственно первого и второго отвода линии задержки 1, а на фиг. 2з,л — диаграммы сигналов на интеграторах 5 первого и второго отвода линии задержки 1, используемых для формирования весовых коэффициентов указанных отводов.

Коэффициенты взаимной корреляции сигнала ошибки и выборки входного сигна650234 ла на каждом отводе линии задержки 1 определяют сигнал подстройки весового коэффициента соответствующего отвода. Указанный сигнал подстройки весовых коэффициентов вычисляется на каждый тактовый интервал. Значение весового коэффициента каждого отвода формируется на выходе интегратора 5 соответствующего отвода.

Предложенное устройство позволяет исключить воздействие как отдельных единичных элементов, искаженных импульсными помехами, так и пачек ошибок, вызванных указанными помехами. В результате обеспечивается устойчивая работа с заданным параметром качества на протяженных коммутируемых и некоммутируемых каналах связи.

Формула изобретения

Устройство адаптивной коррекции сигналов в дискретных каналах связи, содержащее линию задержки с N отводами, «аждый отвод которой подключен к первым входам основных перемножителей и каждого перемножителя N корреляторов, каждый из которых включает интегратор, выход каждого интегратора N корреляторов подключен к соответствующему основному перемножителю, выходы последних подключены к входам первого сумматора, вы5

Зо ход которого подключен к ОднОм) Входу второго сумматора, к другому входу которого подан эталонный инвертированный сигнал, выход второго сумматора подключен через аттенюатор к вторым входам перемножителей Nкорре.ляторов, .о т .л и ч аю щ е е с я тем, что, с целью повышения точности, в него введены элемент задержки на длительность единичного элемента, последовательно соединенные пнвертор, формирователь тактовых импульсов, статический триггер, элемент И, к другому входу которого подключен выход инвсртора, регистр сдвига, на другой вход которого поданы тактовые импульсы, к другому входу статического триггера поданы сигналы оценки единичного импульса и Л ключей, при этом каждый из М ключей введен между выходом перемножителя коррелятора и входом интегратора, к управляющему входу N ключей подключены соответствующие выходы регистра сдвига, а выход элемента задержки на длительность единичного элемента подключен к входу линии задержки с Л отводами.

Источники информации, принятые во внимание при экспертизе

1. Proalcis 1. G., М111ег 1. Н. An Adaptive

Receiver for Digital Signaling Through

Channels xvith Intersjmbol Interference.

«IEEE Transaction of Information Theory», — 15, 1969, № 4.

650234 со CV) Составитель Г. Теплова

Техред А, Камышникова

Корректоры: P. Беркович и Т. Добровольская

Редактор К. Щадилова

Типография, пр. Сапунова, 2

Заказ 2713/17 Изд. № 167 Тираж 779 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7Ê-35, Раушская наб., д. 4/5