Фазо-импульсный сумматор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалист ииеских

Республик (61) Дополнительное к авт. свил.-ву(22) Заявлено 25.02.77 (21) 2456757/18-2 с присоединением заявки № (23) Приоритет

Опубликовано 05.03;79.Бюллетень № 9

Дата опубликования описания 08. 03.7

Гасударственный квинтет

СССР на делам иэебретеннй н еткритнй (72) Авторы изобретения

В. И. Жабин, В. И. Корнейчук, А. Ф. Меженый, В. Г. Оснач, А. Г. Скорик и В. П. Тарасенко

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заяви7ель (54) ФАЗО-ИМПУЛЬСНЫЙ СУММАТОР

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах, работающих в недвоичной системе счисления при фазо-импульсном представлении информации.

Известны десятичные сумматоры с фазо-импульсным представлением информации (1), (2) .

Такие сумматоры обладают низким быстродействием и могут быть применены лишь для десятичной системы счисления.

Наиболее близким по технической сущности является фазо-импульсный сумматор, содержащий триггер и элементы И и ИЛИ, а также шины слагаемых, шину переноса из младшего разряда, шину переноса в стар1 шин разряд, шины фазо-импульсных констант, выходную шину (3).

Такой сумматор характеризуется сравнительно невысоким быстродействием.

Целью изобретения является повышение быстродействия фазо-импульсного сумматора.

Для достижения этой цели он содержит преобразователь фазо-импульсного кода в двоичный позиционный код, сдвигатель, многоразрядный двоичный накапливающий сумматор, дешифратор, причем входы преобра зователя фазо-импульсного кода в двоичный позиционный код соединены с шинами фазоимпульсных констант, а управляющий вход— с выходом первого элемента ИЛИ, входы которого соединены с шинами слагаемых и входами элемента И, выход которого подключен к единичному входу триггера, нулевой вход которого подключен к шине нулевой фазо-импульсной константы, а единичный и нулевой выходы — соответственно к входам сдвига и разрешения передачи информации без сдвига сдвигателя, входы которого соединены с выходами преобразователя фазо-импульсного кода в двоичный позиционный код, а выходы — со входами многоразрядного двоичного накапливающего сумматора, ко входу переноса младшего разряда которого подключена шина переноса из младшего разряда, а выходы подключены ко входам дешифратора, выходы которого соединены с первыми входами группы элементов И, вторые входы которых подключены к соответствующим шинам фазо-импульсных констант, а выходы — ко входам второго элемента ИЛИ, выход которого%одклю4 ном периоде фазо-импульсный сигнал второго слагаемого. В результате этого на выходах накапливающего двоичного сумматора 1 образуется результат суммы двух чисел с

5 учетом единицы переноса с младшего разряда. Если значение этой суммы превышает величину основания системы счисления, то на выходе цепи переноса двоичного сумма тора 1 появляется единичный сигнал, который через элемент ИЛИ 10 поступает на шину сигнала переноса в старший разряд. При этом число состояний двоичного накапливающего сумматора 1 выбирается равным значению основания принятой системы счисления. Состояние многоразрядного двоичного накапливающего сумматора дешифрируется дешифратором 7, сигнал с одного из выходов которого поступает на первый вход соответствующего элемента И 8. Считывание результата суммирования происхо20 дит в следующем (втором) опорном периоде посредством фазо-импульсных констант, каждая из которых соответствует своему выходу дешифратора 7 и поступает на второй вход соответствующего элемента И 8. На выходе того элемента 8, на входах которого присутствует сигнал с дешифратора 7 и соответствующая фазо- импульсная константа, . -появляется единичный сигнал, который через элемент ИЛИ 9 поступает на выходную шину фазо-импульсного сумматора. При этом фазовый сдвиг этого сигнала по отношению к опорной последовательности соответствует двоичному позиционному коду суммы, сформировавшемуся на выходах двои ного сумматора 1.

Пусть теперь числа Х и Х, поступающие по входным шинам, имеют одинаковые численные значения. Так как при фазо-импульсном принципе представления информации сигналы, отображающие одинаковые числа, совпадают во времени, то на управляющий вход преобразователя 5 поступит

40 один сигнал и на выходе этого преобразователя появится двоичный позиционный код, соответствующий только одному из фазоимпульсных сигналов.

Одновременно с этим откроется элемент

И 4 и триггер 3 установйтся в единичное состояние. В этом случае двоичный позиционный код сдвигается сдвигателем 2 на один разряд в сторону старших разрядов. Таким образом на выходе сдвигателя 2 появится двоичный позиционный код, соответствую5О щий удвоенному значению одного из суммируемых чисел, который поступит на двоичный сумматор 1, где сформируется окончательный результат суммы с учетом единицы переноса с младшего разряда. Если зна55 чение суммы двух чисел превышает величину основания системы счисления, то на выходе цепи переноса сдвигателя 2 появится единичный сигнал, который через элемент

ИЛИ 10 поступит на шину сигнала переноса

651343 чен к выходной шине фазо-импульсного сумматора, выходы переноса сдвигателя и многоразрядного двоичного накапливающего сумматора подключены ко входам третьего элемента ИЛИ, выход которого подключен к шине переноса в старший разряд.

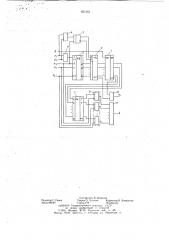

Сущность изобретения поясняется чертежом, где изображена функциональная схема фазо-импульсного сумматора.

Фазо-импульсный сумматор - содержит многоразрядный двоичный накапливающий сумматор 1, вход младшего разряда которого соединен с шиной сдвига переноса из предыдущего разряда. К информационным входам двоичного сумматора 1 подключен выходами сдвигатель 2, вход сдвига и вход разрешения передачи информации без сдви га которого соединены соответственно с единичным и нулевым выходами триггера 3.

Единичный вход триггера 3 связан с выходом элемента И 4, а нулевой вход триггера 3 — с шиной нулевой фазо-импульсной конста нты Ко . Ко входам сдвигателя 2 подсоединен выходами преобразователь фазоимпульсного кода в двоичный позиционный код 5. К управляющему входу преобразователя 5 подсоединен выходом элемент ИЛИ 6, а ко входам преобразователя 5 подвешены нины фазо-импульсных констант К! (i =

=- 0,1,...;и — 1; и — основание системы счисления). Первый вход элемента И 4 и первый вход элемента ИЛИ 6 соединены с шиной первого слагаемого, а вторые входы этих элементов — с шиной второго слагаемого.

К выходам двоичного. сумматора 1 подключен дешифратор 7, связанный выходами с первыми входами группы элементов И 8, ко вторым входам которых подведены шины соответствующих фазо-импульсных констант

Выходы элементов И 8 соединены со входами элемента ИЛИ 9, выход которого подключен к выходной шине фазо-импульсного сумматора. Кроме того, выходы переноса сдвигателя 2 и двоичного сумматора 1 связаны с входами элемента ИЛИ 10, выход которого подключен к шине сигнала переноса в старший разряд.

Фазо-импульсный сумматор работает следующим образом.

Пусть суммируемые числа Х> и Ха, поступающие по шинам слагаемых, имеют неодинаковые численные значения. В этом случае фазо-импульсный сигнал, отображающий меньшее число, поступит на управляющий

- вход преобразователя 5 первым и преобразуется в двоичный позиционный код. Так как вначале работы нулевая фазо-импульсная константа Ко установит на нулевом выходе триггера 3 единичный сигнал, то двоичный позиционный код первого Слагаемого через сдвигатель 2 поступит на многоразрядный двоичный накапливающий сумматор 1 без изменения. Аналогичным образом на двоичный сумматор 1 поступает в том же опорФормула изобретения

6513

5 в старший разряд. В дальнейшем формирование сигналов суммы на выходе фазо-импульсного сумматора аналогично описанному в предыдушем примере.

Из описания работы фазо-импульсного 5 сумматора следует, что общее время суммирования двух чисел с учетом единицы переноса с младшего разряда и считывания результата такого суммирования равно двум опорным периодам. В известном сумматоре такая же операция требует трех опорных

1О периодов. Так как период тактовых импульсов для известного сумматора должен быть не менее Зт, а для данного сумматора г (ч— минимальное время, через которое возможна передача импульсов на вход сумйатора), 1 то время суммирования двух чисел в известном сумматоре будет равно Зг Зп = 9пс, а время такого же суммирования в данном сумматоре т 2п = 2пг, где n — количество тактовых импульсов в опорном периоде. Отсюда едует, что предлагаемь!й сумматор 20 в 4,5 раза будет более быстродействующим, чем известйый сумматор.

Фазо-импульсный сумматор, содержащий триггер и элементы И и ИЛИ, а также шины слагаемых, шину переноса из младшего разряда, шину переноса в старший разряд, шины фазо-импульсных констант, выходную шину, отличающийся тем, что, с целью повышения быстродействия, сумматор содержит преобразователь фазо-импульсного ко-да в двоичный позиционный код, сдвигатель, многоразрядный двоичный накапливающий

35 сумматор, дешифратор, причем входы преобразователя фазо-импульсного кода в дво43

6 ичный позиционный код соединены с шинами фазо-импульсных констант, а управляющий вход — с выходом первого элемента ИЛИ, входы которого соединены с шинами слагаемых и входами элемента И, выход которого подключен к единичному входу триггера, нулевой вход которого подключен к шине нулевой фазо-импульсной константы, а единичный и нулевой выходы — соответственно к входам сдвига и разрешеййя передачи информации без сдвига сдвигателя, входы которого соединены с выходами преобразователя фазо-импульсного кода в двоичный позиционный код, а выходы — со входами многоразрядногб двоичного накат1ливающего сумматора, ко входу переноса младшего разряда которого подключена шина переноса из младшего рязряда, а выходы подключенй ко входам деШифратора, выходы которого соединены с первыми входами группы элементов И, вторые входы которых подключены к соответствующим шинам фазо-импульсных констант, а выходы — ко входам второго элемента ИЛИ, выход которого подключен к выходной шине фазо-импульсного сумматора, выходы переноса сдвигателя и многорязрядного двоичного накапливающего сумматора подключены ко входам третьего элемента ИЛИ, выход которого подключен к шине переноса в старший разряд.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 486319, кл. G 06 F 7/385, !973.

2. Авторское свидетельство СССР № 370606, кл. G 06 F 7/385, 1970.

3. Ситников Л. С. Многоустойчивые элементы в цифровой измерительной технике.

Киев, «Наукова думка», 1970, с. 59 — 62, рис. 58 — 59.

651343

Pi

Х1

Рг к, Составитель В. Березкин

Редактор С. Равва Техред О. Луговая Корректор Н. Ковальчук

Заказ 806 45 Тираж 779 Подписное

1ЯИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K-35, Раунскан наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4