Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

Pip(. = „ р

ОПИСАНИЕ(ИЗОБРЕТЕН ИЯ и АВТОРСКОМУ СВИДВТВ,ПЬСХВУ

Союз Советекия

Социалистимескиз

Республик (61) Дополнительное к авт. синд-ву (22) Заявлено 12.01,76 (2l) 2313791/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл, G O8 F 15/46

6 05 В 23/02

Гкудерстееиньй ещатет

СССР

N делам езебретеией и еткрытей

Опубликовано .05.03.79. Вюллетень K 9 (53) У,О,К

621.396 (088.8) Иата опубликования описания 05.03.79 (72) Авторы изобрЕтеиии С. С. Забара, A. М, Романкевич, О. Д. Руккас и М, С. Бер)атейи

Киевский научно-исследовательский институт периферийного ооорудования (7Ц Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ

Изобретение относится к области автоматического контроля н может быть использовано для контроля плат цифровых вычислительных машин, построенных на стандартных ячейках.

Известно устройство для контроля объекта, содержащее регистры парамегров объекта, столб- 3 цов таблицы ненсправпостей, номеров столбцов таблицы, неисправностей, регистр результатов выборки, схему собирания и схемы индикации (1).

Недостатком данного устройства является низкая частота смены входных ситналов проверяемого объекта, а также необходимость предварительного вычисления большого объема информации о входньи испытательных последовательностях и таблице функций неисправностей.

Наиболее близким техническим решением является устройство, содержащее коммутатор, объединенный со входами. блока усилителей-нормализаторов, блоки уставок, соединенные со входами соответствующих компараторов, в ыходы 2@ которых соединены со входами блока ввода.

-,вывода н блок управления, соединенный с генера- . ,торомтестов (2}.

Недостатком данного устройства является не возможность устранения при контроле неисправленных ситуаций типа логического риска, критических состязаний, неустойчивости состояния и т.п., что, в конечном счете, приводит к низкой достоверности контроля.

Целью изобретения является повышение. достоверности контроля. Это достигается тем, что в устройство введены временной и амплитудный дискриминаторы, элементы ИЛИ, блоки регистрации и блоки управления уставкамн, причем выход блока усилителей-нормализаторов соединен со входами временного и амплитудною дискриминаторов, блока регистрации, блоков управления уставками и через элементы ИЛИ вЂ” со

Входами блоков уставок, выходы блоков управления уставками соединены с другими входами соответствующих элементов ИЛИ, а нх входы — с выходами компараторов и блоков регистрации, второй и третин входы которых соединены с выходами временного дискриминатора и блока управления, выходы блока ввода-вывода соединены со входами генератора тестов и блок 65 1351

"" " йрайГейтттг, соединенного с выходом аьптлитуд = ттого дйСкримииатора.

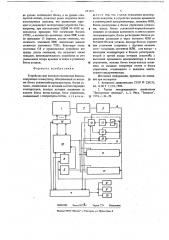

Блок-.схема устройства показана на чертеже.

Устройство содержит проверяемый логический блок 1, коммутатор 2, блок усилителей-нормалиэаторов 3, магистральную шину 4, временной дискриминатор 5, амплитудный дискриминатор 6, блок ввода-вывода 7, блок ввода 8, блок печати

9, пульт управления 10, блоки проверки стандартных ячеек 11, состоящие из блоков уставок 12, к омпараторов 13, блоков управления установками 14 и блоков регистрации 15, блока управления 16, схемы ИЛИ 17, генератор тестов

18.

Устройство работает следующим образом.

Генератор тестов (ГТ) 18 представляет собой быстродействующий генератор псевдослучайных кодов. Отдельные разряды ГТ могут быть "замаскированы". Это означает, что на соответствующие

"контакты разъема проверяемого логического блока 1 поступают постоянные во времени сигналы "0" либо "1" (инфоркйция о номерах маски " руемьтх разрядов и тине маскирующих констант поступает из блока ввода-вывода 7), Режим мас кирования применяется для уменьшения времени контроля втех случаях,,когда срабатывание некоторых цепей под воздействием только случайных сигналов происходит слишком редко. В результате действий "испытательнт,тх""тгоследовательносгей, поступающих с ГТ на входах и выхо"дах сйндаргттых ячеек, на которых построен проверяемый логический блок 1 прбйсходит случайная смена сигналов, причем, благодаря вы-! сокой частоте смены наборов в последовательности, генерируемой ГТ за достаточно короткое время, на входах каждой из стандартных ячеек (СЯ) блока 1 появятся все наборы сигналов, необходимые для проверки исправности данной

СЯ. Сигнзлы со всех внешних полюсов каждой

СЯ с помощью коммутатора 2 через блок усилителей-нормализаторрв 3 поступают в магистральную шину 4. Коммутатор 2 последовательно подключается к каждой СЯ проверяемого блока 1.

Усилители-иормализаторы 3 имеют высокое входное сопротивление с тем, чтобы не создавать дополнительной нагрузки для СЯ проверяемого блока 1. Дня каждого из типов СЯ, используемых в проверяемом блоке 1, в устройстве имеется отдельный блок проверки стандартных ячеек 11, состоятцнй из блоков уставок 12; на входьг которых из магистральной шины через схему ИЛИ 17 поступают сигналы, снятые со входов СЯ проверяемого блока 1, а также компаратора 13, сравтптвающего сигналы с выходов блока уставок 12 с выходными сигналами г.Я проверяемого блока 1, 1 поетугжющими из магистрзльной шины 4. Компараторы 13 всех блоков проверки СЯ 11 связаны с блокоьт ввода-вывода 7, однако в каждый момент сигналами с блока управления 16 заблокированы выходы всех компараторов 13, кроме того, который принадлежит к блоку проверки 11, соответствующему той СЯ, которая подключена в дана ный момент через коммутатор 2 к магистральной шине 4.

Кроме перечисленных элементов в состав блоков проверки стандартных ячеек 11, соответствующих СЯ вЂ” элементам памяти (например, тО ИМС 41ТК 551, K1TK552), входят блок регистрации и блок управления уставками. Назначение этих блоков состоит в защите предлагаемого устройства от ошибок евяззнных с выработкой

ГТ 18 сигналов, вызьтваюптих неопределенные

1З ситуации в проверяемом блоке 1. Блок регистрации фиксирует следуюптие возможные причины неопределенного состояния СЯ: а )- логически иекорректныи входной сигнал

СЯ (например, последовательность из наборов 00 и и на Я и Б входах монолитных триггеров; б) сигнал, длителъность которого меньше порогового значения, обеспечивающего надежное срабатывание СЯ.

Информация о ситуациях типа (б) (такие

> ситузцитт могут юэникать при наличии состяззний, логического риска или неустойчивости в проверяемом блоке 1) поступает иэ временного дискриминатора 5. Сигнал о наличии одной из приведенных выше причин неопределенности поступает в блок упрзвления эталонами, который

-анализирует состояние компаратора. Если имеет место несовпадение выходных ситналов проверяемой и эталонной СЯ, вырабатывается сигнал, который через схему ИЛИ 17 воздействует на

З> эталонную СЯ и переводит ее в то же состояние, в которое фактически перешла проверяемая СЯ.

Таким образом, последствия неопределенной ситуации ликвидируются. Таким же способом

"" устраттттется тгачальнзя иегтпределенность исход4О ного состояния СЯ в начале проверки: установка эталонной СЯ в исходное состояние, в котором находится проверяемая СЯ, производится по команде с блока управления 16..

Амплитудный дискриминатор 6 фиксирует

45 появление сигнала, не соответствующего уровню логического поля или единицы. Информация о номере контактз, где зарегистрирован такой сигнал, выдается оператору через блок ввода-выво1 да 7, а проверка приостанавливается.

Технико-экономическая эффективность устройства определяется повышением достоверности контроля, обусловленным, прежде всего отсутствием ошибок; связанных с неопределенными состояниями обьектов контроля.

Устройство позволяет локализовать неисправность с точностью до минимального элемента замены (например, интегральной микросхемы).

Применение принципа сравнения с установкой не

651351

ЦНИИПИ Заказ 807/36 Тираж 779 Подписное

Филиал ППП "Патент", г,ужгород, ул. Проектная, 4 на уровне логического блока, а на уровне стандартной ячейки, позволяет резко сократить число используемых эталонов, что значительно упрощает и удешевляет эксплуатацию устройства. Так, например, при изготовлении "ЭШЗМ М вЂ” 4030 используется примерно 500 логических блоков (ТЗЗ), а количество различных типов ИМС в них ие превышает 15 (причем, вполне очевидно, что стоимость эталонной ИМС значительно меньше стоимости эталонного ТЗЗ) . Благодаря этому эталонные СЯ в предлагаемом устройстве нет нужды делать сменными, что позволяет также повысить производительность устройства за счет уменьшения потерь времени за поиск и установку блока уставок.

Формула изобретения

Устройство для контроля логических блоков, содержащее коммутатор, объединенный со входами блока усилителей-нормализаторов, блоки уставок, соединенные со входами соответствующих компараторов, выходы которых соединены со входом блока ввода-вывода, блок управления, соединенный с генератором тестов, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности контроля, в устройство введены временной и амплитудный дискриминаторы, элементы ИЛИ, блоки регистрации и блоки управления уставками, выход блока усилителей-нормализаторов соединен со входами временного и амплитудного дискриминаторов, блока регистрации, блоков управления уставками и через элементы ИЛИ со входами блоков уставок, выходы блоков управлеtO ния уставками соединены с другими входами соотв .тствующих элементов ИЛИ, а их входы — с выходами компараторов и блоков регистрации, второй и третий входы которых соединены с выходами временного дискриминатора и блока управления, выходы блока ввода-вывода соединены со входами генератора тестов и блока управления, соединенного с выходом амплитудного дискриминатора.

Источники информации, принятые во внима20 ние при экспертизе

1, Авторское свидетельство СССР И 238235, кл., G 06 F 11/10, 1969.

2. Труды международного симпозиума

"Дискретные системы", т., 2. Рига, "Зиматне", 25 1974, с. 26 — 29.