Цифро-аналоговый многофункциональный преобразователь

Иллюстрации

Показать всеРеферат

() ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДИТИЛЬСТВУ

Союз Советснкн

Соцкапксткчеснкн

Респубпкн >651370 (6!) Дополнительное к авт. свид-ву

2 (5l) М. Кл.

Я 06 3 1/00

Cj 06 9 7/26 (22} Заявлено 14,03.77 (21) 2462039/18-24 с присоединением заявки №

Гасударственный комитет ссср

50 делам изобретений н открытий (23) Приоритет

Опубликовано05.03.79.БюллетЕйь № 9

Дата опубликования описания 10.03.79 (53) УДК 681.34 (088.8) (?2) Автор изобретения

Г. А. Калинин

Харьковский институт радиоэлектроники (71) Заявитель (54) ЦИФРОАНАЛОГОВЫЙ, МНОГОФУНКЦИОНАЛЬНЫЙ

ЛРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области автоматики и вычислительной техники, в част ности, к устройствам цифроаналогового функционального преобразования.

Известен цифроаналоговый функциональный преобразователь, содержащий входной регистр, дешифратор, цифроаналоговые преобразователи, масштабный и суммирую- щий операционные усилители 1).

Недостатком устройства является его низкая производительность при работе с различными видами функций,: определяемая отсутствием автоматической перенастройки связей между дешифратором и:цифроаналоговыми преобразователями при смене ви да функций.

Известен также многофункциональный преобразователь для совместной работы цифровых и аналоговых вычислительных маШин, содержащий входной регистр адреса, блок памяти функций, цифроанало

20 говый преобразователь, группу схем сравнения, шифратор, коммутатор, блок реверсивных счетчиков, блок вывода, блок па

2 мяти адресов, две группы элементов И, регистр saga функций и регистр адреса врлинейностей. Достоинством преобразователя является высокая производительность, обеспечиваемая за счет автоматы» ческой коммутации видов и адресов реализуемых функций. Недостатком преобразователя является сложность конструктив иой реализации при вйсоких требованиях по точности функционального;преобразоваms(a).

Каиболее близким цо технической ерш ности к предложенному является цифроаналоговый многофункциональный преобра эователь, содержащий первйй регистр, выходы старших разрядов которого соединены со входами логиЧеского блока, а выходы младших разрядов попключены к цифровым входам первого цифроаналого- вого линейного преобразователя подключенного входом управления знаком к вы- ходу триггера знака" и соединенного выходом с входом масштабного операционного усилителя, выход которого подключен к

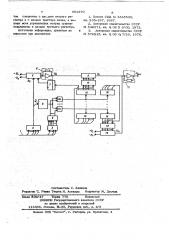

3 -, . 651370 4 аналоговому входу второго цифроаналого- ° преобразователя 5, выходы регистра 3 вого линейного преобразователя, соединен- соединены с входами дешнфратора кода ного цифровыми входами с выходами вто-, функции 6. Выходы преобразователя 5, рого регистра и подключенного выходом подключенного входом управления знаком к входу суммирующего операционного уси- g к выходу триггера знака 7, через маслителя, соединенного выходом с выходной штабный операционный усилитель 8 соешиной многофункционального преобразова- "динен с ан логовым входом второго дифтеля и вйходу третьего цифроаналогово- роаналогавого" линейного преобразоватего линейного преобразователя, соединен- JlB 9, подключенного цифровыми входами ного цифровыми вход ми o,вьщодами tO к выходам второго регистра 10. Выход третьего регистра, причем входы перво- преобразователя 9 соединен с входом

"го регистра подключены K входной шине сУммиРУющеГО опеРациОнного Усилители мног эфункциональножпр образоиателя (3}. 11 и с выходом третьего цифРоаналого».

Недмтат ом прототипа авле :я ни - вя о линейного преобразователя 12, дифк nponeaù@, ùbnoo, при работе с рае Â ровь е входы которого подключены к выли ными видами функций, что опрепепп ходам третьего регистра 13. Первые вхоеся необходймстью учной з,,мен,„>o lgr элементов Й Ряда групп 14 соединены

i Г„ческого и интерфейсно- о Моков при пе- с выходам « лоха 4, a ax вторые входы реходе с одной функциональной заву си ..подключены K соответствующим выходам мжти на другую. Кроме етого, интер- ® цешифратора 6. Выходы элементов И кажфейснь,й бло не iimei ся изделием микро- дой группы 14 соединены с входами соэлектроники и поэтому имеет значитель- ответствующей управляющей матрицы угные габарйтиб-весовые показатели.. левых коэффициентов 15 и с входами со

Hem â изобретения является повьппе- . ответствующей управляющей матрицы орииз пройзведительностя. + динат 16. Выходы матриц 18 подключеЙМтавленная цель достигается тем, . иы к входам Регистра ÕÎ и входу тригчто в цифроаналоговый миогофуикдиь- гера 7 а выходы матРиц 16 «к входам иальйый преобразователь дойопнительно регистра 13.

IIieaewi упРавйающйе" матриц yj поясах кэаффйциентов, управлякицяе матрицы ор- зе Работает многофункциональный преобйий т, регистр кода функции дешифратор . Разователь следующим образом. По входкода функции и Ряд групп цементов И, . ной шине 1 поступает информационное причем пщюые Входы элементов я каждой словoü с< стоящее"из кода аргумента и, pynnbi, сМдинейиых выходами с входами котоРый записывается в регистр 2, и ко соотвЬФствующей управляющей матрицы да функции Р, котоРый записывается в

3$ 03

Угловых коэФФициентов и с входами соот- регистр 3. ветствуюшей управляющей матрицы ордн- До ический блок 4 по значениям етариат,— подкачены к выходам логического ших разрядов М1 кода И определяет блока, в вторые входы соедййены с соот- .номер текуМцего нодйнтервала задания ар-.

4а ветствующим выходом дешифратора кода гумента при кусочно-линейной аппроксифующйи, подключеян6го входамй через мацни, Количество подйитервалов равно

pe истр кода функции к входной шине айса два в степени, соответствующей миогофункциойальиого преобразователя, числу старших разрядов двоичного кода щ ичем выходы всех управляющих матриц К1. Выходй блока 4 соединены с первыугловых коэффициентов соединены с вхо--,, ми входами элементов И ряда групп 14. дами второго Регистра и входом тригге- Число групп 14 равно числу воспроизвора знак, а выходы всех упривлякяпих димых фуйкций, а число элементов И в матриц ординат подключены к входам::каждой группе равно числу выходов блока третьего регистра. 4.

50 1

На чертеже изображена блок-схема Дешифратор 6 по значению кода P устройства,:.: осуществляет подачу отпирающего сигнаУстройство содержит входную шину 1, ла на соответствующую Fpynny элементов соединенную с входом первого pef Hñòðà И 14, Выходные сигналы с блока 4 через

2 и регистра;кода функции 3 . Выходы группу. элементов И 14 поступают на старших разрядов регистра 2 подключены входы соответствующих матриц.15 и 16, K:âxîöàM логического блока 4, а выходы в которых "хранятся коды подынтервальных младших разрядов к цифровым входам значений угловых коэффициентов и орди.первого цифроаналогового линейного .:лат j -ой функции.

651370 6

Каждой функции соответствует одна другому миожеству функций путем изме из матриц 15 и одна из матриц 16. МаТ» пения информации, записанной в управлнюрицы 15, 16, представляющие собой пос щих матрицйс ординат и угловых коеффнтоянные запоминающие устройства, соС циентов. тоят иэ двух взаимно перйендикулярных 5 групп шин-строк и столбцов. Количество Другим йреимуществом устройств явстрок равно числу адресуемых управляю- ляегся его технологичность; так как пеших слов,. т, е. числу выходов блока 4, реход от одного множества функций к

Количество столбцов соответствует раз- другому не требует проектирования новорядности управляющих слов. Подключение 16 ro логического блока и интерфейса, а диода или транзистора от строки к столб- заклю.жется в смене управляющих матриц. цу означает запись 1" в соответствую-. .щий разряд числа по соответствующему адресу.

Ф ормула изобр етения . цифроаналоговьЩ линейный преобра-. зователь 5, выполненный в виде "матрицы МиФРоанало1 свыше многофункциональный резисторов с ключами, управляется ко - преобразователь, содержащий первый редом Й составленным из младших раэря- гистр, выходы старших разрядов которого

2 дов входного кода в регистре 2, и на соединены со вход Ыи логического блока, выходе операционного усилителя 8 форчун" а выходы младших разрядов подключены руется напряжение - . к цифровым входам перво1 о цифроанало1ового линейного преобразователя, под Ц-: +U Q —. y 1ццоченного входом управления знаком к .д - о

Я"... выходу триггера знака и соединенного выходом с Йходом масштабного:операционгде З, - опорное напряжение преобразова ход ного усилителе, виход которого подклютели 51

:: ° . - чен к аналоговому в)сну второго цифрономинала резистора в цепи обратной свя джи второго рюистра и подключенного и еоб а ователя 5,, ° выходом к Входу суммиЯчОщегР oHepa уп вление знаком иап яжени U - цио@-" у -тели соедииенног выходом осуществляется в преобразователе 5 с помощью триггера 7, у :тановка которого пРеобРаэователЯ " выходУ wPersего цифР в нужное состояние на каждом участке ное состояние на каждом участке аналогового линейного преобразователя, роксим и ocymeceanaema yrrjainse СОеюиеннм 0 Фрощумй ж66ами с вьх6щей матрицей 15 . дами треть 6 0 регистра» причем входъ| цыходное иапряженйе суммирующего;, "Е"ВОГО Р Г 1СтРа. HOQ3039)Ie!9 K ВХОД"Ой операционного усилителя 1 j равно +" Hе мног4 "кцио иа @ -oro п "- "бРазова

-.-. : теля,, о т ii и ч а ю шийся тем, что, «+ U >6+ 1О.,,: :o целью повышения производительности, р 0 g jq 2 в него дополнительно введейы 1управляющие матрицы угловых коеффкциентов, упгде М tg и My - коды в регистрах 13 и равлякнцие,матрицы ординат, регистр кода

lO соответственно;

45 функции, дешифратор кода функций и ряд

1 - количество двоична:,групп злементоь И, причем- йервые входы раэрядОВ В рЕГИСтрЕ 13 (бЕЗ уЧЕта Эиа- аЛЕМЕИтОВ 11 К ждОй груППЫ, СоЕдйНЕННЬ1Х кового разряда);, выходамн с входом соответствующей уп=

- количество двоичных: равляющей матриц уГловь|с Коеффициевраэрядов в регистре 10. тов и с входами соответствуяйцей управ50: ляющей матрицы ординат, по11кжженм к

Настоящее устройство позволяет пе- выходам логического блока, а вторйе реходить от реализации одной функции входы соединены с соответствующим вык другой функции из заданного множеств- .ходом дешифратора кода функции, подклю 55 ва функций практически мгновенно, т. е. чепного входами через регистр кода функсо скоростью смены управляющих кодов. ции к входной шине многофункциональноУстройство является универсальным, го преобразователя, причем выходы всех: так как позволяет переходить к любому управляющих матриц угловых коеффициен651370 8

1. Патент США J4 3345505, кл. 235-197, 1967.

2. Авторское свидетельство СССР

М 548871, кл. Я 06 3 3/00, 1973.

3..Авторское свидетельство СССР

И 572815, кл. Cj 06 С 7/26, 1976. тов соецинены с вхо. ами второго регистра и с вхоцом триггера знака, а выХоды всех управляющих матриц ординат поцключены и входам третьего регистра, Источники информации, принятые во внимание при экспертизе Г

Заказ 809/47 Тираж 779 . Подписное

ЙНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Составитель С. Казинов

Редактор С. Равва Твхред И, Асталош Корректор М. Демчик