Двухотсчетный преобразователь углового перемещения в цифровой код

Иллюстрации

Показать всеРеферат

<с см, a е а

О П И С А Н И- < 651389

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДВТЮЛЬСТВУ (6!) Дополнительное к авт. свнд-ву Ж 526932 (5l) М. Кл. (22) Заявлено 18.03,77 (21) 2462744/18-24

Е 08 С 9/04 с присоединением заявки ¹ (23) Приоритет

Гввтдврвтвйеьй ииапвт

СССР вв делам «заврвтввве я вткрмтвй

Опублнковайо 05.03.79Pтоллетенb № 9 (5З} УЙК681,325, (088.8) Дата опубликования описания 08.03,79 (72) Авторы изобретения

А. С. Буданов, А. А, Гаврилов, Е. Ф. Тупиков и В. П. Максимов (71) Заявитель (54) ДВУХОТСЧЕТНЫЙ, АНАЛОГОЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ УГЛА

Изобретение относится к системе контроля и преобразования неэлектрических величин в электрический сигнал, а именно к двухотсчетным преобраеовате« лям угловых перемещений в цифровой код.

Известны двухотсчетные преобразователи угловых перемещений в код, содержащие синусно-косинусный вращающийся трансформатор, функциональные делители напряжения, сумматоры и реверсивный счетчик tl).

Недостаток таких преобразователей состоит в изменении погрешности работы при изменении угла в широких пре- делах.

По основному авт. св. Y 526932 известен двухотсчетный преобразователь углового перемещения в цифровой код, содержащий двухотсчетный синусно-косинусный вращающийся трансформатор (CKBT), фазовый детектор, преобразователь напряжейие-частота, блок управления реверсивным счетчиком, реверснв2, ный счетчик с младшими и старшими разрядами и блок ввода кода, делители и частоты, кварцевый генератор, дешиф:

J раторы и блок формирования синусоидальных сигналов, преобразователь код-на В пряжение, сумматор, формироватеюпограничитель, синхронизатор, блок считывания кода грубого отсчета, блок памяти и блок согласования отсчетов j2).

Недостаток этого устройства состоит в сравнительно невысокой точности работы преобразователя. . Белью изобретения является повышение точности преобразователя.

- Поставленная цель достигается за счет того, что ъ двухотсчетный преобразователь углового перемещения в цифровой.код введены два дополнительнык сумматора, избирательный усилитель, синхронный детектор, интегратор и

\ управляемый делитель напряжения один вход первого дополнительного сумматора соединен с третьим выходом блока формирования сннусоидальных сигналов и с первым входом синусно-косинусного вращающегося трансформатора, четвертый выход блока формирования синусоидальных сигналов соединен с первым входом управляемого делителя напржкения и с другим, входом первого допол кительного сумматора, выход которого соединен с одним входом второго дополнительного сумматора, к другому входу которого подключен пятый выход блока формирования синусоидальных сигналов, выход второго дополнительного сумма= тора через избирательный усилитель подключен к одному входу синхронного детектора, второй вход которого подключен к другому выходу второго дешифра тора, выход синхронного детектора через интегратор подключен к вторбму входу управляемого делителя напряжения, выход которого подключен ко второ му входу синусно-косинусного вращающегося трансформатора.

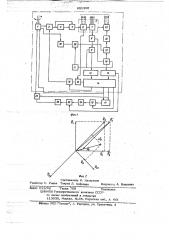

На фиг. 1 приведен блок-схема двухотсчетного преобразователя углового перемещения в цифровой код; на фиг. 2 приведена диаграмма, пояснкющая работу устройства.

Преобразователь содержит двухот счетный синусно-косинусный вращшощийся трансформатор (СКВТ) 1, фазовый детектор 2, преобразователь напряжение »частота 3, блок управления 4, реверсивный счетчик 5, содержащий сооч ветственно младшие 6 и старшие 7 разряды, блок ввода кода 8, делители частоты 9 и 10, кварцевый генератор 11, дешифраторы 12 и 13, блок формирования синусоидальный сигналов 14, преобразователь код-напряжение 15, сумматор 16„17, 18, формирователь -ограничитель 19, синхронизатор 20, блок считывания кода грубого отсчета 21, блок памяти

22, блок согласования отсчетов 23, избирательный усилитель 24, синх- ронный детектор 25, интегратор 26, управляемый делитель напряжения 27.

В устройстве выходы блока 14 формировании синусоидальных сигналов связаны с входами двухотсчетного оинусно-косинусного вращающегося трансформатора 1. Третий выход блока

14 формирования синусоидальных сигналов соединен с одним из входов двухотсчетного синусио-косинусного вращающегося трансформатора 1 и с одним из входов первого дополнительного сумматора 17. Четвертый выход блока 14 формирования синусоидальных сигналов соединен через управляемый делитель напряжения 27 с другим входом двухоъсчетного синусно-косинусного вращаю щегося трансформатора 1 и с другим входом сумматора 17. Выхрд сумматора

17 соединен с одним иэ входов второго дополнительного сумматора 18, к другому входу подключен пятый выход блока

14 формирования синусоидальных сш надов . Выход сумматора 18 через прследовательно соединенные избирательный усилитель 24, сьпгхронпый детектор

25, второй вход которого подключен к другому выходу второго дешифратора.

13,.интегратор 26 подключен к другому входу управляемого делителя напря-. жения 27.

Устройство работает следующим образом.

В исходном состоянии реверсивный счетчик 5 и делители 9 и 10 нахо дятся в исходном состоянии. Сигнал с точного отсчета CKBT-1 поступает на фазовый детектор 2, на второй вход которого поступает компенсирующее напряжение, в формировании, которого участвуют блоки 5, 8, 9, 10, 12, 14, 15, 16, образующие эталонный фазовращатель. Напряжение рассогласования, пропорциональное фазе между сигнальным напрякением, снимаемым с точного отсчета СКВТ 1 и компенсирующимс эталонного фаэоврашателя, поступает на преобразователь напряжение-частота

3 и блок управления 4 реверсивным счетчиком 5, которые в зависимости от знака и амплитуды напряжения рассогласования управляют режимом работы реверсивного счетчика (суммирование или вычитание, частота заполне п я).

Код старших разрядов реверсивного счетчика 5 через блок ввода кода записывается в делитель 9. Запись кода . осуществляется один раэ эа период заполнения делителя 10. В результате периодического ввода кода в делитель

9 кодовые комбинации в параллельно работающих делителях частоты оказываются смещенными. Лешифраторы 12 и 13 и блок формирования синусоидальных сигналов преобразуют это смешение в фазовый сдвиг формируемых сигналов.

Заполнение реверсивного счетчика 5 от преобразователя напряжение частота 3 осуществляется до тех пор, пока фаза компенсирующего напряжения, сйимаемого с сумматора 16, не будет равна фазе сигнального напряжения, снимаемого с точного отсчета CKBT.

В устройстве равенство квадратур-ных напряжений для питания СКИТ 1 осуществляется автоматически, Выполнено зто следующим образом (фиг. 2).

Пусть питающее напряжете U непосред1 ственно подключено, к входной обмотке

CKBT 1 а квадратурное Ог " через

ymimm IA II b emg 27. 16

При таком подключении питающих иапряжений будет подстраиваться ампли туда квадратурного на ряжения ц ,г

При увеличении Ог, на выходе первого, дополнительного сумматора 1 7 получим вектор, а при равных напряжениях был вектор ц . Ha втором дополнител1 ном сумматоре 18 из вектора суммы

Вычитается вспомОгательнбе напряжение Q, сдвинутое на угол 225 относительно tj . Величина напряжения

Q выбирается близкой к 5 . ОтклоHBHH$t HG 5-1 0% Не влияют HB точность подстройки. Из полученного на выходе сумматора 18 сигнала избирательным

25 усилителем 24 выделяют и усиливают сигнал первой гармоники 6о, Синх. ронным детектором 28 выделяется соотавляющая О,„, нропорпиональная

36 только амплитудному разбалансу. Опор ное напряжение оп на синхронный детек тор формируется обьединением соответсч вующих временных участков с дешифратора 13. На управляемый делитель на35 пряжения 27 сигнал с синхронного детектора 25 подается через интегратор 26.

Начальная установка амплитуд питания и Ц осуществляется выбором козффнпиента деления блока 27, при минимальном уровне выходного сигнала с синхронного детектора 25.

Работа устройства основана па неизменности и высокой стабильности фазовых сдвигов, формируемых синусоидальных сигналов. Введение автоподстройки амплитуд питания СКИТ в преобразователе угол-код позволило исклктить соответствующую погрешность от неравен -. ства амплитуд питания, что упростило И настройку и аксплуатапию, Величина суммарной погрешности от введения автоподстройки амплитуд питания умень шилась В два раза и составила 5-7 угловых секунд.

Формула изобретения

Двухотсчетиый, преобразователь углового перемещения в пифровой код по авт. Св. ¹ 526932, о т л и ч а юHI и и с я тем, что, с пелью повыше ния точности, в него введены два допоа» нительных сумматора, избирательный усилитель, синхронный детектор, ННТе,гратор и управляемый делитель. напряжения, один вход первого дополнительного сумматора соединен с третьим выходом блока формирования синусоидальных сигналов и с первым Входом синуснь-косинусного Вращающегося трансформатора, четвертый Выход блока формирования синусоидвльных сигналов соединен с первым входом управляемого делителя напряжения и с другим входом первого дополнительйого сумматора, ВЫХОД КОТОРОГО СОЕДИНЕН С ОДНИМ ВХОдом второго дополнительного сумматора к другому входу которого подклпочен пятый выход блока формирования синусидальных сигналОВ ВыхОд вторОгО дО полнительного сумматора через йзбирательный усилитель подключен к Одному входу синхронного детектора, а Второй вход которого подютючен к другому выходу второго дещифратора, выход синхронного детектора через интегратор подключен к второму входу управляе мого делит ащ напрюкения, выхьд кото.. рого подключен ко второму входу синус нокосипусного Вращающегося трансфсц матора.

Источники пнформащщ, преняъъме Во внимание при експертизе

1. Зверев A. E. и др. Преобразователи угловых перемещений в пифровой код. 1974, с. 143.

2. Авторское свидетельство СССР

¹ 526932, кл. 6- Оа С 9/О4, 1975.

651 389

Див.7

Составитель И. Назаркина

Редактор С. Равва Техред Л. Алферова Корректо .. А. Власенко

Заказ 811/48 Тираж 709 Подписное

QHHHfIH Тосударственного комитета СССР по делам изобретении и .открытий

113035, Москва, Ж-35, Рвущсквя нвб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4