Дискриминатор нулевых биений

Иллюстрации

Показать всеРеферат

ОПИСА

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<>651447

Ф» /Г. К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 1804.77 (21) 2476838/18-09 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано 0503.79.Бюллетень № 9 (51) М. Кл.

Н 03 0 13/00

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621, 376. .332 (088. 8) Дата опубликования описания 050379 (72) Авторы изобретения

А.Н.Виницкий и В.A ° Острожинский (71) Заявитель

-(54) ДИСКРИМИНАТОР НУЛЕВЫХ БИЕНИЙ

Изобретение относится к радиотехнике и может использоваться в системах измерения несущей частоты сигналов радиоимпульсов путем сравнения частоты измеряемого сигнала с частотой калиброванного опорного генератора и последующей подстройки частоты опорного генератора по сигналам дискриминатора.

Известен дискриминатор нулевых биений, содержащий два квадратурных канала, в каждом из которых включены последовательно фазовый детектор, фильтр нижних частот, ключ, на другой вход которого поданы тактовые им- 15 пульсы, блок памяти,дифференцирующая цепь и коммутатор, другой вход которого через фазоинвертор подключен к выходу дифференцирующей цепи, а управляющий вход — к выходу блока опре- ® деления знака сигнала (1).

Однако это устройство характери-. зуется недостаточным быстродействием.

Целью изобретения является повышение быстродействия.

Для этого в дискриминаторе нулевых биений, содержащем два квадратурных канала, в каждом из которых включены последовательно фазовый детектор, фильтр нижних частот, ключ, на другой вход которого поданы тактовые импульсы, блок памяти, дифференцирующая цепь и коммутатор, другой вход которого через фазоинвертор подключен к выходу дифференцирующей цепи, а управляющий вход — к выходу блока определения знака сигнала, в каждом из квадратурных каналов дифференцирующая цепь выполнена в виде последовательно соединенных линии задержки и вычитателя, второй вход которого соединен с входом линии задержки, вход блока определения знака сигнала соединен с выходом вычитателя, в каждый из квадратурных каналов включены блок определения знака сум-

nm входы которого подключены к входу и выходу линии задержки,и элемент равнозначность,первый вход которого соединен с выходом блока определения знака сигнала,а к второму входу подключен выход блока определения знака суммы другого квадратурного канала, к выходам коммутаторов подключены параллельно соединенные по входам, общие для обоих квадратурных каналов элемент сравнения и дополнительный коммутатор, к выходам элементов равнозначность подключены один непосредственно, а другой

651447 через дополнительный фазоинвертор соответствующие входы второго дополнительного коммутатора, при этом управляющие входы дополнительных коммутаторов подсоединены к выходу элемента сравнения, а выходы являются вЫходами дискриминатора нулевых бие- 5 ний.

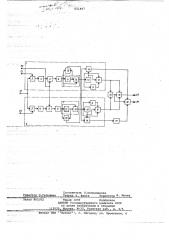

На чертеже приведена структурная элек"грическая схема предложенного устройства.

Дискриминатор нулевых биений со- Н) держит два квадратурных канала 1,2, " в каждом из которых включены последовательно фазовый детектор 3, фильтр нижних частот 4, ключ 5, на другой вход которого поданы тактовые импуль- 1я сы, блок памяти б, дифференцирующая цепь 7 и коммутатор 8, другой вход которого через фазоинвертор 9 подключен к выходу дифференцирующей цепи 7, а управляющий вход — к выходу блока определения знака сигнала

10, в каждом из квадратурных каналов 1 и 2 дифференцирующая цепь 7 выполнена в виде последовательно соединенных линии задержки 11 и вычитателя 12, второй вход которого соединен с входом линии задержки 11, вход блока определения знака сигнала

10 соединен с выходом вычитателя 12, в каждый из квадратурных каналов 1 и 2 включены блок определения знака 30 суммы 13, входы которого подключены к входу и выходу линии задержки 11, и элемент равнозначность 14, первый вход которого соединен с выходом блока определения знака сигнала 10, а к второму входу подключен выход блока определения знака суммы 13 другого -квадратурного канала, к выходам коммутаторов 8 подключены параллельно соединенные по входам, общие для 4О обоих квадратурных каналов 1 и 2 элемент сравнения 15 и дополнительный коммутатор 16, к выходам элементов равнозначность 14 подключены один непосредственно, а другой через дополнительный фазоинвертор 17 соот45 ветствующие входы второго дополнительного коммутатора 18, при этом управляющие входы дополнительных коммутаторов 16,18 подсоединены к выходу элемента сравнения 15, а выходы О являются выходами дискриминатора нулевых биений, входы 19,20,21,22, выходы 23,24.

Устройство работает следующим образом. 55

При подаче на входы фазовых детекторов 3 когерентно-импульсного сигнала и< с несущей частотой fz и опорных колебаний с частотой fon, сдвинутых друг относительно друга на 90, ® о на выходе блоков памяти б образуются последовательности прямоугольных импульсов с длительностью и периодом следования, равными длительности и периоду .следования селектирующих им- Я

:пульсов. Эти последовательности промодулированы колебаниями с частотой

Fo ° определяемой как Fo=fc font сдвинутыми друг относительно друга на 90 . Линии задержки 11 задерживают эти последовательности на период следования селектирующих импульсов. Блоки определения знака суммы 13 определяют знаки сумм сигналов, взятых с входа и выхода линий задержки 11. Вычитатели 12 определяют разность этих же сигналов, а блоки определения знака сигнала

10 определяют знаки разностей. Элементы равнозначность 14 вЬ1рабатывают логическую единицу, если на их входы поступают. одинаковые логические сигналы (пара логических нулей или пара логических единиц). Логические сигналы на их выходе зависят только от знака частоты F, причем при изменении знака РЕ эти сигналы изменяются на обратные.

При этом сигнал на выходе блока памяти б имеет вид Л)=ц s1n(g nT+q )

Сигнал на выходе блока памяти 6 имеет вид

u„otn3=0 Ìn (Q nT+q )..

Разность сигналов U9-(n ) и того же сигнала, задержанного на период, имеет вид ц Гп1=2 0 соз(52 nT- — +g )g1n

RdT . а Т

9 м d 2 О 2

Сумма сигналов о«Lnl и того же сигнала, задержанного на период, имеет вид

Qu tnl =20 соз(Я nT- — +Ч> )со и Т 5 Т

1О М 2 умножим 9Г 1ма Еи„сп l и получим

uzCnj =20„„соз (Я. nÒ- — + Р )з1н Я. Т.

Я Т

Аналогично можно йолучить

uzIEn1=hu1oCn1 Ru Cnl=-20мыд (9 пТ

ЯбТ

)51n 5t T о где au«(n) — Разность сигналов

u«tnl и u„ t n-1 l )

Е 09 Гn 1 — сумма сиГналов

u9 tn) и и t n-11

Знак величин о (и) и о и (n) зависит только от знака сомйожителя

ЫП9 Т(т.е. от знака 9. ), т.к. другие сомножители всегда положительные. Однако при некоторых значениях

Ч и п сигналы u> (n) или uzz (n) Равны нулю, а знак, следовательно, достоверно определить нельзя.

Но если выбирать из сигналов Од (п)и uzi(.n) сигнал с наибольшей амплитудной и по нему определять знак Q. -, то результат определения знака не 6удет зависеть от Чо и и т ° к. сигналы zzr(n) и uzz (n) равны нулю в разное время. В предложенном

651447

5 устройстве с целью его упрощения ве личины Uz (n) и 0 (n) не вычисляются, а определяется лишь знак этих величин по знакам сомножителей.

Для этого служат элементы равнозначность 14. Коммутаторы 8 управ- б ляются сигналами с выходов блока определения знака сигнала 10, и коммутируют сигналы, взятые с входа и выхода фазоинвертора 9, таким образом, что на выходе коммутаторов 8 р образуются сигналы всегда положительной полярности.

Элемент сравнения 15 сравнивает значения сигналов на выходах коммутаторов 8 и управляет дополнительными коммутаторами 16,18. В результате этого второй дополнительный коммутатор 18 подключает выход 24 к элементу равнозначность 14 того квадратурного канала, где сигнал наибольший. Дополнительный фазоинвертор 17 включен из-за того, что знак

Й на выходе элемента равнозначность 14 квадратурного канала 2 (сигнал О (п))получается обратным.

Дополнительный коммутатор 16 коммутирует сигналы, имеющиеся на выходах коммутаторов 8, таким образом, что на выход 23 поступает наибольший из них.

Таким образом, на выходе 24 присутствует сигнал (логические О или 1 ), зависящий от знака Я а на выходе 23 — сигнал, зависящий З5 от величины !З(п Й, -Т/, причем полярность этих сигналов не зависит от начальной фазы сигнала на входе

19 и от текущего времени и достаточно всего лишь двух импульсов на 40 входе устройства для определения знака частоты биений Fg

Таким образом, предложенное устройство обладает значительно повышенным быстродействием. 45

Формула изобретения

Дискриминатор нулевых биений, содержащий два квадратурных канала, в каждом из которых включены последовательно фазовый детектор, фильтр нижних частот, ключ, на другой вход которого поданы тактовые импульсы, блок памяти, дифференцирующая цепь и коммутатор, другой вход которого через фазоинвертор подключен к выходу дифференцирующей цепи, а управляющий вход — к выходу блока определения знака сигнала, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия, в каждом из квадратурных каналов дифференцирующая цепь выполнена в виде последовательно соединенных линии задержки и вычитателя,второй вход которого соединен с входом линии задержки, вход блока определения знака сигнала соединен с выходом вычитателя, в каждый из квадратурных каналов включены блок определения знака суммы, входы которого подключены к входу и выходу линии задержки, и элемент равнозначность, первый вход которого соединен с выходом блока определения знака сигнала, а к второму входу подключен выход блока определения знака суммы другого квадратурного канала, к выходам коммутаторов подключены параллельно соединенные по входам, общие для обоих квадратурных каналов элемент сравнения и дополнительный коммутатор,к выходам элементов равнозначность подключены один непосредственно, а другой через дополнительный фазоинвертор, соответствующие входы второго дополнительного коммутатора, при этом управляющие входы дополнительных коммутаторов подсоединены к выходу элемента сравнения, а выходы являются выходами дискриминатора нулевых биений.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 490263, кл. Н 03 К 5/18, 1974.

651447

Составитель Л.Каграманова

Редактор Л.Гельфман Текред 3. Фанта Корректор И™Уска

Заказ 865/62 Тираж 1059 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35с Рауаскаяя наб cä 4 5 «

46фй@ ЙГФЖ@с эйли» .- ..;ь:.й: ь .ымз вюа и айа м, Филиал ППП Патент, г. Ужгород, ул. Проектная, 4