Симметричный тиросторный элемент памяти

Иллюстрации

Показать всеРеферат

(F116526 I 3 бойз Йоветских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву 381098 (22) Заявлено 23.11.76 (21) 2422871/18-24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано 15.03.79. Бюллетень № 10 (51) М, Кл.

G 11С 11/34

Государственный комитет

СССР (53) УДК 621.327 (088.8) по делам изобретений

-и открытий (45) Дата опубликования описания 15.03.79 (72) Автор изобретения

В. Н. Синеокий (71) Заявитель (54) СИММЕТРИЧНЫЙ ТИРИСТОРНЫЙ ЭЛЕМЕНТ ПАМЯТИ

Изобретение относится к интегральным запоминающим устройствам (ЗУ) и является усовершенствованием известного элемента памяти, описанного в основном авт. св. № 381098.

Известен элемент памяти; выполненный в виде симметричного триггера на двухэмиттерных тиристорах, п- и р-базы которых перекрестно соединены, аноды связаны с адресной шиной, внешние по топологии эмиттеры подключены к информационным шинам, а внутренние — соединены и через резистор подключены к цепи хранения.

Описанный элемент памяти занимает малую площадь в интегральном исполнении, однако выполнение двух эмиттеров в одной базовой р-области тиристора приводит к необоснованным потерям быстродействия при снижении потребляемой мощности и сохранении помехоустойчивости.

Целью изобретения является повышение быстродействия и уменьшения потребляемой мощности.

Поставленная цель достигается тем, что симметричный тиристорный элемент памяти содержит элементы связи, а базовые области р-типа каждого тиристора выполнены в виде двух полуобластей, одна из которых подключена через первый элемент связи к базовой области и-типа, через второй элемент связи — к адресной шине. Элементы связи могут быть выполнены на диодах, а первые элементы связи могут быть выполнены на резисторах.

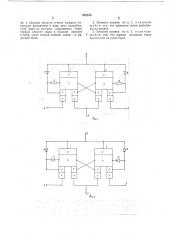

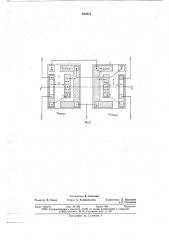

На фиг. 1 изображена электрическая схема предлагаемого элемента памяти, в которой первые элементы связи выполнены на резисторах; на фиг. 2 — та же схема с диодами в качестве элементов связи; на

10 фиг. 3 — топологическая схема элемента памяти.

Предлагаемый элемент памяти содержит тиристоры 1 и 2, эмиттеры каждого из которых выполнены в отдельных базовых

15 областях р-типа, Внутренние эмиттеры соединены между собой и подключены к цепи хранения 3. Внешние эмиттеры тиристоров

1 и 2 подключены соответственно к информационным шинам записи и считывания

20 4, 5.

Одна из р-областей каждого тиристора, в которой выполнен внешний эмиттер, связана с адресной шиной 6 через элементы связи, выполненные на диодах 7, 8, катоды

25 которых подключены к внешним р-базам, а аноды — к адресной шине 6.

Топология тиристоров 1 и 2 выполнена таким образом, что ббльшая часть периметра анода сближена с р-базой, в которой

З0 выполнен внутренний эмиттер, при этоМ

652613

65 расстояние а между этими областями меньше, чем расстояние б между остальной частью периметра анода и внешней р-базой.

В качестве первых элементов связи, обеспечивающих запись информации и одновременное ограничение насыщения внешних составляющих и — p — и-транзисторов, могут быть использованы резисторы 9 и 10, включенные между внешними р-базами тиристоров 1, 2 и и-базами тиристоров, либо диоды 11 и 12 (фиг. 2), катоды которых подключены к п-базам, а аноды — к внешним р-базам тиристоров 1 и 2.

Предлагаемый элемент памяти работает следующим образом.

В режиме хранения один из тиристоров

1 или 2, предположим тиристор 1, находится в проводящем состоянии, обеспечивая устойчивое закрытое состояние другого тиристора 2. Ток хранения при этом может быть доведен до единиц наноампер повышением уровня п р — n — р-составляющего тиристор 1 р — n — р-транзистора, в базе которого выполнен эмиттер хранения.

В силу того, что в предлагаемой ячейке эмиттеры двухэмиттерных тиристоров 1 и

2 выполнены в раздельных р-базах, минимальный ток хранения без снижения быстродействия может быть реализован за счет топологического исполнения схемы согласно фиг. 3.

Благодаря тому, что ббльшая часть периметра анода тиристора 1 (аналогично выполнен и тиристор 2) сближена с внутренней р-базой и расстояние а между этими областями меньше, чем расстояние б между остальной частью периметра анода и внешней р-базой, достигается низкий уровень а р — n — р-составляющего тиристор 1 р — и — р-транзистора с внешней р-базой при высоком уровне а р — n — р-составляющего тиристор 1 и — р — и-транзистора с внутренней р-базой.

Это обеспечивает ограничение насыщения внешних составляющих тиристор 1 и — р — n-транзисторов, ослабляет связь между информационными шинами 4, 5 и шиной хранения 3, т. е. обеспечивает устойчивое хранение информации при повышении быстродействия и уменьшении потребляемой мощности.

Полностью исключить статическую связь между эмиттерами элемента памяти при хранении информации позволяет использование в ячейке памяти без необходимости выполнения топологии ячейки согласно фиг. 3 резисторов 9, 10 или диодов 11, 12, шунтирующих центральный переход тиристоров 1, 2 со стороны внешней р-базы.

Тем самым достигается возможность исчользования тока хранения с максимальным эффектом, обеспечивающим рост устойчивости информации.

При записи информации в элемент памяти потенциал на одной из информацион5

55 ных шин 4 или 5, в данном случае при b1крывании тиристоров 2 на шине 5, понижается. В то же время на другой шине 4 потенциал достигает величины, обеспечивающей отсутствие тока через открытое ранее плечо тиристора 1.

При этом через диод 8 или резистор 1О (фиг, 1) и перекрестную связь задается ток с адресной шины 6 во внешнюю р-базу тиристора 2 закрытого ранее плеча. Это обеспечивает вывод из насыщения и закрывание связанных с цепью хранения 3 составляющих р — и — р и и — p — и-транзисторов открытого ранее тиристора 1, и устойчивое состояние элемента памяти, соответствующее новой информации, Быстродействие элемента памяти по записи обеспечивается ограничением величины заряда неосновных носителей во внешних р-базах и и-базах тиристоров 1 и

2. Это достигается ограничением уровня а р — n — р-составляющего р — и — р-транзистора с внешней базой, включением резисторов 9, 10 или диодов 11, 12 между и-базами и внешними р-базами тиристоров

1, 2.

При считывании новой информации (открыт тиристор 2) ток с адресной шины 6 проходит через внешнюю и внутреннюю р-базы открытого тиристора 2 соответственно в информационную шину 5 и цепь хранения 3, обеспечивая блокирование анодного р — и-перехода закрытого тиристора 1 и, таким образом, неразрушение информации. При этом заряд в базах открытого плеча тиристора 2 накапливается на уровне, близком к границе насыщения, что не снижает быстродействия элемента при записи.

Поэтому в предлагаемом элементе памяти вопросы роста быстродействия наряду со снижением потребляемой в режиме хранения мощности могут решаться независимо, определяясь в каждом конкретном случае характеристиками ИС ОЗУ, в которой элемент памяти применяется.

Предлагаемый элемент памяти в интегральном исполнении не требует дополнительной площади по сравнению с известным элементом, так как предусмотренные предлагаемой схемой элементы обеспечения записи и ограничения насыщения внешних составляющих и — р — n-транзисторов, в частности диоды и резисторы, могут быть выполнены топологически в р-аноде, п-базе, р-базах тиристоров.

Формула изобретения

1. Симметричный тиристорный элемент памяти по авт. св. Ме 381098, отлич аюшийся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, он содержит элементы свя6826И зи, а базовые области р-типа каждого тиристора выполнены в виде двух полуобластей, одна из которых подключена через первый элемент связи к базовой области п-типа, через второй элемент связи — к адресной шине.

2, Элемент памяти по п. i, отличан)шийся тем, что элементы связи выполнены на диодах.

3. Элемент памяти по п. 1, отлич аюшийся тем, что первые элементы связи выпо IHcHbI на резисторах, 652613

Составитель В. Синеокий

Техред А. Камышникова

Редактор Н. Коган

Заказ 1033/19 Изд. № 368 Тираж 680 Подписное

НПО Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, р

Риг.,у

Корректоры: Л. Брахнина и А. Степанова