Устройство для обращения к блокам оперативной памяти

Иллюстрации

Показать всеРеферат

< 652615

Сева Соеетсее

Соцееалмстммесим» реснублмк (6!) Дополнительное к авт. саид-ву (22) Заявлено23.06.76 (21) 2375715/18-24 с присоединением заявки №

2 (51) М. Кл.

G 11 С 17/00

Геаудвратвеавй юапет

ССС0 ае девам «зебрие«««

«вткрит«« (23) Приоритет

Опубликовано15.03.79.Бюллетень №10

Дата опубликования описания 19,03.79 (53) УДК 628,327..6(088.8) М. В. Тяпкин, В. С. Новизенцев, Б. H. Cyxux и О. Н. Сердюкова (Щ Автори изобретен и» (ТВ) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ К БЛОКАМ

ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к вычислительной технике и мажет быть использовано нри организации обращения процессора к блокам оперативной памяти.

В современных многопроцессовых вы числительных системах используется оперативная память большого объема, со» стоящая из отделыых блоков. Как правило, длительность работы памяти намного превышает длительность рабочего такта процессоров. В связи с этим в системах используется предварительная выборка операндов и команд из нескольких блоков оперативной памяти одновременно, Известна организация обращения к опе ративной памяти, где предварительный запуск нескольких блоков памяти осуществляется, если адреса обращений относятся к разным блокам )1j. Наиболее близким к изобретению техническим решением является устройство обращения к памяти, содержащее индивидуальные для каждого блока памяти счетчики никла и триггеры запоминания обращения к памяти (2), 2

Зто устройство характеризуется громоздкостью схемы и сильной зависимостью количества оборудования от количества блоков оперативной памяти, 11елью изобретения является повышение надежности при значительном уменьшении оборудования, В описываемом устройстве это достигается тем, что в нем счетчи« ки цикла работы памяти заменены одной последовательно соединенной линией сдвиговых регистров, в которую поступа наг номера блоков. оперативной памяти, занятых обращениями и по которой они перемещаются от ее начала к концу, при чем каждый номер блока находится в . линии сдвига время, равное времени цик» ла работы памяти. Вход линии сдвига подключен к дешифратору, выход которого устанавливает в состояние 0" cocrr ветствующий триггер свободной памяти.

Выход линии сдвига подключен к друго му дешифратору, выход которого уста» навливает упомятутый триггер свободной, намести в состояние 1".

652615

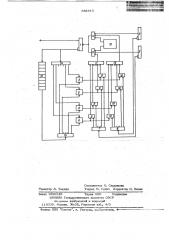

На чертеже приведена блок-схема описываемого устройства.

Оно содержит выходной регистр 1 адреса обращения к памяти, адресные регистры 2 и 3 запросов на обращение 5 к памяти, элементы И 4 и 5 подключения адресных регистров запросов к выход, ному регистру адреса обращения к памяти, триггеры G,ñâîáîäíûõ блоков памяти, дешифраторы 7 и 3 номера запрашивае- 10 мого блока памяти, двухвходовые элементы И 9 и 10, элементы ИЛИ 11 и 12 на -.й- входов, блок 13 приоритета запросов, дешифратор 14 номера блэка памяти, к которому начинается обращение, последовательно соединенные реристры сдвига 15 и дешифратор 16 номера блока памяти,. обращение к которому заканчйвается.

На адресные регистры 2 и 3 поступают адреса ячеек оперативной памяти, к которым должно быть произведено обращение. Часть разрядов каждого адреса, определяющая номер блока памяти, поступает на свой для каждого запросчика дешифратор 7 и 8 на- И -входов соответственно числу блоков памяти. Сигнал с выхода дешифратора при состоянии 1 сээгветствующего триггера 6 свободной памяти черж один из элементов И

9 и 10 и один из элементов ИЛИ 11 и"

12 разрешает одному из входов работу одного из элементов И 4 и 5, через которые в соответствии с приоритетом, определяемым блоком приоритета 13, на выходной регистр 1 поступает содержимое одного из адресных регистров

2 и 3. С выходного регистра 1 адрес обращения направляется в соответствующий блок оперативной памяти, а часть разрядов, определяющая номер блока памяти, поступает на вход дешифратэра 1 4, выход которого устанавли . вает в состояние "0 соответствующий триггер 6 свободной памяти. Кроме тс

ro, номер блока памяти с выхода регистра 1 поступает в последовательно соеди-. ненные регистры сдвига 15, а с выхода этой сдвиговой цепочки номер блэка памяти поступает на дешифратор 16, вы50 ход которого устанавливает в сэстэяцйе

1" соответствующий триггер свободной памяти.

Общее количество разрядов последовательно соединенных регистров сдвига подсчитывается пэ формуле

N=K (6о 2"+4), Т причем К= 2 — -1, где

+вр. и - количество разрядов регистров сдвига;

1 - длительность цикла оперативной памяти минимальнэе время, через которое может поступить новый запрос на регистр 1; р- число блоков оперативной памяти.

Ф ормула изобретения

Устройство для обращения к блокам оперативной памяти, содержащее адресные регистры, одни из выходов которых подключены ко входам первого и второго дешифраторов, выходы которых подключены к первым входам первых элементов И, вторые входы которых подключены к выходам триггеров, а выходы элементов И подключены ко входам элементов

ИЛИ, выходы которых подключены к первым входам вторых элементов И, вторые входы которых подключены к выходам блока приоритета, третьи входы вторых элементов И подключены к другим выходам адресных регистров, выходы вторых элементов И подключены ко входам выходного регистра, с дни выходы которого подключены ко входам третьего дешифратора, выходы которого подключены ко входам установки в 0 триггеров, отличающееся тем,что,с целью повыше щя надежности устройства, оно содержит четвертый дешифратор и последовательно соединенные регистры сдвига, входы которых подключены ко входам третьего дешифратора, а выходы — ко входам четвертого дешифратэра, выходы которого подключены ко входам установки в "1" соответствующих триггеров.

Источники информации, принятые во внимание при экспертизе

1. Катцан Г. Вьгчислительные машины системы 370. М., "Мир", 1974, с.246-248.

2. ЭВМ БЭСМ-6, ИЫ1. 700.000

ТО2, т.! И.

65261 5

Составитель О. Сердюкова

Техред М. Сенич Корректор О. Билак

Редактор Л. Тюрина

Заказ 1069/49 Тираж 680 Подписное

11НИИПИ Госудррственного комитета СССР по. делам изобретений и открытий

113033, Ыссквв, Ж33, Раушсквк ввб., 1/3

Филиал ППП "Патент", г. Ужгород, улвПроектная, 4 — ——