Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Соввтеммн

Социо алмстмчео(ин

Республнк (61) Дополнительное к авт. свил-ву « (22) Заявлено04.11,76 (21)2417610/18-24 с присоединением заявки №

Гаеударвтвепный камктвт

СССР аа делам кэюбрвтеннй н ютнрытнй (23) ПриоритетОпубликовано15.03.79.Бюллетень № 1

Дата опубликования описания 19,03.79 (72) Авторы изобретения .

Н. Н. Журавский и А. M. Селигей

Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляющих машин (71) Заявитель г (54) ПОСТОЯННОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к вычислитель. ! ной технике, в частности к постоянным запоминающим устройствам.

Известьы постоянные запоминающие устройства (ПЗУ), одно из которых содержит дешифратор адреса, накопитель, регистр числа, выполненный на триггерах, подключенных к выходам накопителя, и шину сброса триггеров. С целью упро щения, повышения надежности работы и быстродействия в накопителях известных постоянных запоминаюших устройств разряды с преобладающим количеством единиц представляют в обратном коде «1 .

Наиболее близким к изобретению техни ческим решением является ПЗУ, содержшцее первый дешифратор адреса, выхо- ды которого соединены со входами накопителя, выходы накопителя через эле менты НЕ подсоединены к первыМ входам первых элементов И, ко вторым входам которых подключены выходы соответствующих первых элементов ИЛИ, выходы первых элементов И соединены с первыми входами соответствующих вторыи элементов ИЛИ, выходы которых подсоединены ко входам регистра числа 321.

Однако в известных постоянных запоминающих устройствах количество элементов связи и число проводов в запоминаю ших трансформаторах может быть уменьшено не более, чем в два раза. Это не позволяет производить дальнейшее упрощение накопителя, повышение надежности работы и быстродействие устройств на основе метода поразрядного обратного кодирования.

Белью изобретения является повышение надежности. В предложенном устройстве это достигается тем, что оно седержит второй дешифратор адреса, вторые элементы И и третьи элементы ИЛИ по числу выходов накопителя, при этом входы второго дешифратора-адреса соединены с соответствующими входами первого дешифратора адреса, а выходысо входами первых и третьих элементов

ИЛИ, выходы третьих элементов ИЛИ

652616

Сбедииены с первыми входами соответст» вующих вторых элементов И, вте, ые вхо» ды которых подключен iso входам соответствукицих элементов HE, а выходыко вторым. входам соответствующих вгорых элементов ИЛИ.

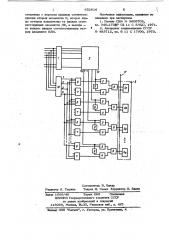

На чертеже представлена схема предложенного устройства. С@о содериит первый дешифратор адреса 1, "накайатель

2, регистр числа 3,,первые элементы

И 4, вторые элементы И 5, первые элементы ИЛИ 6, вторые элементы ИЛИ 7, чретьи элементы ИЛИ З, элементы HE 9, второй дешифратор адреса 10 н ипшу сбре са 11. 15

На чертеже приведены связи между узлами устройства для слуиая, когда ин формационный массив для хранийия в устройстве условно разделен на четыре

Равные части, например: .14 числа 1 2 3 и

Р Р Р Р

1 0 1 0 О

2 1 О О О

3 О 1

4 О О

5 1 1

6 О О

7 .1 0

8 1 1

1 О

О 0

1 выходы которого соединены со входами накопителя, выходы накопители через элементы HE подсоединены к первым . входам первых элементов И, ко вторым входам которых подключены выходы соответствующих первых элементов ИЛИ, 45 выходы первых элеменгов И соединены с первыми входами соответствуюших вторых эх.ементов ИЛИ, выходы которых подсоединены ко входам регистра числа, 50 о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит второй дешифратор адреса, вторые элементы И и третьи элементы

ИЛИ по числу выходов накопителя, при этом входы второго дешифратора адреса соединены с соответствующими входами первого дешнфратора адреса, а выходы со входами первых и третьих элементов, ИЛИ, выходы третьих элементов ИДИ

3 р

0"

О и

Р

О

0 1

1 0

2

О 1 О

О О О

О

О О 1 0

О 1 0 0

В известных устройствах применение поразрядного обратного: кодирования данного массива не дает преимуществ.

В предложенном устройстве в каждой части массива разряды с преобпадакицим количеством единиц s накопителе записаны обратным кодом:

l4 числа 1 2

Р Р

5 1 1 1 О

6 О 0 О 0

В соответствии с кодом адреса на входах первого дешифратора адреса 1. из накопителя 2 считывается код числа, например, третьего: 010...0. Входы вто рого дешнфратора адреса 10 принимают два старших разряда кода адреса. При выборе третьего числа на втором выходе второго дешифратора адреса 10 устанав ливается уровень логической 1", кото рый, поступая через соответствующие первые и третьи элементы ИЛИ 6 и 8, разрешает на входах вторых элементов

И 5 1-го и 2-ro разряда вьщачу инфор- мации из накопителя 2 прямым кодом.

Информация в 3-м и Д-м разрядах выдается обратным кодом, так как уровень логической "1 в этих разрядах поступает на первые элементы И 4, к которым выходы накопителя 2 подключены через элементы HE 9. Считанные из накопите» ля сигналы далее поступают через первые элементы ИЛИ 7 на единичные вхо ды триггеров регистра числа 3, предварительно сброшенных в 0 сигналом сброса на шине 11. В регистре числа 3 фиксируется исходный код 011 ° ..1.

Применение предложенной схемы по стоянного запоминающего устройства позволяет существенно уменьшить коли чество элементов связи в полупроводни ковых постоянных запоминающих устройствах и количество кодовых проводов в запоминающих трансформаторах постоян ных запоминающих:устройств трансформа торного типа, Упрощение накопителей повышает надежность работы устройства и его быстродействие.

Фбрмула изобретения

Постоянное запоминающее устройство, содержащее первый дешифратор адреса, 1

652616 6 соединены с первыми входами соответст Источники информации, принщые во вующих вторых элементов И, вторые вхо- внимание при экспертизе ды которых подключены ко входам соо - 1. Патент США № 3609708, ветствующих элементов НЕ, а выходы - кл. 340-173$P (G 11 С 5/02), 1971» ко вторым входам соответствующих вто- > 2. Авторское свидетельство СССР рых элементов ИЛИ. № 483712, кл, 8 11 С 17/00, 1973.

Составитель В. Вакар

Редактор Л. Тюрина Техред М. Сенич Корректор О. Билак

Заказ 1069/49 Тираж 680 Подписное

IlHHHnH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская иаб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4