Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. свил-ву(22) Заявлено 2301.76 (23) 2316771/18-21 с присоединением заявки № (23) Государственный комитет

СССР но делам изобретений и открытий

Приоритет

Опубликовано 1ьоз79,Бюллетень ¹ 10

Дата опубликования описания 1p5g7c

P2) Авторы иаобретения

С.Ф.Пушкин, В.П.Орлов и В. И.Головченко

P1) Заявитель (54) АНАЛОГО- ЦИФРОВОЙ ПРЕОБРЛЗОВАТКЛЬ

Изобретение относится к вычислительной технике.

Известен аналого-цифровой преобразователь, содержащий устройство сравнения, преобразователь кода в напряжение, регистр и логический блок 1).

Однако устройство имеет большое время преобразования. Известен аналого-цифровой преобразователь, содержащий устройство сравнения, вход которого соединен с выходом преобразователя кода в напряжение, выход соединен с первым входом блока логики, второй вход которого соединен с выходом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ и распределителя, а третий вход блока логики соединен с вторыми входами элемента

ИЛИ и распределителя (2).

Однако время преобразования устройства велико, С целью уменьшения времени .преобразования в аналого-цифровой преобразователь, содержащий устройство сравнения, преобразователь кода в напряжение, блок логики, генератор тактовых импульсов, элемент ИЛИ и распределитель, введены и основных двоично-десятичных счетчиков, и блоков управления, п коммутаторов и дополнительный двоично-десятичный счетчик, причем выход устройства сравнения соединен с первым входом блока логики, второй вход которого соединен с выходом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ и распределителя, а второй, третий и четвертый выходы блока логики соединены соответственно с входами дополнительного двоично-десятичного счетчика и входами п блоков управления, выходЫ которых соединены с соответствующими входами п основных двоично-десятичных счетчиков, их выходы соединены с первыми входами и коммутаторов, вторые входы которых соединены с выходом дополнительного двоичнодесятичного счетчика, а выходы соединены с соответствующими входами и преобра ователя .кода в напряяение, выход элемента ИЛИ соединен с входом установки в нуль дополнительного двоично-десятичного счетчика, шина яапуск соединена с вторым входом элемента ИЛИ, и с входом.652704 4 вые импульсы, в результате которых компенсирующее напряжение на выходе

10 преобразователя 2„ начинает увеличиваться от 1. 0 --U если

° (4 с шаг >м квантования,™равным 10 U„

Как только напряжение компенсации

О станет больше преобразуемого U т.е. Uq + с устройства 1 на первый управляющий вход блока б поступает сигнал Превышения, в результате которого с первого выхода блока ф). 6 на входе установки нуля счетчика

8 через элемент ИЛИ 3 поступает сигнал Установки в нуль, а.на управляющий вход распределителя 5 - сигнал, в результате которого он пере25 ходйт в очередное состояние, при этом дополнительный двоично-десятичный счетчик 8 подключается вместо очередной декады основного двоичнодесятичного счетчика 4-2, а старшая декада основного двоично-десятичного счетчика 4-1, через коммутатор 10 -1к соответствующему входу преобразователя 2.

Так как в старшей декаде счетчика

4-1 записывается число, на единицу меньше числа, которое записывается

s счетчике 8, то при подключении выхода старшей декады счетчика 4-1 через коммутатор 10-1 к соответствующему входу преобразователя 2 напря40 жение компенсации ()!, на его выходе уменьшается на величину шага квантованиЯ этой декады, РавномУ 10 Ц„м, вследствие чего компенсирующее напряжение ()к станет меньше идирдвно

45 преобразуемому U<, т.е.А„1о U„ > g„„ где Л вЂ” число, записанйое в старшей декаде основного двоично-десятичного ! счетчика 4-1. уатайовйй в- нуль основных двоично" Десятичных счетчиков, управляющие выходы распределителя соединены соответственно с управляющими вхо- дами и коммутаторов и D. блоков управления.

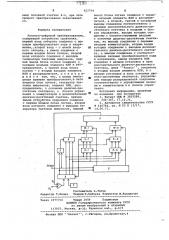

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Аналого-цифровой преобразователь содержит устройство 1 сравнения, преобразователь 2 кода в напряжение, элемент ИЛИ 3, и основных двоичнодесятичных: счетчиков 4-1 - 4-п распределитель 5, блок б логики, генератор 7 тактовых импульсов,, дополнительный двоично-десятичный счетчик 8, и блоков 9-1-9-п управления и п коммутаторов. 10- — 10-п.

Выход основных счетчиков 4-l-4-п является выходом устройства.

Преобразование напряжения U„ начийается с установки s нуль сигналом Запуск . дополнительногосчетчика 8 и основных счетчиков

4-1-4-п а распределителя 5 и блока б логики-в исходное состояние. В

= " исходйом состояйий с распределителя 5 на коммутатор 10 и на блок ,9-1 поступает сигнал, который нодклю чает дополнительный счетчик 8 вместо старшей декады основного счетчика 4 . и разрешает поступать через блок 9-1 сигналам, формируемым блоком 6, на выходы отключенного счетчика 4-1.

С приходом первого тактового импульса с генератора 7 в блок 6 на втором .выходе блока 6 формируется, сигнал установки в основном двоично-десятичном счетчике 4-1 через блок 9-1 управления числа 4 (0100), а в счетчике 8 - числа 5 (0101), в результате которого с выхода преобразователя 2 на вход устройства 1 поступает компенсирующее напряжение

Ug равное фО„, где Uq максимальное напряжение компенсации, при этом если величина компенсирующего напряжения О окажется больше преобразуемого сигнала О, т.е. +ц„ „, >0,, то с выхода устройства 1 на йервый управляюкий вход блока б поступает сигнал Превышения . 50

С приходом второго тактового им- пульса с генератора 7 в блок 6 на третьем выходе блока б формируется сигнал установки в ocBQBHQM двоично-десятичном счетчике 4-1 через блок 9-1 числа 0 (0000), а в дополнительном счетчике 8-числа 1 (0001), в результате чего на соответствующий вход преобразователя 2 через коммутатор 10-1 поступает цифровая информация числа 1, а с его выхода на второй вход устройства 1 сравнения - компенсирующее напряжение U, равное 10 (икр, прн -этом, если величина компенсирую taего напряжения станет меньше пре.1

«.1 образуемого, т.е. 10 U»< „, то с выхода устройства 1 сраь ения на первый управляющий вход блока 6 поступает сигнал Недокомпенсации, прн наличии которого .с четвертого выхода блока 6 на счетный вход основного двоично-десятичного счетчика

4-1 через блок 9-1 и на счетный вход счетчика 8 начинают поступать тактоЕсли напряжение компенсации О „ меньше преобразуемого, то с выхода устройства на первый управляющий вход блока б поступает сигнал Недокомпенсации, при котором блок б устанавливается в исходное состояние после чего начинается цикл обработки очередной декады. !

Обработка очередной и последующих декад основных счетчиков 4-2 - 4-п производится в той же последовательности, что ч обработка старшей декадыс

После обработки и-ной декады распределитель 5 отключает счетчик

8 от коммутатора 10-п, подключив к

652704

Формула изобретения х

Составитель A.Tèòoâ

Редактор Т.Янова . Техред И.Бабурка Корректор И.Ковальчук

Тираж 1059 . Подписное

ЦНИИПИ Государственного комитета СССР по дЕлам изобретений и открытнй

113035 Москва, g-35р Раушская наб,, д.4/5

Заказ 1077/54

Филиал ППП Патент, r Ужгород, ул.Проектная,4 нему основной счетчик 4-п, при этоь процесс преобразования заканчивается.

Аналого-цифровой преобразователь, содержащий устройство сравнения, первый вход коТорого соединен с выходом преобразователя кода в напряжение,1второй вход — с шиной входного сигнала, а выход соединен с первым входом блока логики, второй вход которого соединен с выходом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ .и Распределителя, а третий вход блока логики — с вторым входами элемента

ИЛИ и распределителя, о т л и ч а юшийся тем, что, с целью уменьшения времени преобразования,в него введены блок логики, генератор тактовых импульсов, элемент ИЛИ, распределитель, и основных двоично-десятичных счетчиков, и блоков управления и коммутаторов и дополнительный двоично-десятичный счетчик, причем выход устройства сравнения соединен с первым входом блока логики, второй вход которого соединен с выходом генератора тактовых импульсов, первый выход блока логики соединен с первыми входами элемента ИЛИ и распределителя, а второй, третий и четвертый выходы соединены соответственно с входами дополнительного двоично-десятичного счетчика и входами и блоков управления, выходы которых соединены с соответствующими входами и основных двоично-десятичных счетчиков, их выходы соединены с первыми входами коммутаторов, вторые входы

1О которых соединены с выходом дополнительного двоично-десятичного счетчика, а выходы соединены с соответствующими входами преобразователя кода в напряжение, выход элемента ИЛИ

18 соединен с входом установки в нуль дополнительного двоично-десятичного счетчика, шина Запуск, соединена с вторым входом элемента ИЛИ, и с входом установки в нуль основных двоо ично-десятичных счетчиков, управляющие выходй распределителя соединены соответственно с управляющими входами п коммутаторов и и блоков управления.

Источники информации, принятые во внимание при экспертизе

1. Патент США,Р 3855589, кл. 340-347, 17.12.74.

2. Авторское свидетельство СССР

Р 440784, кл . Н 03 К 13/17, 14.06,71.