Синхронизирующее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

И ЗОБРЕТЕ Н И1 .

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ

)652720

I

1 В-

« (61) Дополнительное к авт. свид-ву (22) Заявлено 15.04,77(21) 2476675/18-09 с присоединением заявки № (51) М. Кл"

Н 04 L 7/02

Государственный комитет

СССР оо делам изобретений и открытий (23) Приоритет—

»

Опубликовано05.03.79.Бюллетень Ю 10 (53) УДК 621.394.

«662 2(088»8) Дата опубликования описания 19.03.79

Е. Ф. Камнев, А, Ю. Курковский, А. П. Родимов, А. М. Чуднов и В. М. Терентьев (72) Авторы изобретения (71) Заявитель (54) СИНХРОНИЗИРУЮЩЕЕ УСТРОЙСТВО Изобретение относится к электросвязи и может быть использовано в устройствах

> предназначенных для передачи данных.

Известно синхронизируюгцее устройство, содержащее Jf каналов, каждый из которых состоит из декодера и переключателя, при этом выходы всех декодеров подключены к входам управляющего блока, выходы которого, объединенные с соответствуюшими выходами переключателей, подключены к входам элемента ИЛИ, а также блок задержки с отводами (1).

Однако известное устройство имеет недостаточную помехозашищенность и скорость синхронизации.

Целью изобретения является повышение .помехозащищенности и увеличение скорости синхронизации.

Для этого в синхронизирующем устройстве, содержа щем Я к а н алов, каждый из которых состоит из декодера и переключателя, при этом выходы всех декодеров подключены к входам управляющего блока, выходы которого, объединенные с соответствующими выходами переключателей, подключены к входам элемента ИЛИ, а также блок задержки с отводами, в каждом канале введены объединенные по входу блоки регистрации и накопители, а также дополнительный элемент ИЛИ, причем выход блока регистрации через накопитель подключен к входу переключателя, а другой выход наs капителя подключен к входу декодера, при этом выходы всех переключателей подключены к входам дополнительного элемента

ИЛИ, а выход элемента ИЛИ через блок задержки с отводами подключен к другому входу каждого блока регистрации.

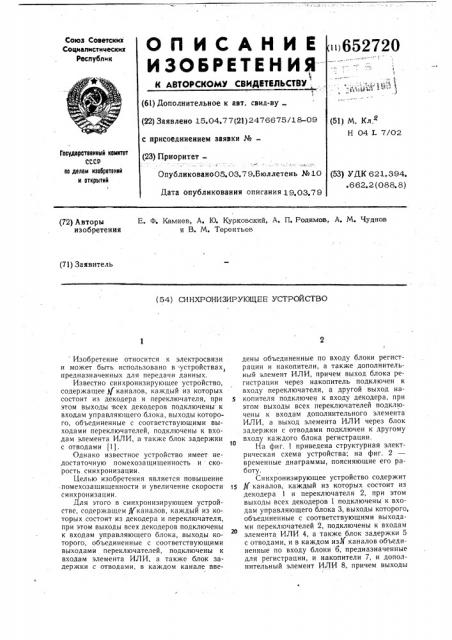

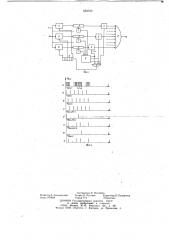

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 временные диаграммы, поясняюшие его работу.

Синхронизирующее устройство содержит

ts P каналов, каждый из которых состоит из декодера 1 и переключателя 2, при этом выходы всех декодеров 1 подключены к входам управляющего блока 3, выходы которого, объединенные с соответствующими выходами переключателей 2, подключены к входам элемента ИЛИ 4, а также блок задержки 5 с отводами, и в каждом из)/ каналов объединенные по входу блоки б, предназначенные для регистрации, и накопители 7, и дополнительный элемент ИЛИ 8, причем выходы

652720 блоков 6 через накопители 7 подключены к

Bxojl3ì псреклю гатсля 2, "а другие выходы накопителей 7 подключены к входам деко-! деров 1, при этом выходы всех переключателей 2 подключены к входам дополнительного элемента ИЛИ 8, а выход элемента ИЛИ

4 через блок задержки 5 подключен к другому входу каждого блока регистрации 6.

Устройство работает следу ощим образом.

Г1оследователы(ость (искаженная помс- 30 хами) двоичных («О» или «1») посылок, образующая кодовую комбинаци(о, соответствующую элементу сообщения, поступает одновременно на все первыс входы блоков регистрации 6 (фиг. 2а). 113 вторые входы блоков регистрации 6 поступает ш)следова15 тельность регистрирующих импульсов, причем сдвиг по времени между рсп)етрирующимн ичпульслми, поступаюн(ими ня различныс блоки 6, определяется ffpci»JcJII!I>fxl интервалом между соотвстству)ош ми оТВодами блока 5 (фиг. 2б, в, г).

В блоках 6 с ИГ)чоп<ыо рсгистрируlonlnx импульсов производится регистрация кодовой кочоиняции принимаем<и.о информационного сигнала (фиг. 2д, с, >к), которая дллес запоминлстся в нлкопитслях 7. Декодеры прсобрязуfoT принятые кодовые послсдовятсльностц к виду, удобному для принятия решения о пал яви ошноки в комби нациях, которые Опрсдсляст блок 8 н Отпирает псрскл(очлтель 2 гой линейки, где нс

30 было Обнаружсno ошибки в нрнсме информационной кодовой кочбннации (фиг. 2з). Далее сигнал правильно принятой комбинации через элемент ИЛИ 8 постуfi;icT ня III!xoq устройства, а управляющий блок 3 подает на вход блока задержки 5 импульс регистрации через элемент ИЛИ 4 производства процесса регистрации следу)ощей информяционнои кодовой последовательности.

Помехоза щи щен ность данного устройства повышена за счет анализа ошибок в приеме «зашум ICHHblx» кодовых последовательностей, принятых Я/ параллельными линейками, и выбора той из них, где не произошло ошибки при регистрации, а степень помехОза(цищен)3ости будет определяться плотностью регистрирующих импульсов на временном интервале, равному длительности элс: ментарной посылки. Гкорость фязирования (синхронизации) в дашюм устройстве определяется лишь временем подклк>чения оптимальной линейки Ii3 выход устройства, что составляет приблизительно 10<>/о От скорости СИHxронизлции в изве< пюм устройстве, так клк в ней сипгал синхрониза(ши внача ле проходит линик> задержки, затем ряд инерционных элечснтов и только после этого поступает н4 вход перс

ДОПОЛНИТСЛЬНО З(3 C ICT OTC) 1 CTIIИЯ В HI!(f)OP мационной кодовой последоватслыгс>стн специального синхросип(ллл HoBI>HH;icT() информационная скоросгь передачи, л слсдоВЛТСЛ 3>НО, ПрОП >CHII3 H CHOCO() IIOCTI>

<вязи в целом.

ФГ)/>л!(/.и цз<)Г)/7< 7<>ин»

Гlllfxponffnlfp) устройство, содержан<сс N каня "loB, к;)ждь(й JIB которы\ сОстОит из декодсрл и псрскл(очатсля, при этом Bl>ixoды всех декодеров подкл(о fcnbl к входам упрлвляюн<сго блока, выходя которого, объедиlicHHl>Ic с соотвсTcTB) >Огцимн выходами переключателей, подкл(очсны к входам элечдачи, orличГИГ)и(«r)J тсм, что, с )<елью нов Inicnnn n())i(. <х)ан<ищ< нности и увеличения скоро TH ñníxðoíèçàöèè, в каждом клнялс ввсдсны обьсдиненныс по входу блоки р< гистрлции и накопители, 3 также дополнитсльный элемент ИЛИ, причем выход блока регистрации через накопитель подключен к входу Jfcpcf<;llo÷3òåcfÿ, а другой выход накопителя подключен к входу декодера, при этом выxоды всех переключателей подклfo чсны к входам дополнительного элемента

ИЛИ, л выход элемента ИЛИ через блок задср>кки с отводами подключен к другому входу каждого блока регистрации.

Источники информации, принятые во внимание при экспертизе

1. Патент США ¹ 3851100, кл. Н 04 L 7/00, 1975.

652720

Риз. !

Риг. г

Редактор А. Зиньковский

Заказ 1078/54

Составитель E. Погиблов

Техред О. Луговая Корректор В. Куприянов

Тираж 774 Подписное

ИНИИПИ Государственного комитета СССР по делам изобретений и открьпий

1 1 3035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4